со э

со

а

Изобретение относится к вычислительной технике и может быть использовано в графических дисплеях растрового типа.

Цель изобретения - упрощение устройства.

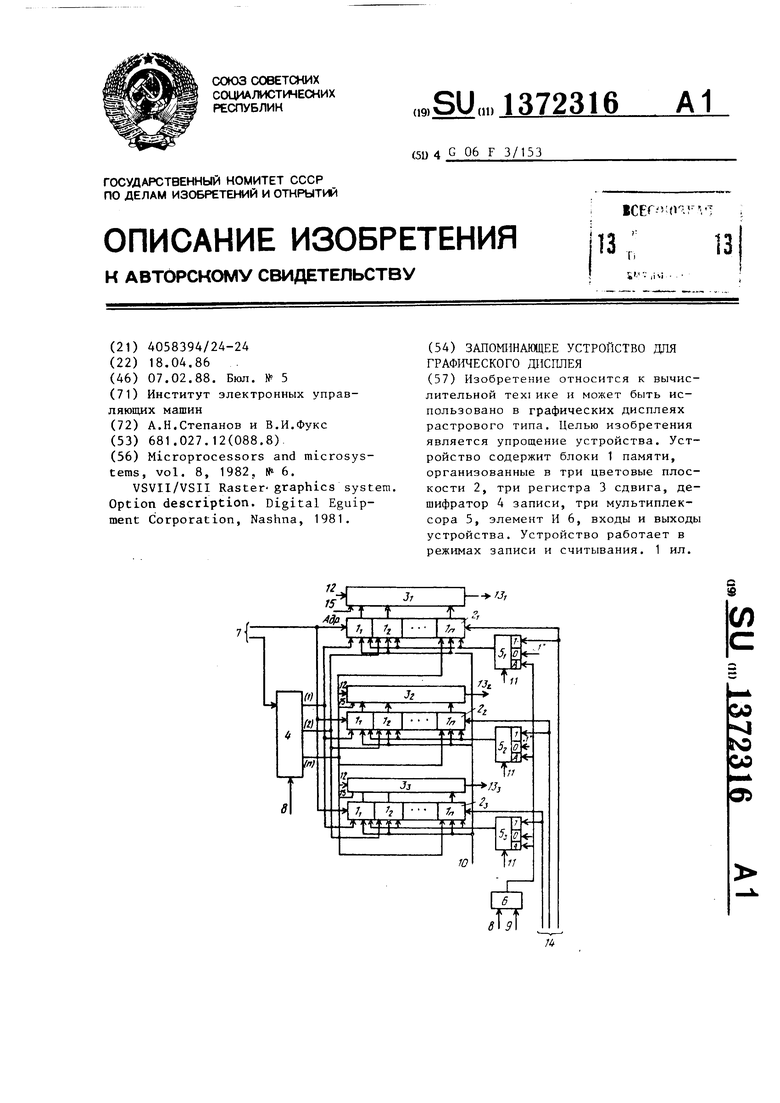

На чертеже представлена структурная схема запоминающего устройства для графического дисплея для случая трех цветовых плоскостей.

Устройство содержит блоки 1 памяти, организованные в три цветовые плоскости 2, три регистра 3 сдвига, дешифратор 4 записи, три мультиплексора 5, элемент И 6, входы 7 адреса вход 8 разрешения записи, вход 9 задания режима, входы 10 и 11 стро- бирования, тактовый вход 12, выходы 13, входы 14 данных и входы 15 записи пегистров сдвига.

Блок памяти работает следующим образом.

В режиме как записи, так и считывания на входы 7 поступают разряды адреса, причем младшие разряды, определяющие номер блока памяти в цветовых плоскостях, поступают, на входы дешифратора 4, а старшие разряды представляют собой мультиплексированный адрес ячейки в блоках памяти всех цветовых плоскостей. Прием двух половин адреса блоками памяти осуществляется по сигналам стробиро- вания адреса строки (RAS) и строби- рования адреса столбца (CAS) сдвинутом во времени, (понятия строка и столбец относятся к внутренней структуре блоков памяти и являются условным для данной структуры).

В режиме считывания сигнал разрешения записи на входе 8 имеет нулевое значение, при этом на выходе элемента И 6 будет нулевой потенциал, а на выходах дешифратора 4 - единичный, соответствующий запрету записи. Мультиплексоры 5 передают на свои выходы сигналы с нулевого входа, т.е. единичное значение. Мультиплексоры стробируются общим сигналом CAS по входу 11 и выдает индивидуальные для каждой цветовой плоскости сигналы CAS.

Информация с выходов блоков памяти цветовых плоскостей заносится в соответствующие регистры сдвига по сигналу на входе 15 и далее преобразуется в последовательный код на выходах 13. При этом происходят считьюание и передача на выход кода последовательных пикселей.

В режиме записи одновременно с сигналом RAS на входе 10 подается сигнал разрешения записи высоким уровнем на вход 8, который разрешает выдачу сигналов разрешения записи на выходах дешифратора 4. Сигнал на

вход 8 подается синхронно во времени с сигналом RAS. При этом данные с входов 14 записываются в соответствующие блоки памяти цветовых плоскостей. Если на входе 9 присутствует единичный потенциал, что соответствует режиму записи только единиц, то сигнал на входе 8 будет вызывать переключение входов мультиплексоров, при котором стробирующий сигнал будет

логически перемножаться с соответ- ствуюгдим разрядом данных. Это приведет к тому, что сигнал с выхода мультиплексора будет передан на вход стробирования адреса столбца соответствующей цветовой плоскости только если соответствующий разряд данных имеет единичное значение. В противном случае сигнал CAS не подается, запись в блоки памяти этой плоскости не производится, а информация в ячейках выбранной строки блоков памяти регенерируется. Таким образом, реализуется операция записи только единиц.

35

Формула изобретения

Запоминающее устройство для гра- нфического дисплея, содержащее блоки

памяти, регистр сдвига и дешифратор записи, информационный вход которого является адресным входом устройства, адресные входы блоков памяти являются вторым адресным входом устройства, входы данных блоков памяти являются входом данных устройства, первые тактирующие входы блоков памяти являются первым тактирующим входом устройства, выходы блоков памяти соединены с информационными входами соответствующего регистра сдвига, выходы которых являются выходом данных устройства, тактирующие входы регистров сдвига являются вторым тактирующим входом устройства, управляющие входы сдвиговых регистров являются управляющим входом устройства, управляющий вход дешифратора записи является входом раз

313723164

решения записи устройства, о т л и-мультиплексоров соединены с входом чающееся тем, что, с цельюданных устройства,- вторые входы дан- упрощения устройства, оно содержитных мультиплексоров соединены с шиной мультиплексоры и элемент И, выход логической единицы устройства, так- которого соединен с адресными входа-тирующие входы мультиплексоров явля- ми мультиплексоров, первый вход эле-ются третьим тактирующим входом уст- мента И является входом задания ре-ройства, вторые тактирутошие входы жима устройства, второй вход элемен-блоков памяти соединены с выхода- та И является входом разрешения за- )Qми соответствующих мультиплексо- писи устройства, первые входы данныхров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство формирования сигналов управления динамической памятью | 1989 |

|

SU1741141A1 |

| Динамическое оперативное запоминающее устройство | 1987 |

|

SU1499401A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для отображения графической информации на экране цветного телевизионного индикатора | 1990 |

|

SU1836719A3 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1336123A1 |

| Устройство для ввода информации | 1984 |

|

SU1201842A1 |

Изобретение относится к вычислительной тех1 ике н может быть использовано в графических дисплеях растрового типа. Целью изобретения является упрощение устройства. Устройство содержит блоки 1 памяти, организованные в три цветовые плоскости 2, три регистра 3 сдвига, дешифратор 4 записи, три мультиплексора 5, элемент И 6, входы и выходы устройства. Устройство работает в режимах записи и считывания. 1 ил.

| Microprocessors and microsystems, vol | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| VSVIl/VSII Raster- graphics system | |||

| Option description | |||

| Digital Eguip- ment Corporation, Nashna, 1981. | |||

Авторы

Даты

1988-02-07—Публикация

1986-04-18—Подача