Изобретение относится к области вычислительной техники и может быть использовано для функционального контроля полупроводниковой оперативной памяти динамического типа.

Цель изобретения - повышение быстродействия устройства.

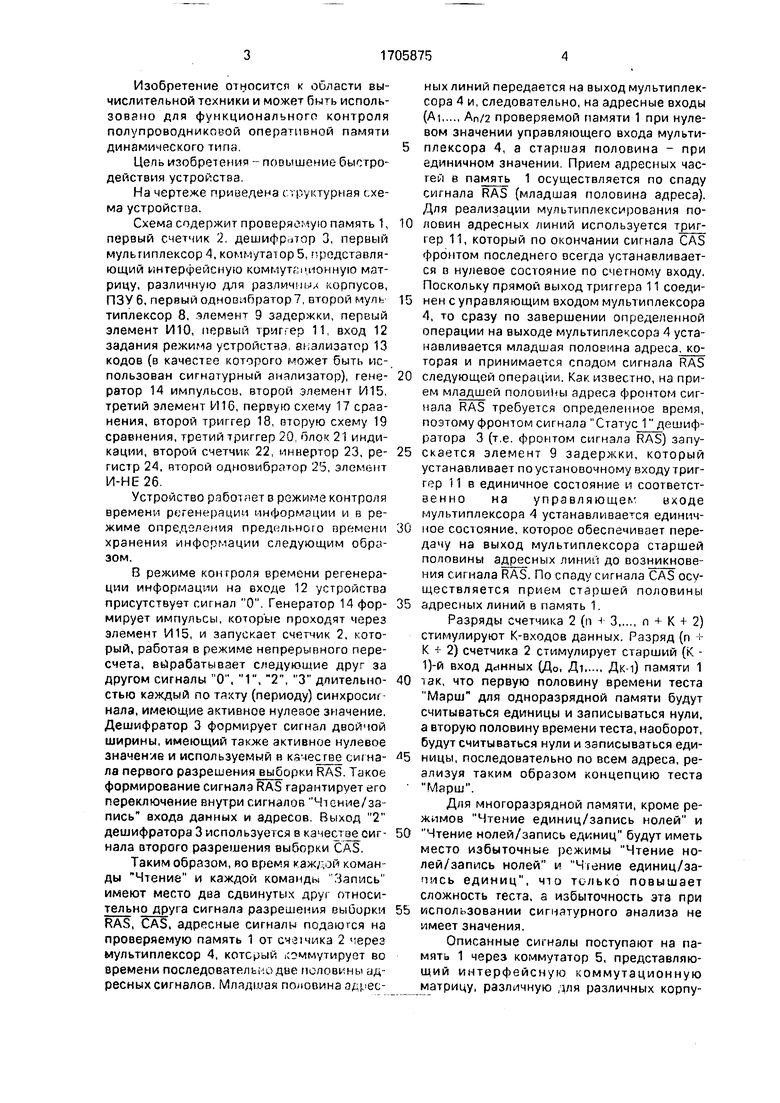

На чертеже приведена структурная схема устройства.

Схема содержит проверяемую память 1, первый счетчик 2. дешифратор 3, первый мультиплексор 4, коммутатор 5, представляющий интерфейсную коммутационную матрицу, различную для различных корпусов, ПЗУ 6, первый одновибратор7, второй мультиплексор 8, элемент 9 задержки, первый элемент И10, первый триггер 11, вход 12 задания режима устройства, анализатор 13 кодов (в качестве которого может быть использован сигнатурный анализатор), генератор 14 импульсов, второй элемент И15, третий элемент И16, первую схему 17 сравнения, второй триггер 18, вторую схему 19 сравнения, третий триггер 20, блок 21 индикации, второй счетчик 22, инвертор 23, регистр 24, второй одновибратор 25, элемент И-НЕ 26.

Устройство работает в режиме контроля времени регенерации информации и в режиме определения предельного времени хранения информации следующим обрг)- зом.

В режиме контроля времени регенерации информации на входе 12 устройства присутствует сигнал О. Генератор 14 формирует импульсы, которые проходят через элемент И15, и запускает счетчик 2, который, работая в режиме непрерывного пересчета, вырабатывает следующие друг за другом сигналы О, 1, 2, 3 длительностью каждый по тахту (периоду) синхросиг нала, имеющие активное нулевое значение. Дешифратор 3 формирует сигнал двоимой ширины, имеющий также активное нулевое значение и используемый в качестве сигнала первого разрешения выборки RAS. Такое формирование сигнала RAS гарантирует его переключение внутри сигналов Чтение/запись входа данных и адресов. Выход 2 дешифратора 3 используется в качестве сиг- нала второго разрешения выборки CAS.

Таким образом, во время каждой команды Чтение и каждой команды Запись имеют место два сдвинутых друг относи- тельно друга сигнала разрешения выборки RAS, CAS, адресные сигналы подаются на проверяемую память 1 от 2 через мультиплексор 4, который коммутирует во времени последовательно две половины адресных сигналов. Младшая половина адресных линий передается на выход мультиплексора 4 и, следовательно, на адресные входы (Ai,..., An/2 проверяемой памяти 1 при нулевом значении управляющего входа мультиплексора 4, а старшая половина - при единичном значении, Прием адресных частей в память 1 осуществляется по спаду сигнала RAS (младшая половина адреса). Для реализации мультиплексирования по0 ловин адресных линий используется триг- гер 11, который по окончании сигнала CAS Фронтом последнего всегда устанавливается в нулевое состояние по счетному входу. Поскольку прямой выход триггера 11 соеди5 нен с управляющим входом мультиплексора 4, то сразу по завершении определенной операции на выходе мультиплексора 4 устанавливается младшая полоеина адреса, ко- торая и принимается спадом сигнала RAS

0 следующей операции. Как известно, на прием младшей половины адреса фронтом сигнала RAS требуется определенное время, поэтому фронтом сигнала Статус 1 дешиф- ратора 3 (т.е. фронтом сигнала RAS) запу5 скается элемент 9 задержки, который устанавливает по установочному входу триггер 11 в единичное состояние и соответст- венно на управляющее входе мультиплексора 4 устанавливается единич0 мое состояние, которое обеспечивает передачу на выход мультиплексора старшей половины адресных линий до возникнове- ния сигнала RAS. По спаду сигнала CAS осуществляется прием старшей половины

5 адресных линий в память 1.

Разряды счетчика 2 (п + 3,..., п + К + 2) стимулируют К-входов данных. Разряд (п + К 4- 2) счетчика 2 стимулирует старший (К - 1)-й вход дннных (До, Дт,..., Дк-0 памяти 1

0 так, что первую половину времени теста Марш для одноразрядной памяти будут считываться единицы и записываться нули, а вторую половину времени теста, наоборот, будут считываться нули и записываться еди5 ницы, последовательно по всем адреса, реализуя таким образом концепцию теста Марш.

Для многоразрядной памяти, кроме режимов Чтение единиц/запись нолей и

0 Чтение нолей/запись единиц будут иметь место избыточные режимы Чтение нолей/запись нолей и Чтение единиц/запись единиц, что только повышает сложность теста, а избыточность эта при

5 использовании сигнатурного анализа не имеет значения.

Описанные сигналы поступают на память 1 через коммутатор 5, представляющий интерфейсную коммутационную матрицу, различную для различных корпусов. Выходы тестируемой БИС ОЗУ 1 подаются на информационные входы, используемого в качестве регистратора выходных реакций анализатора 13 кодов, представляющего собой типовой сигнатурный анализа- тор. На его второй управляющий вход Сдвиг1 (синхровход) поступают импульсы синхрснизации с генератора 14 черет элемент И15.

Так как при проверке БИС ОЗУ тестом Марш происходит последовательный непрерывный перебор всех адресов, то для осуществления контроля времени регенерации достаточно по окончании теста Марш организовать задержку тз и осуществить по- вторную проверку данной БИС ОЗУ указанным тестом.

В момент окончания первого теста Марш (перепад с единичного в нулевое состояние (п + К + 2)-го разряда счетчика 2) одновибратор 7 формирует короткий сигнал с активным нулевым уровнем, который поступает на управляющий на вход схемы 17 сравнения и обеспечивает сравнение в последней кодов истиной (присутствует на вы- ходах анализатора 13 кодов) и эталонной (хранится в регистре 24) сигнатур. В случае их совпадения (исправны вся ячейки тестируемой БИС ОЗУ и значит необходим контроль времени регенерации, т.е. задание паузы длительностью т,з перед повторным тестированием тестом Марш) на выходе схемы сравнения 17 по-прежнему остается уровень 1.

Передним фронтом сигнала с выхода одновибратора 7 триггер 18 устанавливается в единичное состояние (исходное состоя ние - нулевое), тем самым обеспечивается прохождение сигналов генератора 14 через элемент И16 ка счетный вход счетчика 22 (исходное состояние нулевое) и блокируется проходжение сигналов генератора 14 через элемент И15 на счетный вход счетчика 2 и на второй управляющий вход Сдвиг анализатора 13 кодов.

Кроме того, сигнал (сигнал окончания теста Марш) с выхода одновибратора 7, поступая на первый управляющий вход Стоп анализатора 13 кодов (действующий задний фронт), заканчивает измерительный период (окно), в течение которого производится ввод данных в сигнатурный анализатор.

В момент окончания первого теста Марш (п + К + 3)-й разряд счетчика 2 уста- навливается в состояние 1, а остальные старшие разряды (п + К + 1 + 3,,.., п + К + m + 2) остаются в состоянии О. При такой кодовой комбинации на адресных входах (Ai,...,Am) ПЗУ 6 ( в режиме контроля времени регенерации адресный вход Атн постоянно находится в состоянии О) на его выходах устанавливается двоичная кодовая комбинация, значение которой зависит от предварительного выбора рабочей частоты генератора 14, чем выше частота генератора, тем сто оно больше.

Сигналы генератора 14, поступая на счетчик 22, обеспечивают работу последнего в режиме непрерывного пересчета с нуля до числа, двоичный код которого установлен на выходах ПЗУ 6 (время этого пересчета и является длительностью задержки t;y,

Состояние 1 на управляющем входе схемы 19 сравнения обеспечивает сравнение кода на выходах ПЗУ 6 с кодом ня выходах счетчика 22. В момент их совпадения (конец паузы между циклами контроля) на выходе схемы 19 сравнения появпяегся сш- нэл с активным единичным уровнем, который поступает на управляющий вход Старт анализатора 13 кодов (действующий передний фронт) и, устанавливая сигнатурный анализатор в исходное (как правило нулевое, подготавливает его к очередному измерительному периоду (повторное тестирование тестом Марш).

Сигнал с выхода 19 срззнения, поступая на вход установки в но/ть смотчика 22, устанавлизает его в негодна, ;.yie;oe состояние. Услано пкз триггера 1 ь нулрэие состояние (по счетному ососпечива- ется задним фронтом порог- :i .. уровня J в уровень 1 инвер;и;: ср,ш,:..чс п пмвррто- рс 23 сигнала с выхо/;.. оеми 19 сравнения, i риггер 18 при этом &;- .фу.гт то- ;уп .гкие сигналов генератора 1 ; через элемент И16 и разрешает поступление последних через элемент И15.

Повторная проверка ксмтроли;;-урмой БИС ОЗУ тестем Марш огущестил лтся указанным образом.

Заметим, что в момент окончания повторной проверки тестом Марш на (п н К + 3)-ем разряде счетчика 2 имеет место перепад с уровня 1 в уровень О, по которому одновибратор 25 формирует импульс с активным нулевым уровнем (уровень О на управляющем входе мультиплексора 8 в этом режиме обеспечивает переключение (п + К + 3)-го разряда счетчика 2). Поступление этого сигнала на вход элемента И-НЕ 26 обуславливает появление на выходе последнего перепада с уровня О в уровень 1, по которому триггер 20 устанавливается в нулевое состояние (исходное-единичное со- стоянуе) ввиду наличия на его информационном входе уровня О.

Сигнал О с единичного выхода триггера 20 (сигнал Конец работы) блокирует

дальнейшее прохождение сигналов генератора 14 через элементы И15 и 16. Кроме того, появление уровня О на адресном входе Ат-2 ПЗУ 6 (на входе AI - уровень О на входе Л2 1, а на остальных входах уровни О обеспечивает появление на выходах последнего кода, соответствующего величине задержки между тестами в удобном для индикации виде.

По сигналу О с выхода триггера 20 на управляющем входе блока 21 индикации индицируется код истинной сигнатуры, поступающий з последний с вых.одоп анализатора 13 кодов, и величина временного интервала между тестами (с выходоо ПЗУ 6).

Отметим, что если по окончанию первого тестэ Марш в схеме 17 сравнения обнаружено несовпадение истиной и эталонной сигнатуры (неисправна память и дальней- ший ее контроль по времени регенерации не имеет смысла), то на выходе последней появляется сигнал (активный нулевой уровень), который также обеспечивает переброс триггера 20 в нулевое состояние(конец работы после первого прохода теста Марш). При этом на выходах ПЗУ 6 имеет место код, соответствующий значению интервала времени (паузы) равному нулю (на адресном входе At - уровень 1, а на всех остальных адресных входах ПЗУ 6 - уровень О,

В режиме определения предельного времени хранения информации устройство работает аналогично, однако по окончании повторной проверки тестом Марш контролируемой памяти в случае необнаружения в ней ошибок (т.е. при отсутствии несовпадения истинной и эталонной сигнатур в схеме

17 сравнения) процесс контроля не закэнчи- вается. Так как в этом режиме ввиду присутствия уровня 1 на входе 12 устройства через мультиплексор 8 коммутируется (п 3- К + гп + 2)-й разряд счетчика 2. Разряд (п + К т 3)-й счетчика 2 (после повторного теста Марш) будет находится в состоянии О, разряд п + (К + 1) + 3 установится в состояние 1, а остальные разряды гн-(К - 2)+ 3,..., п + (К + т) + 2 по-прежнему - в состоянии О.

При этой комбинации на адресных входах Ai,,.,, Am ПЗУ G (с учетом того, что на входах Ат+1 и Ат+2 имеют место уровни 1) на выходах ПЗУ появится двоичнап кодовая комбинация, соответствующая большему времени задержки.

Счетчик 22 аналогичным образом за- лолняется от нумя до равенства с новой кодовой комбинацией на выходах ПЗУ 6. По сигналу с выхода схемы сравнения 19 (в

момент совпадения комбинаций на выходах счетчика 22 и ПЗУ 6) начинается очередной цикл проверки БИС ОЗУ тестом Марш и, если в результате контроля ошибок в контролируемой БИС ОЗУ вновь не обнаружится, то подобная процедура повторяется с последовательным наращиванием временного интервала между очередными циклами проверки, вплоть до обнаружения ошибки в контролируемой БИС ОЗУ 1, что и определяет время предельного хранения информации в динамических БИС ОЗУ,

Количество нарастающих временных интервалов между циклами проверки - N 2т - 1, где m - число адресных входов ПЗУ 6, соответственно соединенных с (п + К + 3,..., п + (К + т) + 2) - разрядами счетчика 2 (m зависит от требуемой точности определения времени хранения информации).

Если же (при определенном выборе т) ошибок в БИС ОЗУ не обнаружится, то устройство останавливает дальнейший контроль в момент перепада с уровня 1 в уровень О (п + К + m + 2)-го разряда счетчика 2 аналогично.

Формула изобретения

Устройство для контроля оперативной памяти, содержащее генератор импульсов, первый счетчик, дешифратор, первый мультиплексор, коммутатор, анализатор кодов, первый, второй и третий триггеры, элемент задержки, первый, второй и третий элементы И, выходы первого мультиплексора являются адресными выходами устройства, информационные входы первой и второй групп которого соединены соответственно с выходами первой и второй групп первого счетчика, управляющий вход первого мультиплексора соединен с прямым выходом первого триггера вход установки в 1 которого соединен с выходом элемента задержки, дешифратора соединены с первым и вторым выхопами первого счетчика перьый выход дешифратора - с первым входом первого элемента И и с входом элемента задержки, второй выход дешифратора - с входом синхронизации первого триггера и с вторым входом - первого элемента И, выход которого является выходом выборки строки устройства, второй выход дешифратора - выходом выборки столбца устройства, третий выход первого счетчика - выходом записи чтения устройства, выходы третьей группы первого счетчика -- информационными, выходами устройства, входы анализатора кодой - информационными входами устройств-., второй управляющий

зход анализатора кодов соединен с выходом второго элемента И и с входом синхро- низации первого счетчика, выход генератора импульсов - с перпыми входами второго и третьего элементов И, второй вход второго элемента И - с инверсным выходом второго триггера, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй счетчик, первая и вторая схема сравнения, второй мультиплексор, первый и второй одновиб- рэгоры, элемент И-Ht, регистр, инвертор и блок постоянной памяти, адресные входы группы которого соединены с выходами четвертой группы первого счетчика, управляю- щий вход второго мультиплексора - с адресным входом блока постоянной памяти и является входом задания режима устройства, первый и второй информационные входы второго мультиплексора - с выходами младшего и старшего разрядов четвертой группы первого счетчика, выход старшего разряда третьей группы первого счетчика соединен с входом первого одновибрэтора, выход которого соединен с входом установ- ки в единичное состояние второго триггера, с входом синхронизации первой схемы срапнения и с первым управляющим входом анализатора кодоп, выходы которого соединены с входами второй группы первой схе-

мы сравнения и являются выходами индикации первой группы устройства, выходы блока постоянной памяти соединены с входами первой группы второй схемы сравнения и являются выходами индикации второй группы устройства, входы второй группы второй схемы сравнения соединены с выходами второго счетчика, вход синхронизации которого соединен с выходом третьего элемента И, второй вход которого соединен с прямым выходом второго триггера и с входом синхронизации второй схемы сравнения, выход которой соединен с входом установки в О второго счетчика, с третьим управляющим входом анализатора кодов и с входом инвертора, выход которого соединен с входом синхронизации второго триггера, выход второго мультиплексора соединен с входом второго одновибратора, выход которого соединен с первым входом элемента И-НЕ, второй вход которого соединен с выходом первой схемы сравнения, выход элемента И-НЕ соединен с выходом синхронизации третьего триггера, единичный выход которого соединен с третьими входами второго и третьего элементов И, с адресным входом старшего разряда блока постоянной памяти и является выходом синхронизации результата контроля, выходы регистра соединены с входами первой группы сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1413676A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1325571A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля блоков оперативной памяти | 1990 |

|

SU1751821A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля оперативной памяти тестом Марш с двоично-нарастающим адресным шагом | 1986 |

|

SU1532978A1 |

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля полупроводниковой оперативной памяти динамического типа. Цель изобретения - повышение быстродействия. Устройство содержит память 1, первый счетчик 2, дешифратор 3, постоянное запоминающее устройство 6, первый одновибратор 7, второй мультиплексор 8, элемент 9 задержки, первый элемент И10, первый триггер 11, вход 12 задания режима, анализатор 13 кодов, генератор 14 импульсов, второй и третий элементы И15, первую схему 17 сравнения, второй триггер 18, вторую схему 19 сравнения, третий триггер 20, блок 21 индикации 21, второй счетчик 22, инвертор 23, регистр 24, второй одновибратор 25, элемент И-НЕ 26. В устройстве обеспечивается уменьшение времени контроля корпуса ОЗУ (режим контроля времени регенерации информации). 1 ил. со с VJ О СЛ 00 VI СЛ

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-01-15—Публикация

1989-11-13—Подача