13

рядов которого подключены к входам дешифратора 3 и используются для фрр- мирования управляющих сигналов на выходах 19 и 20 дешифратора 3. Сигнал с-выхода 2b является сигналом сопровождения адреса (младшей части), Сиг- .нал сопровождения старшей части адреса формируется из сигналов с выходов 19 и 20 на выходе 21 элемента И 4. Мультиплексор 5 на своих выходах 11 формирует адресные коды, старшую и младшие части в зависимости от сигнала на выход триггера 6, управляемого сигналами с выходов 19 и 20. Данные на выходах 25 устройства получаются путем передачи кодов с выходов 23

1

Изобретение относится к автомати- .ке и вычислительной технике и может быть использовано для функционального контроля как отдельных корпусов микросхем оперативных запоминающих -устройств (ОЗУ) с мультиплексируемыми и немультиплексируемыми адресньН ми входами, т.е. ОЗУ соответственно динамического и статического типа, так и построенных на их основе блоков ОЗУ произвольной емкости и организации.

Цель изобретения - повьшение точности контроля устройства.

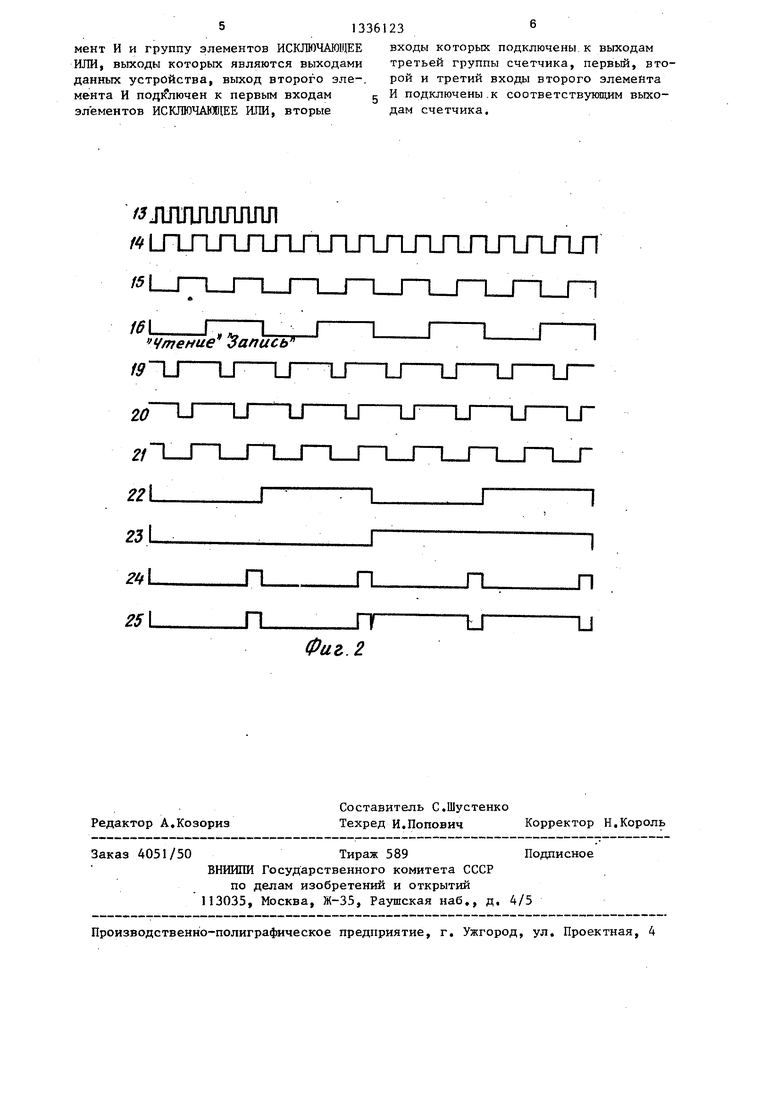

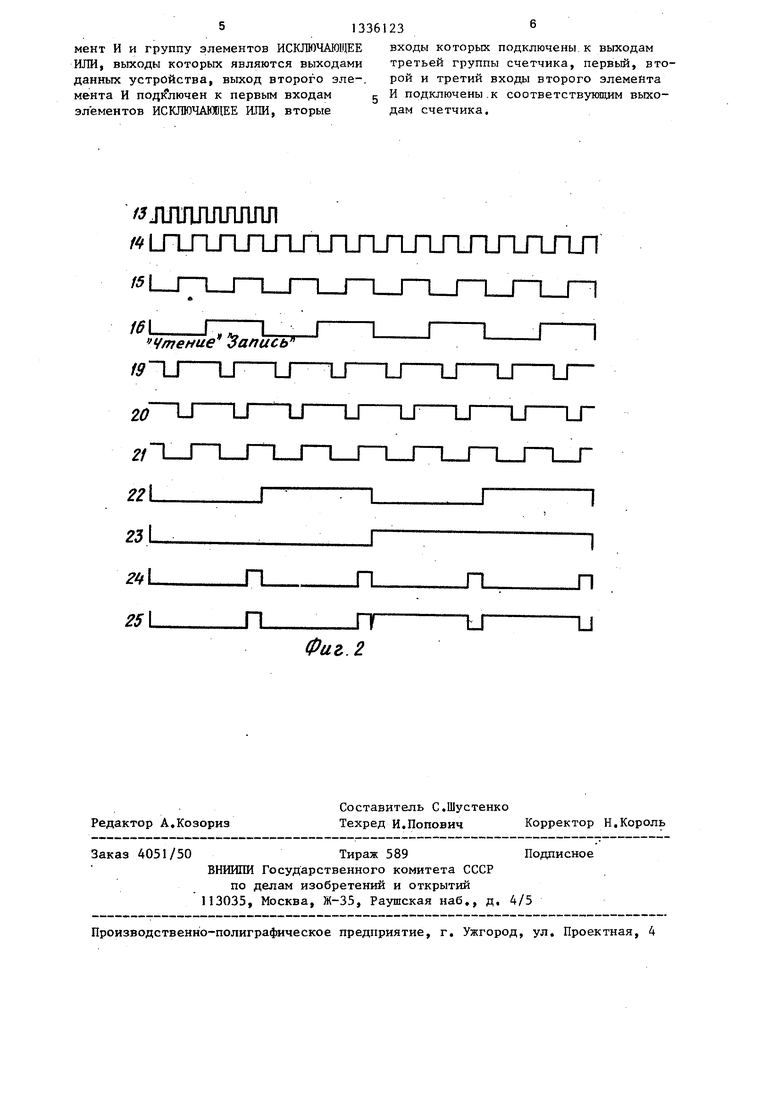

На фиг,1 показана блок-схема устройства; на фиг.2 - временная диаграма работы устройства на примере контроля динамического ОЗУ.

Устройство содержит генератор 1, счетчик 2 (с количеством разрядов п+К+2,гдеп - количество адресных входов контролируемого ОЗУ, К - количество входов данных ОЗУ), дешифратор 3, первый элемент И 4, мульти- плексор 5, триггер 6, элемент 7 задержки, анализатор 8 кодов (например сигнатурный анализатор), второй элемент И 9, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10, адресные выходы 11, вхо- дц 12 данных, выход 13 генератора 11 выход 14 первого младшего разряда (СТО) счетчика -2, выход 15 второго разряда (СТ1) счетчика 2, выход 16 третьего разряда (СТ2) счетчика 2,

23

счетчика 2 через группу элементов ИСКЛЮЧАМВ1ЕЕ ИЛИ 10. Причем в одном из тактов, а именно в четвертом-такте (при наличии на трех младших выходах 14-16 счетчика 2 единичных сигналов), элемент И 9 вырабатывает единичный сигнал, поступающий на входы элементов 10, и данные на выходах 25 инвертируются. Это происходит в момент запрета записи в блок оперативной памяти. В дальнейшем анализатор 8 кодов при считывании данных определяет правильность работы блока памяти, в частности при наличии сигнала запрета записи. 2 ил.

выход 17 режима устройства (ЧТЕНИЕ и ЗАПИСЬ), выход 18 сигнала сопровождения адреса, выход 19 дешифратора 3, выход 20 дешифратора 3 (сигнал сопровождения адреса CAS), выход 21 эле- мента И 4 (сигнал сопровождения адреса RAS), выход 22 первой группы счетчика 2, определяющие младшие разряды адресного кода контролируемого блока памяти (при п адресных входах последним разрядом, определяющим старший разряд адресного кода, будет разряд, п +2 счетчика 2), выход 23 третьей группы выходов счетчика 2 (в общем случае с разряда п + 3), предназначенный для выдачи данных контролируемого блока памяти, выход 24 второго элемента И П и выходы 25 данных устройства.

Устройство работает следующим образом.

Генератор 1, формируя синхроимпульсы, запускает двоичньш счетчик 2, который с помощью выходов 14 (СТО) и 15 (СТ1) и выходов двоичного дешифратора 3 - 19(1) и 20(2) вырабатьшает управляющие сигналы сопровождения адреса 20 (CAS) и 21 (RAS). Сигналы с выходов 19 и 20 управляют работой мультиплексора 5, триггера 6 и элемента 7 задержки, обеспечивающих для динамических ОЗУ мультиплексацию адресных выходов младших и старших разрядов . Вход данных имеет постоянное

нулевое состояние во время первого цикла адресного перебора теста (режим чтения 1/запись 0) и постоянное единичное состояние во время второго пикла адресного перебора теста (режим ЧТЕНИЕ О/ ЗАПИСЬ 1). Во время действия четырехтактного сигнала ЧТЕНИЕ в двух первых тактах имеет место запрет чтения, в третьем такте раз- решение чтения, в четвертом вновь запрет чтения, и выходные сигналы контролируемого блока оперативной памяти в соответствии с ее таблицей состояний/переходов отличаются от этих двух режимов (при запрете чтения - обычно высокоимпедансное состоние, при разрешении чтения - соответствующая записанная ранее информация 0/1), Поэтому будут выявлены такие неисправности, которые привели бы к отсутствию чтения во время его разрешения или, наоборот, к чтению информации во время запрета чтения, поскольку анализатор 8 регист- рирует выходную информацию контролируемого блока оперативной памяти в каждом такте и перемещение ожидаемой информации из одного такта в другой будет зарегистрировано анализа- тором 8.

Во время действия четьфехтактно- FO сигнала ЗАПИСЬ в двух первых тактах имеет место запрет записи, в третьем такте разрешение записи, в четвертом вновь запрет записи, и выходные сигналы контролируемого блока оперативной памяти в соответствии с ее таблицей состояний/переходов не отличаются для этих двух режимов (обычно и при запрете и при разрешении записи на выходе высокоимпедансное состояние). Поэтому выявление таких неисправностей, которые привели бы к отсутствию записи вообще, просто обеспечивается сигнатурным анализатором 8 при последующем счи- тьшании информации. Но выявление таких неисправностей, которые привели бы к осуществлению записи информации не только во время наличия ее разрешения (т.е. в третьем также четырехтактного сигнала ЗАПИСЬ) обеспечивается в предлагаемом устройстве благодаря тому, что на входе данных контролируемого блока памяти состояние входа данных инвертируется в четвертом такте, когда имеет место режим запрета записи, и в случае осуществления при этом собственно записи информации, запишется инверсная информация по отношению к записываемо при разрешении записи, что и будет зарегистрировано в дальнейшем анализатором 8 при считьшании информации. Для автоматической инверсии входной информации в каждом четвертом такте сигнала ЗАПИСЬ введен элемент И 9 (осуществляюш 1Й конъюнкцию выходны сигналов с выходов 14-16 первых трех разрядов счетчика 2), выходной сигнал 24 которого, складываясь по модулю 2 с сигналами на выходах 23 счетчика 2 с помощью элементов ИСКЛЮЧАЮП1ЕЕ ИЛИ 10 (их число равно К-1), обеспечивает требуемые инверсные сигналы на выходах 25.

Формула .изобретения

Устройство для контроля блоков оперативной памяти, содержащее генератор, выход которого подключен к счетному входу счетчика и синхровхо- ду анализатора кодов, информационные входы которого являются информационными входами устройства, дешифратор, первый и второй входы которого подключены соответственно к первому и второму выходу счетчика, третий выход которого является выходом режима устройства, первый элемент И, первый вход которого подключен к первому выходу дешифратора и входу элемента задержки, выход которого подключен к установочному входу триггера, синхро- вход которого подключен к второму выходу дешифратора и второму входу первого элемента И и является первым выходом сигнала стробирования адреса устройства, выход первого элемента И является вторым выходом сигнала стробирования адреса vcтDOЙcтвa, информационный вход триггера является входом сигнала логического нуля устройства, мультиплексор, информационные входы первой и второй групп которого подключены к выходам соответственно первой и второй групп счетчика, выход старшего разряда которого подключен к входу запуска анализатора кодов, выход триггера подключен к управляющему входу мультиплексора, выходы которого являются адресными выходами устройства, отличающееся тем, что, с целью повышения точности контроля, оно содержит второй эле-.

51336123

мент И и группу элементов ИСКЛЮЧАЮЩЕЕ входы которых подключены к выходам ИЛИ, вьпсоды которьпс являются выходами третьей группы счетчика, первьй, вто- данных устройства, выход второго эле-. РОЙ и третий входы второго элемента мента И под1 лючен к первьп. входам g « подключены.к соответствунлцим вько- элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые дам счетчика.

/ ЛШШЛЛЛЯП

/«mjbmijnjiJiJiJiJiJ

г

Чтение апись

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1053165A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1053164A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1987 |

|

SU1413635A2 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1032481A1 |

| Устройство для контроля блоков оперативной памяти | 1990 |

|

SU1751821A1 |

| Устройство для контроля полупроводниковой памяти | 1981 |

|

SU968856A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для функционального контроля блоков оперативной памяти. Цель изобретения - повышение точности контроля. Устройство содер-. жит генератор 1, выход которого подключен к счетному входу счетчика 2, выходы 14 и -15 первого и второго разсо СдЭ 05 ьо САЭ

2ff.

JT

25

Л.

Фиг. 2

п

п

л

JT

ЪГ

| Электростатический двигатель с возвратно-поступательным движением | 1978 |

|

SU744877A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-24—Подача