(Л

ОО

to

со

ND

Изобретение относится к вычислительной технике, в частности к аппаратуре контроля логических блоков вычислительных машин.Цедь изобретения - повышение достоверности контроля.

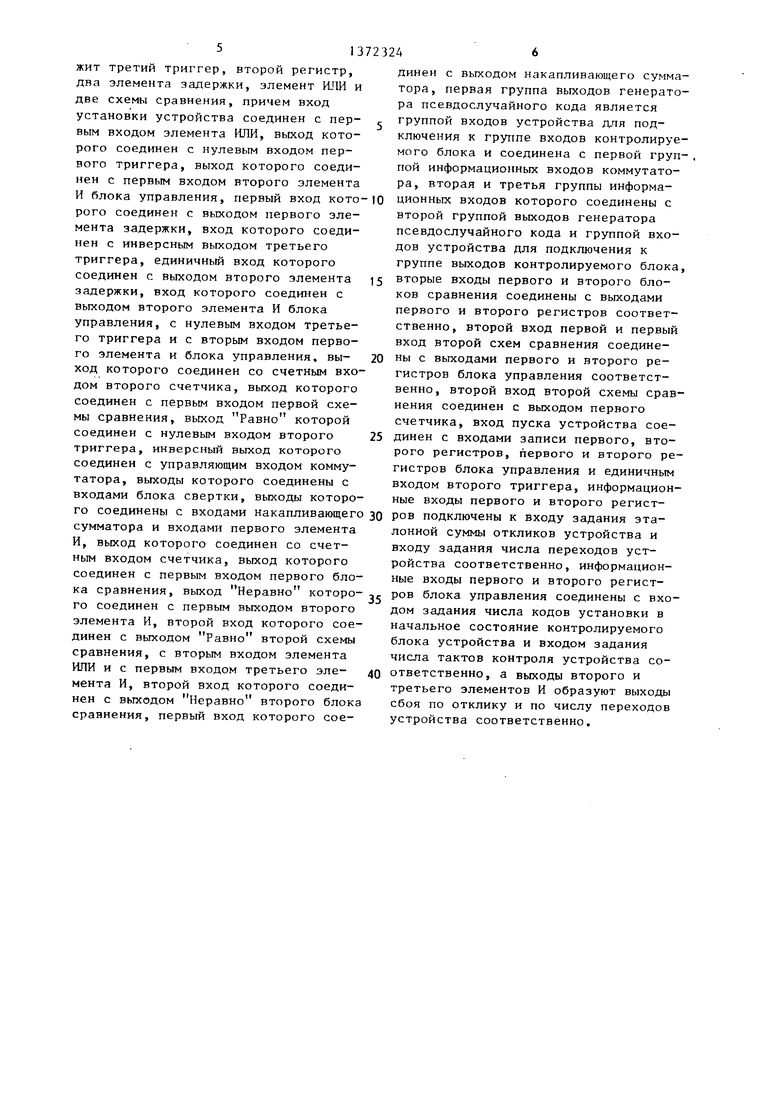

На фиг.1 изображена структурная схема устройства; на фиг.2 - струк турная схема блока управления; на фиг.З - структурная схема блока свертки; на фиг.4 - временная диаграмма работы блока управления.

В состав устройства (фиг„1) входя генератор 1 псевдослучайных кодов I, блок 2 управления, регистры 3 и 4, контролируемый блок 5, коммутатор 6 из элементов И, блок 7 свертки, элемент И 8, счетчик 9, накапливающий сумматор 10, блоки 11 и 12 сравнения элементы И 13 и 14, вход 15 задания эталонной суммы откликов устройства, вход 16 задания числа переходов устройства, вход 17 пуска устройства, вход 18 установки, вход 19 задания числа кодов установки в начальное состояние контролируемого блока устройства, вход 20 задания числа тактов контроля устройства, вькод 21 сбоя по отклику и выход 22 сбоя по числу переходов.

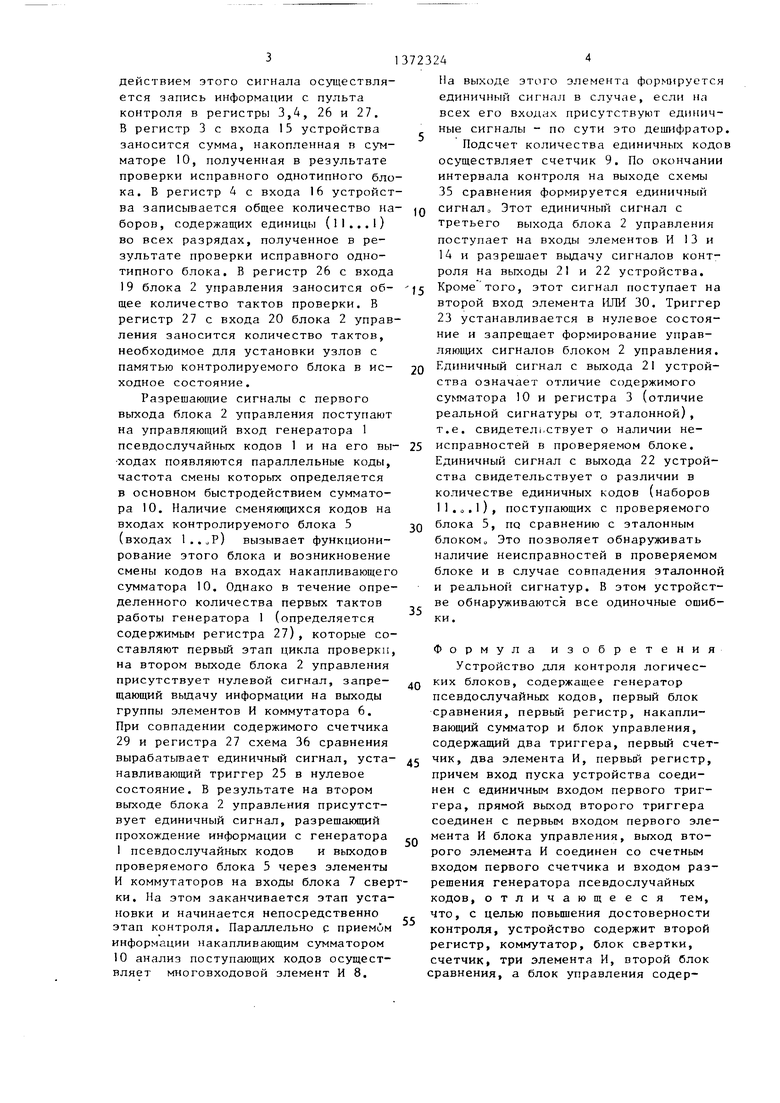

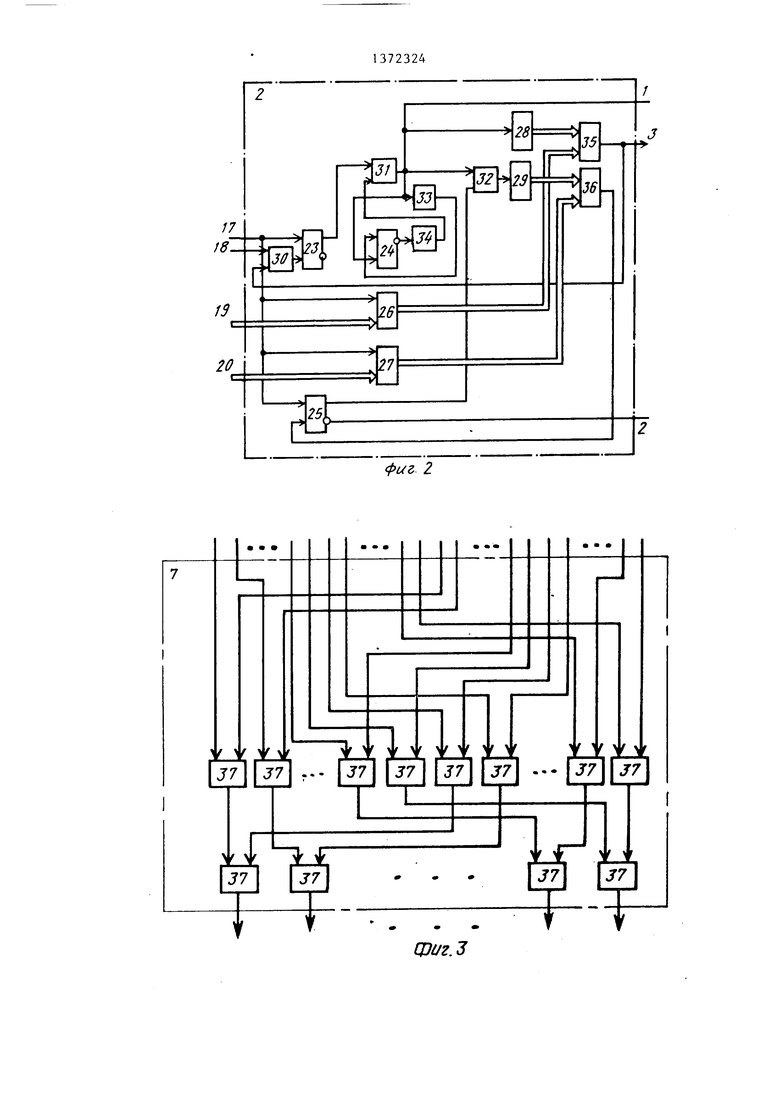

Блок 2 управления (фиГо2) содержит триггеры 23-25, регистры 26 и 27 счетчики 28 и 29, элемент ИЛИ 30, элементы И 31 и 32, элементы задержк 33 и 34 и схемы 35 и 36 сравнения. Блок 7 свертки (фиг.З) содержит элементы переключения ИЛИ 37„

Генератор I псевдослучайных кодов 1 предназначен для формирования тестовых последовательностей для контролир-уемого логического блока и вырабатывает в каждом такте М-разрядный параллельный код (где М - количество выводов проверяемого блока).

Каждый из регистров 3,4, 26 и 27 представляет собой регистр с парафаз ным приемом информации. Регистр 3 п-разрядный (где п - разрядность ко- дов на выходе блока свертки). Регист 4 г-разрядный (где г-1од (Z-R), Z- количество М-разрядных слоев, формируемых генератором 1 псевдослучайных кодов для проверки логического блока R - количество Р-разрядных слоев, фор1 гаруемых генератором 1 псевдослучайных кодов для начальной установки проверяемого блока, Р-количество входов проверяемого блока) Регистр 26 1-разрядный (1-log Z ), а регистр 27 -разрядный (-3 ).

Блок 7 свертки предназначен для преобразования М-разрядной информации, поступающей на его вход, в П- разрядную (где ) и содержит элементы ИСКПЮЧАЩЕЕ ИЛИ. Для контроля логических блоков вычислительной техники он часто строится таким образом, что разрядность информации на его входе и выходе связана следующим отношением: М-К П (где К-целое число). Блок 7 свертки в этом случае содержит (К-1)п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Пример конкретной реализации блока свертки для приведен на фиг.З. Блок 7 свертки содержит 3-п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 37.

Накапливающий сумматор 10 предназначен для сложения параллельных п-разрядных кодов чисел, поступающих на его вход. Он представляет собой накапливающий сумматор с сохранением цифры переноса на каждом такте суммирования.

Каждый из блоков 11 и I2 сравнения представляет собой схему формирования сигнала неравенства двух кодов чисел (п-разрядных и г-разрядных соответственно) и обеспечивает вьщачу единичного сигнала, если коды чисел не равны

Каждая из схем 35 и 36 сравнения представляет собой схему формирования сигнала равенства двух кодов чисел (1-разрядных и 9 -разрядных соответственно) и обеспечивает выдачу единичного сигнала, если коды чисел равны.

Устройство работает следующим образом.

Работа устройства начинается с поступлением сигнала начальной установки от пульта контроля на вход 18 устройства„ Цепи начального обнуления счетчиков 9, 28 и 29, регистров 3, 4, 26 и 27,1 накапливающего сумматора 10 и триггеров 24 и 25 не показаны. По этому же сигналу генератор 1 псевдослучайных кодов 1 устанавливается в определенное исходное состояние (цепь начальной установки генератора не показана), например в такое, когда на всех его выходах присутствуют единичные сигналы. Затем на вход 17 устройства поступает сигнал Пуск с пульта контроля. Под

действием этого сигнала осуществляется запись информации с пульта контроля в регистры 3,4, 26 и 27. В регистр 3 с входа 15 устройства заносится сумма, накопленная в сумматоре 10, полученная в результате проверки исправного однотипного блока. В регистр 4 с входа 16 устройства записывается общее количество наборов, содержащих единицы (11...1) во всех разрядах, полученное в результате проверки исправного однотипного блока. В регистр 26 с входа 19 блока 2 управления заносится общее количество тактов проверки. В регистр 27 с входа 20 блока 2 управления заносится количество тактов, необходимое для установки узлов с памятью контролируемого блока в исходное состояние.

Разрешаюище сигналы с первого выхода блока 2 управления поступают на управляющий вход генератора 1 псевдослучайных кодов 1 и на его вы- ходах появляются параллельные коды, частота смены которых определяется в основном быстродействием сумматора 10. Наличие сменяюп ихся кодов на входах контролируемого блока 5 (входах 1..Р) вызывает функционирование этого блока и возникновение смены кодов на входах накапливающего сумматора 10. Однако в течение определенного количества первых тактов работы генератора 1 (определяется содержимым регистра 27), которые составляют первый этап цикла проверки, на втором выходе блока 2 управления присутствует нулевой сигнал, запрещающий выдачу информации на выходы группы элементов И коммутатора 6. При совпадении содержимого счетчика 29 и регистра 27 схема 36 сравнения вырабатьшает единичный сигнал, устанавливающий триггер 25 в нулевое состояние. В результате на втором выходе блока 2 управления присутствует единичный сигнал, разрешающий прохождение информации с генератора 1 псевдослучайных кодов и выходов проверяемого блока 5 через элементы И коммутаторов на входы блока 7 сверки. На этом заканчивается этап установки и начинается непосредственно этап контроля. Параллельно р приемим информации накапливающим сумматором 10 анализ поступающих кодов осуществляет многоБходовой элемент И 8.

10

15

723244

На выходе этого элемента фop Q pyeтcя единичный сигнал в случае, если на всех его входах присутствуют единич- . ные сигналы - по сути это дещифратор. Подсчет количества единичных кодов осуществляет счетчик 9. По окончании интервала контроля на выходе схемы 35 сравнения формируется единичный сигнал о Этот единичный сигнал с третьего выхода блока 2 управления поступает на входы элементов И 13 и 14 и разрешает вьщачу сигналов контроля на выходы 21 и 22 устройства. Кроме того, этот сигнал поступает на второй вход элемента ИЛИ 30. Триггер 23 устанавливается в нулевое состояние и запрещает формирование управляющих сигналов блоком 2 управления. Единичный сигнал с выхода 21 устройства означает отличие содержимого сумматора 10 и регистра 3 (отличие реальной сигнатуры от. эталонной) , т.е. свидетельствует о наличии неисправностей в проверяемом блоке. Единичный сигнал с выхода 22 устройства свидетельствует о различии в количестве единичных кодов (наборов 1 1 . о. 1) , поступающих с проверяемого блока 5, по сравнению с эталонным блоком Это позволяет обнаруживать наличие неисправностей в проверяемом блоке и в случае совпадения эталонной и реальной сигнатур. В этом устройстве обнаруживаются все одиночные ошибки.

20

25

30

35

0

5

0

5

Формула изобретения

Устройство для контроля логических блоков, содержащее генератор псевдослучайных кодов, первый блок сравнения, первый регистр, накапливающий сумматор и блок управления, содержащий два триггера, первьй счетчик, два элемента И, первый регистр, причем вход пуска устройства соединен с единичным входом первого триггера, прямой выход второго триггера соединен с первьгм входом первого элемента И блока управления, выход второго злемелта И соединен со счетным входом первого счетчика и входом раз- рещения генератора псевдослучайных кодов, отличающееся тем, что, с целью повьщ1ения достоверности контроля, устройство содержит второй регистр, коммутатор, блок свертки, счетчик, три элемента И, второй блок сравнения, а блок управления содер513

жит третий триггер, второй регистр, два элемента задержки, элемент ШШ и две схемы сравнения, причем вход установки устройства соединен с пер- вым входом элемента ИЛИ, выход которого соединен с нулевым входом первого триггера, выход которого соединен с первым входом второго элемента И блока управления, первый вход кото рого соединен с выходом первого элемента задержки, вход которого соединен с инверсным выходом третьего триггера, единичньй вход которого соединен с выходом второго элемента задержки, вход которого соединен с выходом второго элемента И блока

управления, с нулевым входом третьего триггера и с вторым входом первого элемента и блока управления, выход которого соединен со счетным входом второго счетчика, выход которого соединен с первым входом первой схемы сравнения, выход Равно которой соединен с нулевым входом второго триггера, инверсный выход которого соединен с управляющим входом коммутатора, выходы которого соединены с входами блока свертки, выходы которо

дивен с выходом накапливающего сумматора, первая группа выходов генератора псевдослучайного кода является группой входов устройства для подключения к группе входов контролируемого блока и соединена с первой группой информационных входов коммутатора, вторая и третья группы информа- ционньгх входов которого соединены с второй группой выходов генератора псевдослучайного кода и группой входов устройства для подключения к группе выходов контролируемого блока, вторые входы первого и второго блоков сравнения соединены с выходами первого и второго регистров соответственно, второй вход первой и первый вход второй схем сравнения соединены с выходами первого и второго регистров блока управления соответственно, второй вход второй схемы сравнения соединен с выходом первого счетчика, вход пуска устройства соединен с входами записи первого, второго регистров, первого и второго регистров блока управления и единичным входом второго триггера, информационные входы первого и второго регист

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного процесса | 1983 |

|

SU1113800A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1037257A1 |

| Устройство для встроенного тестового контроля | 1986 |

|

SU1324029A1 |

| Устройство для формирования тестовых воздействий | 1984 |

|

SU1168953A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для генерации псевдослучайных последовательностей | 1984 |

|

SU1241434A1 |

Изобретение относится к вычислительной технике, в частности к аппаратуре контроля логических блоков вычислительных машин. Цель изобретения - повышение достоверности контроля. В состав устройства входят генератор 1 псевдослучайных ходов, блок 2 управл- ния, регистры 3,4, подключаемый к контролируемому блоку 5,. коммутатор 6 из элементов И, блок 7 свертки, элемент И 8, счетчик 9, накапливающий сумматор 10, блоки И, 12 сравнения, элементы И 13,14. Устройство позволяет обнаруживать все одиночные ошибки 4 ил.

го соединены с входами накапливающего ЗО РОВ подключены к входу задания эталонной суммы откликов устройства и входу задания числа переходов устройства соответственно, информационные входы первого и второго регистсумматора и входами первого элемента И, выход которого соединен со счетным входом счетчика, выход которого соединен с первым входом первого блока сравнения, выход Неравно которо- ,, ров блока управления соединены с входом задания числа кодов установки в начальное состояние контролируемого блока устройства и входом задания числа тактов контроля устройства со- 40

го соединен с первым выходом второго элемента И, второй вход которого соединен с выходом Равно второй схемы сравнения, с вторым входом элемента ИЛИ и с первым входом третьего элемента И, второй вход которого соединен с выходом Неравно второго блока сравнения, первый вход которого соеответственно, а выходы второго и третьего элементов И образуют выходы сбоя по отклику и по числу переходов устройства соответственно.

лонной суммы откликов устройства и входу задания числа переходов устройства соответственно, информационные входы первого и второго регистров блока управления соединены с входом задания числа кодов установки в начальное состояние контролируемого блока устройства и входом задания числа тактов контроля устройства со-

ров блока управления соединены с входом задания числа кодов установки в начальное состояние контролируемого блока устройства и входом задания числа тактов контроля устройства со-

ответственно, а выходы второго и третьего элементов И образуют выходы сбоя по отклику и по числу переходов устройства соответственно.

фиг 2

ЦЗиг. З

Пербь/й Sjfod

3MfMef f77ff J1.

6/77OpOf/ SJTO

элене /77а l/J/

....Jl

Hi/j eSoi} 6б/;год тригге/уа 2

rL...J

86/jroffП

l/jf

n......

fpf/г. 4

| Способ измерения толщины льда | 1977 |

|

SU643817A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU968816A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-07—Публикация

1986-06-30—Подача