коммутации с вторым входом п-го определителя входов, каждый i-ый вы- . вод контролируемого блока (1 1 , ..., п) соединен с вторым входом 1-го определителя входов блока коммутации и через нормально замкнутые контакты соответствующего реле с четвертым входом элемента 2И-ИЛИ соответствующего j-го блока вычисления остатков (J 2,..., п+1),..шина единичного потенциала соединена с первым, инверсным вторым и четвертым входами элемента 2Й-ИЛИ первого блока вычисления остатков и через вторые нормально разомкнутые контакты каждого из п реле блока ;оммутации с четвертыми входами элементов ilH-HJIH соответствующих блоков вычисления остатков, начиная со второго, выходы регистра сдвига и выход триггера блоков вычисления остатков, начиная со второго, соединены соответственно с входами блока индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1985 |

|

SU1288700A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1142837A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU951312A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Генератор псевдослучайных чисел | 1985 |

|

SU1272484A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Генератор псевдослучайных последовательностей | 1985 |

|

SU1298868A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для косвенного контроля неравномерности воздушного зазора асинхронного двигателя | 1984 |

|

SU1275337A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее генератор псевдослучайных кодов и блок управления, в.состав которого входит генератор тактов, отличающееся тем, что, с целью повышения достоверности контроля, в него введены блок коммутации и блок индикации, причем генератор псевдо- . случайных кодов состоит из (п+1) блоков вычисления-остатков (п чис-. . лу выводов контролируемого блока),, каждый из которых содержит элемент 2И-ИЛИ, выход которого соединен с первым входом первого суммаг тора по модулю два, выход первого сумматора по модулю два соединен с информационным входом регистра сдвига, старший разряд которого соединен с первым входом второго сумматора по модулю два, выход второго сумматора по модулю два соединен с информационным входом триггера, прямой выход которого соединен с первым входом элемента И, выход элемента И соединен с вторыми входами первого и второго сумматоров по модулю два, блок коммутации состоит из п определителей входов, первый и второй выходы каждого кз которых соединены с выводами обмот- , ки соответствующего реле, блок управления .дополнительно содержит два триггера, одновибратор, элемент И и счетчик, причем выход первого триггера соединен с входом одновибратора и с первым входом элемента И, инверсный выход одновибратора соединен с вторым входом элемента И, первый выход .счетчика соединен с входом установки в единицу второго триггера, второй выход счетчика соединен с входом установки в ноль первого триггера, прямой выход одновибратора блока управления соединен с входами установки в ноль счетчика и второго триггера блока управления, регистра сдвига и триггера каждого из (п +1) блоков вычисления остатков и с первым входом п определителей входов блока коммутации, прямой выход второго триггера блока управления соединен с вторым входом (Л элемента И и с первым и инверсным вторы - входами элемента 2И-ИЛИ каждого из (п+1) блоков вычисления остатков, начиная со второго, выхсй а элемента И блока управления соединен с входом генератора тактов, -вн5СОД которого соединен со счетным входом счетчика блока управления и с входами синхронизации триггера ;и регистра сдвига каждого из ln+1) СО б|локов вычисления остатков, вход ч1 установки в единицу первого триггера блока Управления является входом 1чЭ запуска устройства, выход первого О блока вычисления остатков соединен с третьим входом элемента второго блока вычисления остатков, выход каждого предыдущего блока вычисления остатков, начиная со второго по п-ый, соединен с третьим входом элемента 2И-ИЛИ последующего блока вычисления остатков и через первые нормально разомкнутые контакты соответствующего реле блока коммутации с вторым входом соответствукадего определителя входов, выход (п-И)-го блока вычисления отстаков соединен через первые нормально разомкнутые контакты п-го реле блока

Изобретение относится к цифровой вычислительнойтехнике и может быть использовано для автоматической проверки блоков- ЦВМ,

Известно устройство для контроля логических блоков, основанное на методе сравнения выходных сигналов контролируемого и эталонного логических блоков, входные сигналы Которых формируются с помощью счетчика 11 .

Недостатком этого устройства является ограниченная область применения Оно используется только для контроля простых узлов, имеющих небольшое количество входов и не имеющих элементов памяти.

Наиболее близкимпо технической сущности к изобретению является устройство для контроля логических блоков, содержащее блок управления, генератор псевдослучайных кодов, накапливающий сумматор, элементы,И иблок свертки, причем выходы блока управления соединены с управляющими входами генератора псевдослучайных кодов и накапливающего сумматора, выходы генератора псевдослучайных чисел и входы и выходы контролируемого логического блока . соединены с соответствующими входами элементов И, выходы которых соединены со входами блока свертки, выходы блока свертки соединены со Входами накапливающего сумматора, выход которого является выходом устройства .2 ,

Недостатками известного устройства являются низкая достоверность контроля, так как накапливающий сумматор параллельного типа обнаруживает только неисправности, приводящие к изменению числа единиц в выходных последовательностях импульсов проверяемого блока, а также высокая сложность устройства и необходимость ручной перекоммутации входных и выходных каналов в случае

контроля логических блоков различных .типов.

Цель изобретения - повышение достоверности контроля логических блоков.

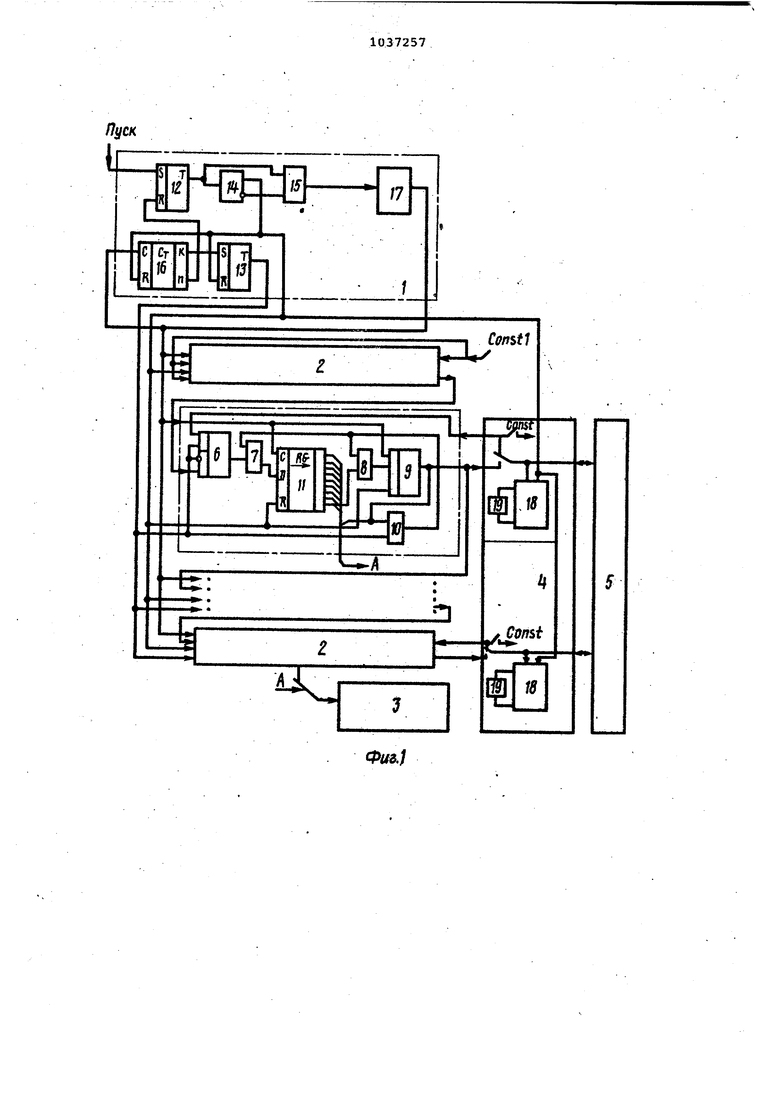

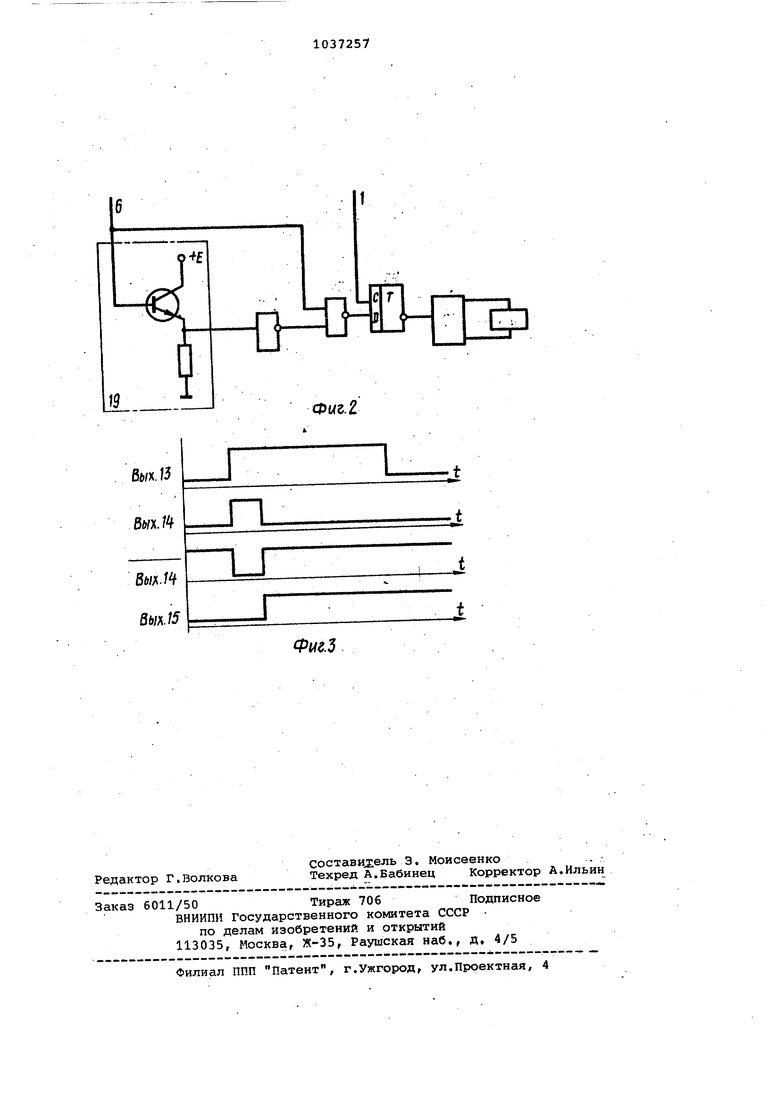

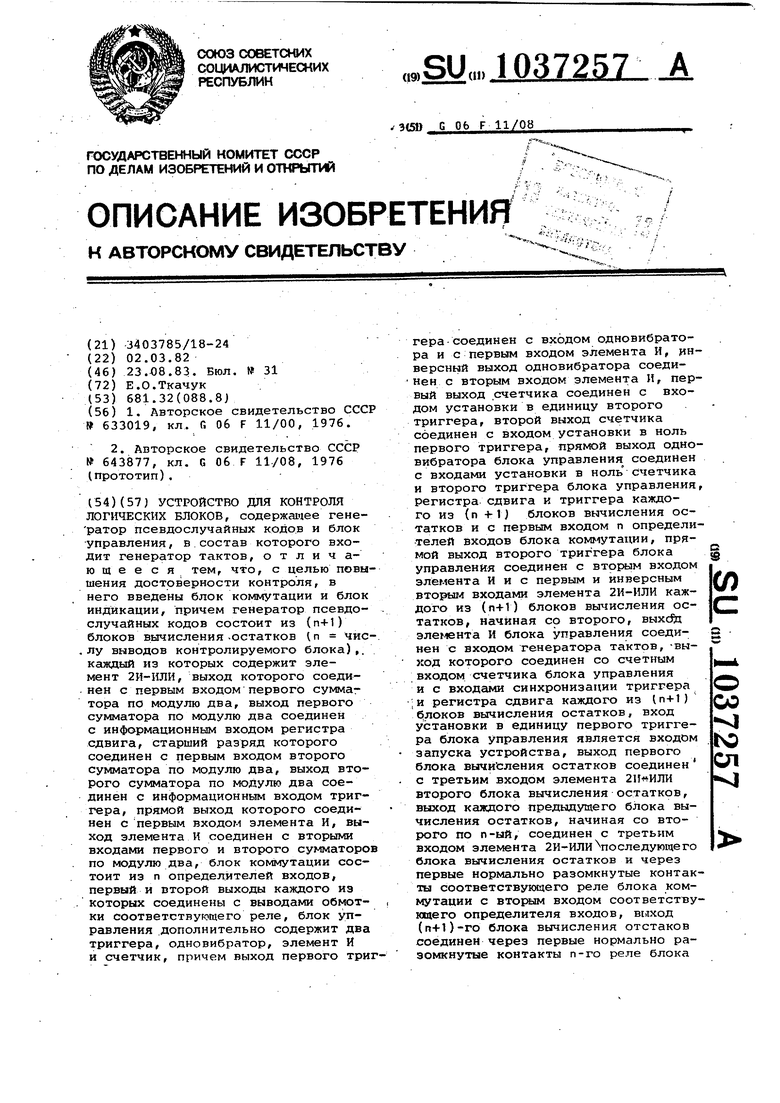

Поставленная цель дс(стигается те что в устройство для контроля логических блоков, содержащее генератор псевдослучайных кодов и блок управления, в состав которого входит генератор тактов, введены блок Kot iMyтации и блок индикации, причем генератор псевдослучаных кодов состоит из (п+1) блоков вычисления остатков (п числу выводов контролируемого блока )j каждый из которых содержит элемент 2И-ИЛИ , выход которого соединен с первым входом первого сумматора по модулю два, выход.первого т:умматора по модулю два соединен с информационным входом регистра сдвига, старший разряд которого соединен с первым входом второго сумматора по модулю два, выход второго сумматора по модулю два соединен с информационным входом триггера, прямой выход которого соединен с первым входом элемента И, выход элемента И соединен с вторыми входами первого и второго сумматоров по модулю два, блок коммутации состоит иэ п определителей входов, первый и второй выходы каждого из которых соединены с выводами обмотки соответствующего реле, блок уп-: равления дополнительно содержит два триггера, одновибратор, элемент И и счетчик, причем выход первого триггера соединен с входом одновибратора и с первым входом элемента И, инверсный выход одновибратора соединен с вторым входом элемента И, первый выход счетчика соединен с входом установки в единицу второго триггера, второй выход счетчика соединен с входом установки в ноль первого триггера, прямой выход одновибратора блока управления соединен с входами установки в ноль счетчика и второго триггера блока управления регистра сдвига и триггера каждого из (п+О блоков вычисления остатков и с первым входсйи определителей вхо дов блока коммутации,-прямой выход . второго триггера блока управления соединен с вторым входом элемента И и с первым и инверсным вторым входа ми элемента 2И-ИЛИ каждого из (п+1) блоков вычисленияостатков, начиная со второго, выход элемента И блока управления соединен с входом генера тора тактов, выход которого соединен со счетным входом счетчика блока управления и с входами синхронизации триггера и регистра сдвига каждого из (n-f-J) блоков вычисления, остатков, вход установки в единицу первого триггера блока управления является входом запуска устройства, выход первого блока вычисления оста ков соединен с третьим входом элемента 2И-НЛИ второго блока вычисления остатков, выход каждого предыду щего блока вычисления остатков, начи ная со второго по п-ый, соединен с третьим входом элемента 2И--ИЛН после дующего блока вычисления остатков и Через первые нормально разомкнутые контактны соответствукнпего реле блока коммутации с вторым входом соответсвующего определителя входов, выход {п+1)-го блока вычисления остатков соединен через первые нормаль но разомкнутые контакты п-го реле, блока коглмутации с вторым входом п-го определителя входов/ каждый i-ый вывод контролируемого блока ( i 1 , . . , п) соединен с вторым входом i-ro определителя входов блока, коммутации и через нормально замкнутые контакты соответствующего реле с четвертым входом элемента 2И-ИЛИ соответствующего j-го блока вычисле ния остатков (У 2,,.., п+1), шина единичного потенциала соединена с первым, инверсным вторым и четвер ТЫ11 входами элемента 2И-ИЛИ первого блока вычисления остатков и через вторые нормально разомкнутые контакты каждого из п реле блоков коммутации с четвертыми входами элементов 2И-ИЛИ соответствующих блоков вычисления остатков, начиная со второго, выходы регистра сдвига и выход триггера блока вычисления остатков, начиная со второго, соединены соответствено с входами блока индикации. На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 г- вариант исполнения определителя входов, на фиг. 3 - временная диаграмма работы блока управления. Устройство содержит блок 1 управления, (п+1) блоков 2 вычисления остатков, блок 3 индикации, блок 4 коглмутации, контролируемый логический блок 5. Каждый блок в -;1числения остатков содержит элемент 2И-ИЛИ.6, сумматоры 7,8. по модулю два,триггер 9, элемент И 10, девятиразрядный регистр 11 сдвига. Влок управления содержит триггеры 12 и 13, одновибратор 14 элемент . И 15, счетчик 16, гейератор 17 тактов. Блок коммутации содержит п опре- делителей 18 входов и п реле 19 по числу выводов контролируемого блока. Каждый иэ блоков вычисления остатков может быть.использован как для генерации тестовых воздействий, так и для контроля реакций контролируемого блока, в зваисимости от того, по какому назначению используется данный вывод. 15лок вычисления остатка выполняет деление последовательности импульсов на пол Ь1Ном вида . о (X) х + X + 1 . Устройство работает следующим образом. По приходу сигнала Пуск триггер 12 устанавливается в единичное состояние и запускает одновибратор 14 сброса, который генерирует импульс сброса, переводящий все элементы устройства в исходное состояние. Тот же импульс подается на определители 18 входов блока-4 коммутации. В том случае, если данный вывод оказался входом, срабатывает реле 19, и сигнал с выхода соответствующего выводу блока вычисления остатков поступает ла вход контролируемого блока. При этом на четвертый вход элемента 2И-ИЛИ блока вычисления остатков коммутируется уровень логической единицы. В этом случае блок вычисления остатков будет работать как генератор псевдослучайной последовательности. Если данный вывод оказался выходом контролируемого блока, коммутация не производится и сигнал с выxoJc;a контролируемого, блока 5 подается на вход блока 2 вычисления остатков. 1 . После окончания импульса сброса начинает работу тактовый генератор. Поскольку триггер 13 находится в.нулевом состоянии, низкий уровень с его выхода подается на входы (п+1) .блоков вычисления отстаков, начиная со второго, чем разрывается обратная связь, и вход каждого регистра сдивга блоков 2 вычисления остатков подключается к выходу предыдущего блока, образуя регистр сдвига длиной 10-п, где п - число выводов контролируемого блока. Вход полученного

регистра подключается к выходу первого блока вычисления остатков, который постоянно работает как генератор псевдослучайной последовательности . Выработанная им по ;ледовательность сдвигается, записывая- начальные состояния в регистры блоков вычисления остатков. На входы контролируемого блока подается псевдослунайная последовательность, выходные сигналы контролируемого блока -при этом не проверяются, так как производится установив в начальное состояние триггера.контролируемого блока и устанавливаются в некоторые отличные друг от друга состояния регистры блоков вычисления остатков По прошествии. К тактов счетчик 15 подает сигнал установки в единицу на триггер 13, и устройство переводится в режим контроля. ПодключаютСИ обратные связи регистров в блоках вычисления остатков, а их входы подключаются к выходам контролируемого блока. Блоки вычисления остатков, подключенные ко входам конт ролируемого блока, работают как генераторы псевдослучаных последовательностей, причем поскольку они были установлены в различные начальные состояния, то и последователь,ности, генерируемые ими, будут, раз

ЛИЧНЫ1

.Количество тактов работы устройства фиксировано, после выдачи последнго тестового воздействия со второго

выхода счетчика 16 блока управлеВИЯ подается сигнал сброса триггера 12, работа тактового генератора прекращается и разрешается индикация вычисленных остатков, которые сравниваются с остатками, полученными в результате проверки исправного одинотипного блока или математического моделирования.

Контролируемый логический блок считается исправным, если указанные остатки совпадают. В противном случае, пользуясь диагностическими словарями и таблицами, определяют место возникновения неисправности.

Таким образом, использование предлагаемого устройства позволяет контролировать логические, блоки цифровой вычислительной техники с высокой достоверностью, так как отклонение данной последовательности выходных импульсов вызовет изменение в значении остатка и облегчит поиск неисправностей в контролируемом устройстве.

I

При этом устройство для контро.ля логических блоков упрощается,поскольку блоки вычисления остатков могут использоваться как для контроля последовательности импульсов, вырабаты ваемой контролируемым блоком, так и для генерации тестовых последовательностей, в зависимости:от назначения данного вывода, контролируемого блока.

Фие.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля логических блоков цвм | 1976 |

|

SU633019A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля логических блоков | 1976 |

|

SU643877A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-08-23—Публикация

1982-03-02—Подача