Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения асинхронного типа.

Цель изобретения - повьшение быстродействия устройства.

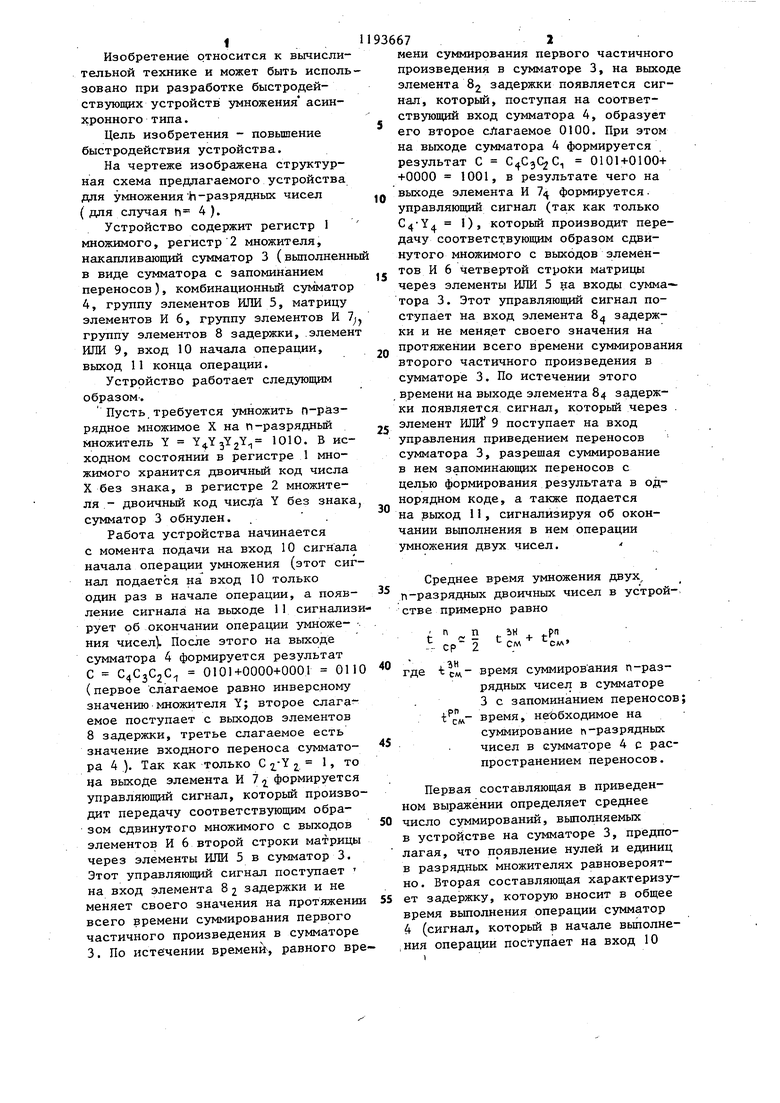

На чертеже изображена структурная схема предлагаемого устройства для умноженияЬ-разрядных чисел ( для случая Г| 4 ).

Устройство содержит регистр 1 множимого, регистр 2 множителя, накапливающий сумматор 3 (выполненнь в виде сумматора с запоминанием переносов ), комбинационньш сумматор 4, группу элементов ИЛИ 5, матрицу элементов И 6, группу элементов И 7 группу элементов 8 задержки, .элемент ИЛИ 9, вход 10 начала операции, выход 11 конца операции.

Устройство работает следующим образом-.

Пусть.требуется умножить п-разрядное множимое X на п-разрядньй множитель Y - 1010. В исходном состоянии в регистре 1 множимого хранится двоичный код числа X без знака, в регистре 2 множителя - двоичный код числа Y без знака, сумматор 3 обнулен. . .

Работа устройства начинается с момента подачи на вход 10 сигнала начала операции умножения (этот сигнал подается на вход 10 только один раз в начале операции, а появление сигнала на выходе 11 сигнализирует об окончании операции умноже- ния чисел). После этого на выходе сумматора 4 формируется результат С С4СзС2С 0101+0000+0001 ОНО (первое слагаемое равно инверсному значению множителя Y; второе слага емое поступает с выходов элементов 8 задержки, третье слагаемое есть значение входного переноса сумматора 4 ). Так как только С i 2. на выходе элемента И 7 формируется управляющий сигнал, который производит передачу соответствующим образом сдвинутого множимого с выходов элементов И 6 второй строки матрицы через элементы ИЛИ 5 в сумматор 3. Этот управляющий сигнал поступает на вход элемента 8 2 задержки и не меняет своего значения на протяжении всего времени суммирования первого частичного произведения в сумматоре 3. По исте чении времени, равного времени суммирования первого частичног произведения в сумматоре 3, на выхо элемента 82 задержки появляется сигнал, который, поступая на соответствующий вход сумматора 4, образует его второе слагаемое 0100. При этом на выходе сумматора 4 формируется . результат С , 0101+0100+ +0000 1001, в результате чего на выходе элемента И формируется. управляющий сигнал (так как только 1), который производит передачу соответствующим образом сдвинутого множимого с выходов элементов И 6 четвертой строки матрицы через элементы ИЛИ 5 на входы сумматора 3. Этот управляющий сигнал поступает на вход элемента 8л задержки и не меня.ет своего значения на протяжении всего времени суммировани второго частичного произведения в сумматоре 3. По истечении этого , времени на выходе элемента 84 задержки появляется сигнал, который через элемент ИЛИ 9 поступает на вход управления приведением переносов сумматора 3, разрешая суммирование в нем запоминающих переносов с целью формирования результата в однорядном коде, а также подается на выход 11, сигнализируя об окончании вьшолнения в нем операции умножения двух чисел.

Среднее время умножения двух, п-разрядных двоичных чисел в устройстве примерно равно

t с

t +

tPn

-слл

- см

-г- СР

о U

где tcM время суммирования п-разрядных чисел в сумматоре 3 с запоминанием переносов; время, неЬбходимое на

суммирование t -разрядных . чисел в сумматоре 4 с распространением переносов.

Первая составляющая в приведенном выражении определяет среднее

0 число суммирований, выполняемых

в устройстве на сумматоре 3, предполагая, что появление нулей и единиц в разрядньгх множителях равновероятно. Вторая составляющая характеризует задержку, которую вносит в общее время выполнения операции сумматор 4 (сигнал, который 5 начале вьшолне,ния операции поступает на вход 10

311936674

и которЬй в дальнейшем осуществляет процессе умножения фактически должен передачу соответствующим образом один раз пройти через весь суммасдвинутых множимых в сумматор 3, в тор 4),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения п-разрядных чисел | 1981 |

|

SU985783A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения @ -разрядных чисел | 1986 |

|

SU1374217A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU993255A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1003077A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1022155A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Устройство для умножения | 1982 |

|

SU1137463A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ П-РАЗРЯДНЫХ ЧИСЕЛ, содержащее регистры множимого и множителя, матрицу элементов И, группу элементов ШШ, накапливающий сумматор, группу элементов И и комбинационный сумматор, причем выходы разрядов регистра множимого, подключены к первым входам элементов И соответствующих столбцов матрицы, прямые выходы разрядов регистра множителя соединены с первыми входами соответствующих элементов И группы, выходы которых соединены с вторыми входами элементов И соответствующих строк матрицы, выход первого элемента И первой строки матрицы соединен с входом первого разряда накапливающего сумматора, выход элемента И п-й строки матрицы соединен с входом

| Устройство для умножения двух -разрядных чисел | 1973 |

|

SU482740A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения двух празрядных чисел | 1977 |

|

SU623204A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения п-разрядных чисел | 1981 |

|

SU985783A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-23—Публикация

1982-10-14—Подача