со

00

4

Изобретение относится к контроль- но-измерительной технике электронной промышленности и может быть использовано в качестве отладочного стенда на этапе логического проектирования цифровой аппаратуры.

Целью изобретения является повышение быстродействия и расширение функциональных возможностей за счет увеличения скорости ввода-вывода сигналов теста.

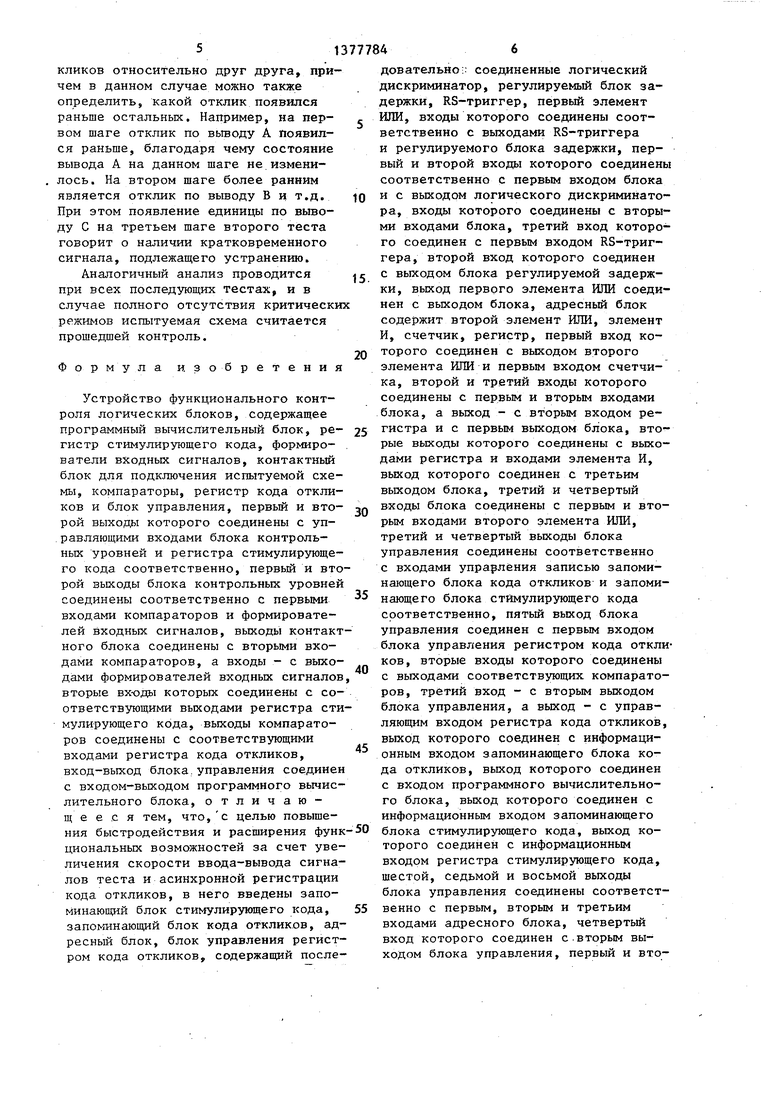

На .фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 - диаграммы его работы.

Устройство содержит программный вычислительный блок 1 (ЭВМ), блок 2 управления, запоминающий блок 3 сти- мулируюш;его кода, регистр 4 стимулирующего кода, формирователи 5.1-5.П входных сигналов, контактный блок 6, блок 7 контрольных уровней, компараторы 8.1-8.п, регистр 9 кода откли137

20 вательности. В блок 10 управления р гистром кода -откликов наносятся дан ные о необходимой величине задержки блока 18, а в блок 7 контрольных уровней - данные об амплитудах вход

ков, блок 10 управления регистром кода откликов, запоминающий блок 11 ко-25 ного и опорного сигналов. При этом

распределение информации между названными блоками осуществляется дешифратором команд блока 2 управлени

да откликов, адресный блок 12, состоящий из многовходового элемента И 13, элемента ИЛИ 14, регистра 15 и счетчика 16.

Блок 10 управления регистром кода откликов содержит логический дискриминатор 17, регулируемый блок 18 задержки, RS-триггер 19 и элемент ШШ 20.

Блок 2 управления содержит управ- ляемьш тактовый генератор, логический узел, дешифратор команд и устройство связи с ЭВМ (не показано). Вьпсо- ды контактного блока 6 соединены с входами компараторов 8.1-8.П, выходы которых соединены с информационньми входами регистра 9 кода откликов, управляющий вход которого соединен с выходом блока 10 управления регистром кода откликов, а выход - с входом запоминающего блока 11 кода откликов, адресные входы которого соединены с вторыми выходами адресного блока 12, вход управления записью - с третьим выходом блока 2 управления, а выход - с входом программного вычислительного блока 1, выход которого соединен с информационным входом запоминающего блока 3 стимулирующего кода, вход управления записью которого соединен с четвертым выходом блока 2 управления, адресный вход - с первым вькодом адресного блока 12, а выход - с информа

77842

ционным входом регистра Д стимулирующего кода, выход которого соединен с входами формирователей 5.1-5.П входных сигналов, другой вход которых соединен с вторым входом блока 7 контрольных уровней, а выход - с входами контактного блока 6.

Устройство работает следзшзщим разом. .

Перед подключением испытуемой схемы к контактному блоку 6 с помощью ЭВМ 1 и блока 2 управления в узлы и блоки устройства заносятся данные,

15 необходимые для работы теста. В запоминающий блок 3 стимулирующего кода по адресам, заносимым в счетчик 16 адресного блока, записывается требуемое количество слов тестовой последо20 вательности. В блок 10 управления регистром кода -откликов наносятся данные о необходимой величине задержки блока 18, а в блок 7 контрольных уровней - данные об амплитудах вход25 ного и опорного сигналов. При этом

5 ного и опорного сигналов. При этом

0

5

0

распределение информации между названными блоками осуществляется дешифратором команд блока 2 управления.

После окончания подготовительных операций и подключения испытуемой схемы к контактному блоку ЭВМ заносит в счетчик 16 код адреса первого слова тестовой последовательности и выдает команду Начало цикла, после получения которой в момент t, запускается тактовый генератор блока 2 управления (фиг.2а). По спаду сигнала генератора блок 2 управления формирует строб-импульс (фиг.26), постук пающий на управляющий вход регистра 4 стимулирующего кода, вход R триггера 1 9 и на один из входов элемента ИЛИ -14. При этом по фронту названного импульса содержимое счетчика 16 (фиг.2в) передается регистр 15 (фиг.2г), а в регистр 4 стимулирую-, щего кода из запоминающего блока 3 заносится первое слово тестовой последовательности (фиг.2д). По спаду строб-импульса содержимое счетчика 16 увеличивается на единицу, и на выходах запоминающего блока 3 спустя некоторое время появляется второе слово стимулирующего кода. Благодаря такой организации работы адресного блока появляется возможность совместить относительно длительный процесс выборки очередного слова тестовой последовательности с процессом рас0

5

пространения стимулирующих сигналов в испытуемой схеме, что способствует повьшению быстродействия устройства

В ответ на воздействие входньпс стимулируюпрпс сигналов испытуемая схема спустя некоторое время выраба- тьгоает сигналы откликов, уровни которых при помощи компараторов 8.1-8.П сравниваются с заданными блоком 7. При этом сигн,ал на выходе компаратора имеет значение 1, если сигнал отклика больше заданного уровня, и значение О в противном случае.

Нормализованные сигналы с выходов компараторов поступают затем на входы регистра 9 кода откликов, выполненного на триггерах типа защелка При этом регистр производит трансляцию поступившей информации на свой выходы, которая разрешена при отсутствии сигнала блокировки на его управлякицем входе, что имеет место в исходном состоянии. Одновременно с процессом распространения сигналов в регистре 9 в блоке 10 управления, куда также поступают сигналы откликов, происходит следующее.

Допустим, что выходной сигнал с одного из компараторов в момент t имеет непредусмотренный всплеск, возникший в результате риска или состязания в испытуемой схеме (фиг.2е). При этом срабатьшает логический дискриминатор 17, реагирующий на любое изменение состояния его входов. Им- пульс с выхода дискриминатора (фиг.2ж), пройдя регулируемый блок 18 задержки и элемент ИЛИ 20, поступает на управляющий вход регистра кода откликов, блокируя изменение информации в последнем. Сигнал с вькода триггера 19, установленного импульсом с дискриминатора в единичное состояние, обеспечивает сохранение блокирующ.го сигнала на выходе элемента ИЛИ 20 до момента выдачи второго слова стимулирующего кода, когда названный триггер будет сброшен в О (фиг.2з).

С приходом фронта тактового импульса генератора блок 2 управления вырабатывает импульс записи кода откликов, поступающий на управляющий вход запоминающего блока 11 (фиг.2и) Информация об откликах, включая непредусмотренные, асинхронным спосо- бом зафиксированная в регистре 9, заносится в память, причем по тому же адресу, по которому в запоминаю

, ю

15 20 5

о 5

0 5

0

5

щем блоке 3 хранится соответствующее слово стимулирующего кода. Далее, по спаду тактового импульса генератора блок управления снова формирует строб-импульс занесения информации в регистр стимулирующего кода , и описанный процесс повторяется.

Так продолжается до тех пор, пока в регистре 15 адресного блока не окажется код адреса последней ячейки запоминакнцего блока 11, состоящий из одних единиц. При этом срабатывает многовходчвый элемент И 13, сигнал с выхода которого вызывает прекращение работы тактового генератора блока 2 управления непосредственно после того, как будет выдан импульс записи кода откликов в последнкио ячейку. После получения соответствующего сообщения об окончании цикла ЭВМ снова заносит в счетчик 16 код начального адреса и выдает команду Чтение. В ответ на приход последней блок 2 управления формирует стро- бирующий сигнал, поступающий на второй вход элемента ИЛИ 14. При этом происходит передача кода адреса из счетчика 16 в регистр 15, а на выходах запоминающего блока 11 появляется соответствующая этому адресу информация. Содержимое счетчика 16 увеличивается на единицу, а ЭВМ, приняв первое слово кода откликов, производит аналогичное обращение за вторым, потом за третьим и так до тех пор, пока не будет считано все Содержимое запоминающего блока 11.

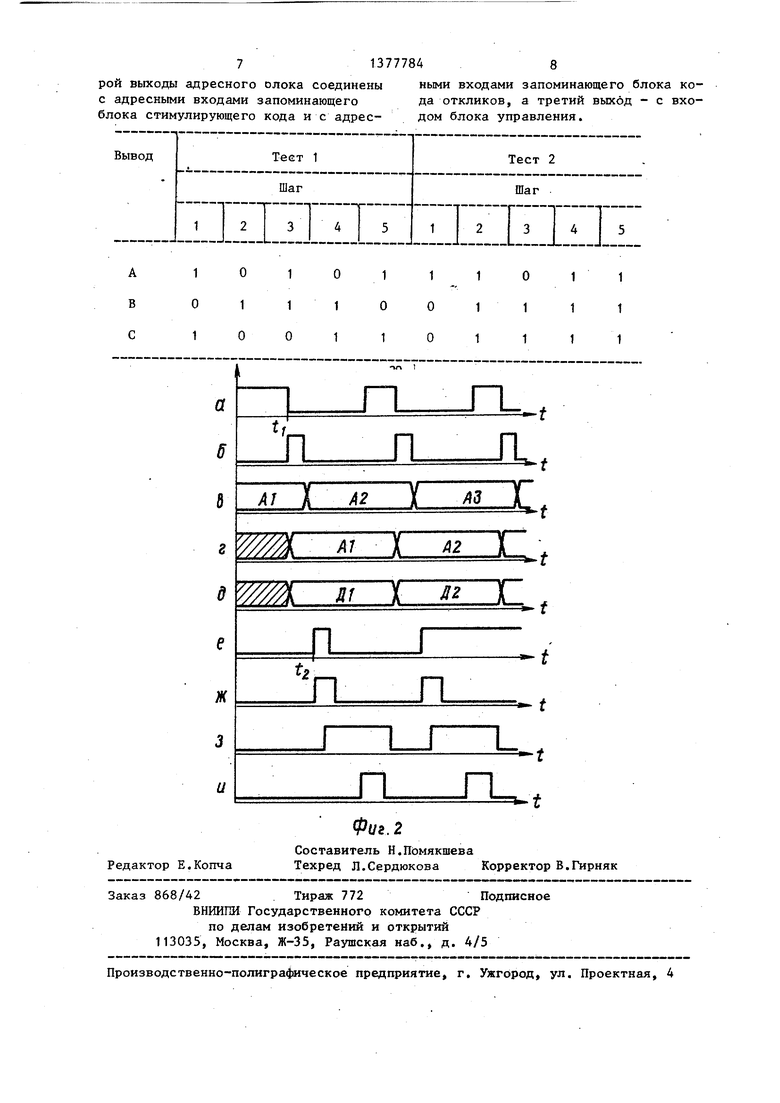

Если в ходе анализа результатов теста будет установлено их полное соответствие ожидаемым, то с целью повьш1ения достоверности тест необходимо многократно повторить, каждый раз уменьшая величину задержки блока 18. При этом возможно появление отличий, связанных, как с задержками сигналов откликов относительно друГ друга, так и с наличием критических режимов в испытуемой схеме. Выявление последних иллюстрируется с помощью таблищ 1, в которой помещены результаты двух тестов из пяти шагов ПО выводам А, В и С испытуемой схемы, причем второму из них соответствует меньшая величина задержки блока 18.

Как видно из таблицы, появление других результатов во втором тесте обусловлено задержками сигналов откликов относительно друг друга, причем в данном случае можно также определить, какой отклик появился раньше остальных. Например, на первом шаге отклик по вьгаоду А появился раньше, благодаря чему состояние вывода А на данном шаге не изменилось. На втором шаге более ранним является отклик по выводу В и т.д. При этом появление единицы по вьгаоду С на третьем шаге второго теста говорит о наличии кратковременного сигнала, подлежащего устранению. Аналогичный анализ проводится при всех последзтощих тестах, и в случае полного отсутствия критических режимов испытуемая схема считается прошедшей контроль.

Формула

13777846

довательно: соединенные логический дискриминатор, регулируемый блок задержки, RS-триггер, первый элемент ИЛИ, входы которого соединены соответственно с выходами RS-триггера и регулируемого блока задержки, первый и второй входы которого соединены соответственно с первым входом блока и с выходом логического дискриминатора, входы которого соединены с вторыми входами блока, третий вход которого соединен с первым входом RS-триггера, второй вход которого соединен с выходом блока регулируемой задержки, выход первого элемента ШШ соединен с выходом блока, адресный блок содержит второй элемент ИЛИ, элемент И, счетчик, регистр, первый вход ко10

15.

20

изобретения

торого соединен с выходом второго элемента РШИ и первым входом счетчика, второй и третий входы которого соединены с первым и вторым входами блока, а выход - с вторьм входом регистра и с первым выходом блока, вторые выходы которого соединены с выходами регистра и входами элемента И, выход которого соединен с третьим выходом блока, третий и четвертый входы блока соединены с первым и вторым входами второго элемента ШШ, третий и четвертый выходы блока управления соединены соответственно с входами управления записью запоминающего блока кода откликов и запоминающего блока стимулирующего кода соответственно, пятый выход блока управления соединен с первым входом блока управления регистром кода откликов, вторые входы которого соединены с выходами соответствующих компараторов, третий вход - с вторым выходом блока управления, а выход - с управляющим входом регистра кода откликов, выход которого соединен с информационным входом запоминающего блока кода откликов, выход которого соединен с входом программного вычислительного блока, выход которого соединен с информационным входом запоминающего

Устройство функционального контроля логических блоков, содержащее программный вычислительный блок, регистр стимулирующего кода, формиро- , ватели входных сигналов, контактный блок для подключения испытуемой схемы, компараторы, регистр кода откликов и блок управления, первый и второй выходы которого соединены с управляющими входами блока контрольных уровней и регистра стимулирующего кода соответственно, первый и второй выходы блока контрольных уровней соединены соответственно с первыми входами компараторов и формирователей входных сигналов, выходы контактного блока соединены с вторыми входами компараторов, а входы - с выходами формирователей входных сигналов, вторые вх-оды которых соединены с соответствующими выходами регистра стимулирующего кода, выходы компараторов соединены с соответствующими входами регистра кода откликов, вход-выход блока.управления соединен с входом-выходом программного вычислительного блока, отличающееся тем, что, с целью повыше25

30

35

40

45

торого соединен с выходом второго элемента РШИ и первым входом счетчика, второй и третий входы которого соединены с первым и вторым входами блока, а выход - с вторьм входом регистра и с первым выходом блока, вторые выходы которого соединены с выходами регистра и входами элемента И, выход которого соединен с третьим выходом блока, третий и четвертый входы блока соединены с первым и вторым входами второго элемента ШШ, третий и четвертый выходы блока управления соединены соответственно с входами управления записью запоминающего блока кода откликов и запоминающего блока стимулирующего кода соответственно, пятый выход блока управления соединен с первым входом блока управления регистром кода откли ков, вторые входы которого соединены с выходами соответствующих компараторов, третий вход - с вторым выходом блока управления, а выход - с управляющим входом регистра кода откликов, выход которого соединен с информационным входом запоминающего блока кода откликов, выход которого соединен с входом программного вычислительного блока, выход которого соединен с информационным входом запоминающего

ния быстродействия и расширения функ-50 блока стимулирующего кода, выход коциональных возможностей за счет увеличения скорости ввода-вывода сигналов теста и асинхронной регистрации кода откликов, в него введены запо- минаюпщй блок стимулирующего кода, запоминающий блок кода откликов, адресный блок, блок управления регистром кода откликов, содержащий после

торого соединен с выходом второго элемента РШИ и первым входом счетчика, второй и третий входы которого соединены с первым и вторым входами блока, а выход - с вторьм входом регистра и с первым выходом блока, вторые выходы которого соединены с выходами регистра и входами элемента И, выход которого соединен с третьим выходом блока, третий и четвертый входы блока соединены с первым и вторым входами второго элемента ШШ, третий и четвертый выходы блока управления соединены соответственно с входами управления записью запоминающего блока кода откликов и запоминающего блока стимулирующего кода соответственно, пятый выход блока управления соединен с первым входом блока управления регистром кода откликов, вторые входы которого соединены с выходами соответствующих компараторов, третий вход - с вторым выходом блока управления, а выход - с управляющим входом регистра кода откликов, выход которого соединен с информационным входом запоминающего блока кода откликов, выход которого соединен с входом программного вычислительного блока, выход которого соединен с информационным входом запоминающего

торого соединен с информационным входом регистра стимулирующего кода, шестой, седьмой и восьмой выходы блока управления соединены соответственно с первым, вторым и третьим входами адресного блока, четвертый вход которого соединен с.вторым вы- хоДом блока управления, первый и вто713777848

рой выходы адресного олока соединены ными входами запоминающего блока ко- с адресными входами запоминающего да откликов, а третий выход - с вхо- блока стимулирующего кода и с адрес- дом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПРОДАЖИ БИЛЕТОВ ПАССАЖИРСКОГО ТРАНСПОРТА | 2004 |

|

RU2280283C1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Устройство для автоматического контроля больших интегральных схем | 1984 |

|

SU1205083A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

Изобретение может быть использовано в качестве отладочного стенда на этапе логического проектирования цифровой аппаратуры. Цель изобретения - повышение быстродействия и расширение функциональных возможностей устройства. Устройство содержит программный вычислительный блок 1, блок 2 управления, регистр 4 стимулирующего кода, формирователи 5.1...5.п входных сигналов, контактнчй блок 6, блок 7 контрольных уровней, компараторы 8.1...8.П, регистр 9 кода откликов. В устройство введен блок 10 управления регистром кода, включающий логический дискриминатор 17, ре- гyлиpye влй блок 18 задержки, RS-триг- гер 19, элемент ИЛИ 20 и адресный блок 12, состоящий из многовходового элемента И 13, элемента ШШ 14, регистра 15 и счетчика 16. Введены также запоминающие блоки 3 и 11 стимулирующего кода и кода откликов, что увеличивает скорость ввода-вывода сигналов теста. 2 ил. t табл. « (Л

| Устройство для контроля больших интегральных схем (БИС) | 1980 |

|

SU918904A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4228537, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-02-28—Публикация

1985-12-11—Подача