(Б) УСТРОЙСТВО для КОНТРОЛЯ БОЛЬШИХ ИНТЕГРАЛЬНЫХ СХЕМ (БИС)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования интегральных схем памяти | 1978 |

|

SU947789A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство функционального контроля интегральных схем с функцией памяти | 1978 |

|

SU748303A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для задания тестов | 1985 |

|

SU1290265A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Устройство для контроля микро-ЭВМ | 1982 |

|

SU1163328A1 |

| Устройство для автоматического контроля больших интегральных схем | 1984 |

|

SU1205083A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU717668A1 |

| Устройство для функционального контроля больших интегральных схем | 1985 |

|

SU1291905A1 |

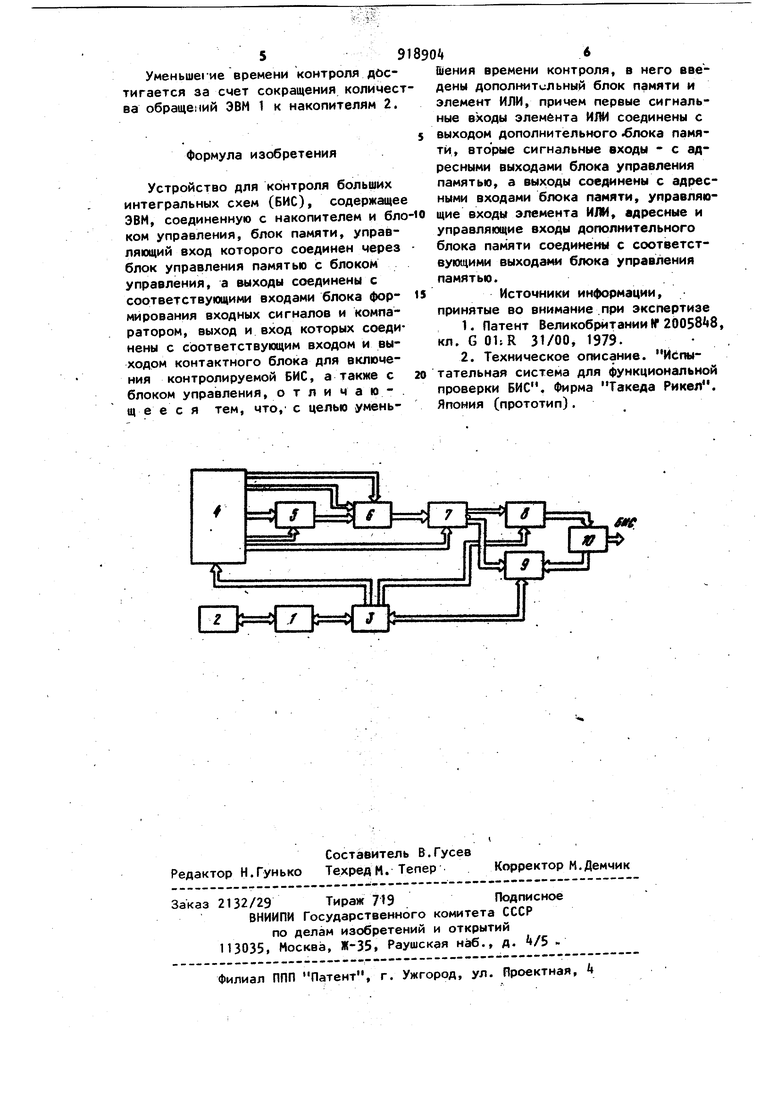

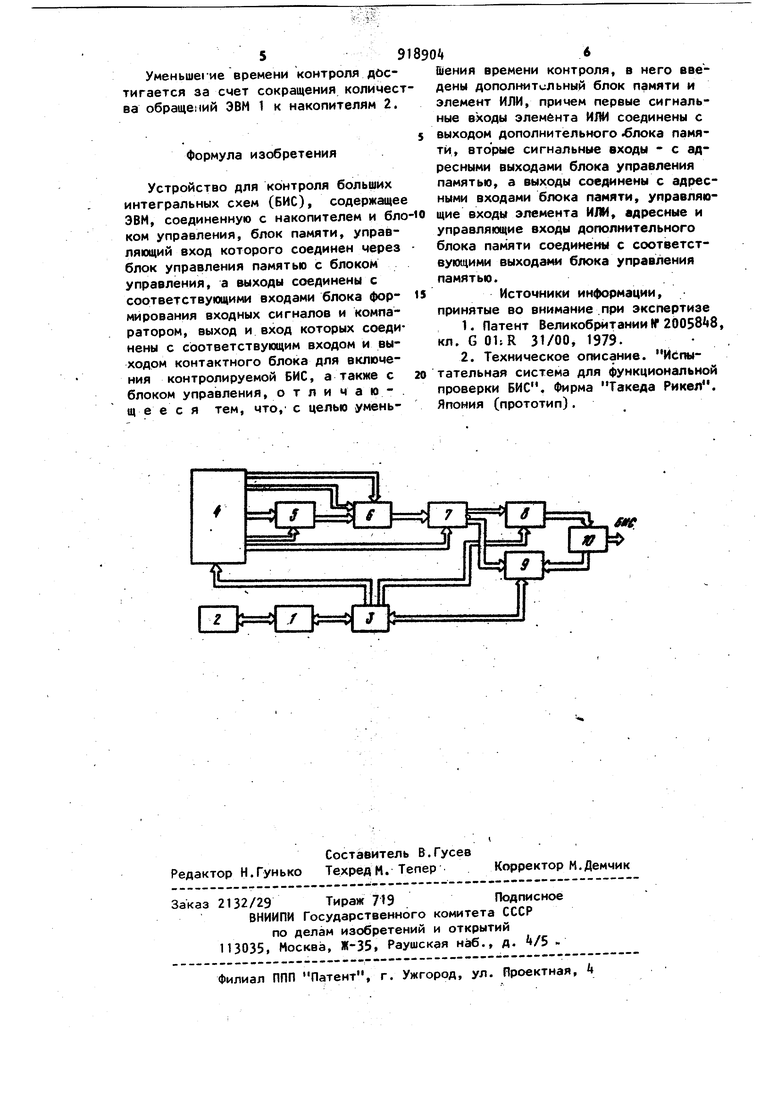

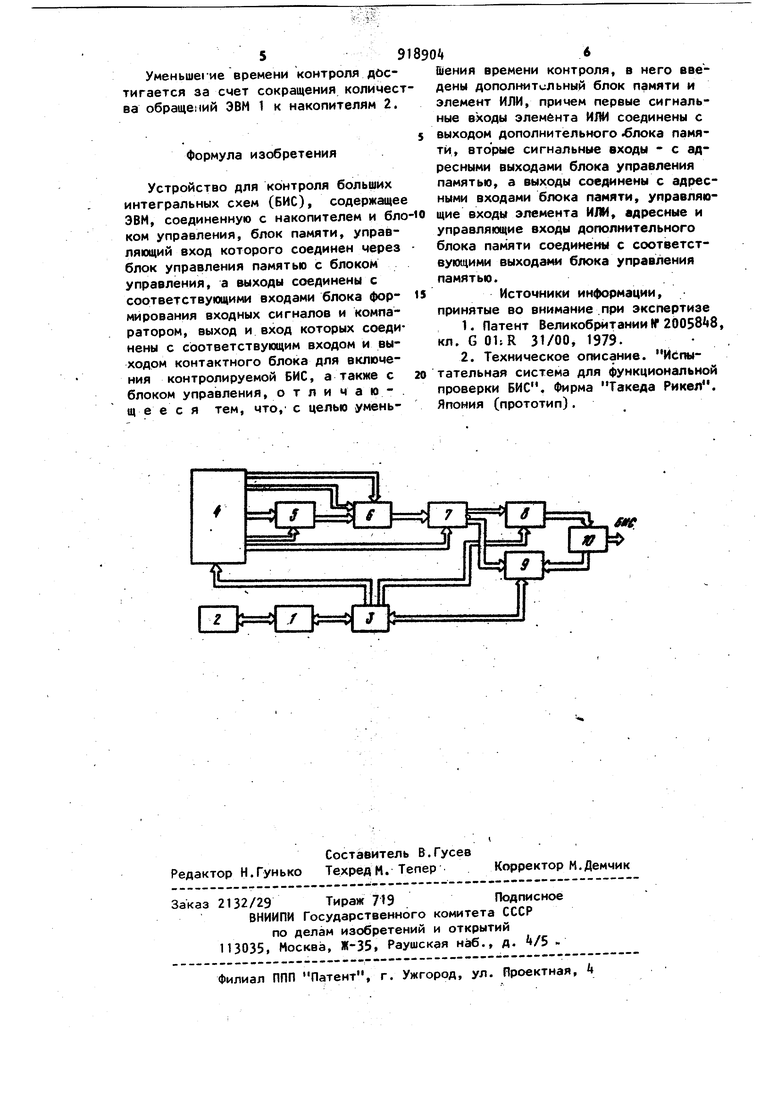

Изобретение относится, к контрольно-измерительной технике и может быт использовано при контроле БИС. Известно устройство контроля БИС, содержащее ЭВМ, измерители параметров, блоки контроля, источник питания, блок контактирования к БИС, ком мутатор и блок управления СТЗ. Недостатком известного устройства является значительное время контроля при подаче на БИС большого количества комбинаций входных кодов. Наиболее близким к изобретению по технической сущности является устройство, содержащее ЭВМ, соединенную с накопителем и блоком управления, выход которого последовательно соединен с блоком управления памятью, с блоком памяти, с блоком формироёа-ния входных сигналов, с блоком контактирования для включения контролируемой БИС и с компаратором ожидаемой информации L2. Недостатком этого устройства является значительное время контроля при необходимости подачи на БИС большого количества входных кодовых воздействий, которое требуется для контроля БИС микропроцессорного набора. Цель изобретения - сокращения времени контроля. Цель достигается тем, что в устройстве, содержащем ЭВМ, соединенную с накопителем и блоком управления, блок памяти, управляющий вход которого соединен через блок управления памятью с блоком управления, а выходы соединены с соответствующими входами блока формирования входных сигналов и компаратором, выход и вход которых соединены с соответствующим входом и Выходом контактного блока для включения контролируемой БИС, а также с блоком управления, введены дополнительный блок памяти и элемент ИЛИ, причем первые сигнальные входы элемента ИЛИ соединены с выхоДОМ дополнительного блока памяти, вторые сигнальные входы - с адресными выходами блока управления памятью, а выходы соединены с адресными входам блока памяти, управляющие входы элемента ИЛИ, адресные и управляющие входы дополнительного блока памяти соединены с соответствующи выходами блока управления памятью. На чертеже представлена функциональная схема устройства. Устройство содержит ЭВМ 1, накопитель 2, блок 3 управления, блок 4 управления памятью, дополнительный блок 5 памяти, элемент 6 ИЛИ, блок 7 памяти, блок 8 формирования входных сигналов, компаратор 9, контактный блок 10 для включения контролируемой БИС. Устройство работает следующим образом. Перед проверкой испытуемой БИС из накопителя 2 посредством ЭВМ 1, блока 3 управления и блока k управления памятью в блок 7 памяти заносится минимальный набор команд-кодовых последовательностей, необходи мых для проведения полного цикла контроля данной БИС, а в дополнительный блок 5 памяти - последовательность адресов этих команд для осуществления циклов проверки. При этом, загрузка информации из накопи теля 2 в память блоков 5 и 7 осуществляется адресным счетчиком и дешифратором команд блока k управлени памятью. Дешифратор команд распределяет информацию между блоками 5 и 7 памяти. В блок 7 памяти информаци заносится посредством адресного сче чика блока k управления памятью через многоразрядный элемент 6 ИЛИ. Последний открывается сигналами с блока Л управления памятью, разрешающими прохождения сигналов адресного счетчика блока управления па мятью во время загрузки информации блок 7 памяти. Затем проверяемая БИС устанавливается в контактный блок 10. По командам с блока f упраёления памятью из дополнительного блока 5 памяти в блок 7 памяти через многоразрядный элемент 6 ИЛИ передается адресная информация, которая выводит информа цию из блока 7 памяти в виде кодово последовательности, затем она (информация) подается на блок 8 форми вания входных сигналов и компаратор 9 4 9. Блок 8 формирования входных сигналов вырабатывает необходимые логические уровни, которые подаются на входы контролируемой БИС. Выходные сигналы БИС (реально получаемая информация - отклик схемы на сигналы воздействия) сравниваются с ожидаемой информацией в компараторе 9. При одинаковой информации БИС считается годной, а при разной бракованной. При этом, компаратор 9 вырабатывает для блока 2 управления сигнал, по получении которого блок 3 управления останавливает измерения и сигнализирует о наличии брака. В случае, если один из несколько выводов контролируемой БИС являются входами и выходами, по окончании процесса занесения информации (запись) осуществляется перевод блока формирования входных сигналов В в третье состояние. Программирование третьего состояния (номера такта и фазы включения) также осуществляется внутри цикла проверки без обращения к постоян1: ой памяти накопителя. Таким образом, в режиме записи информации в , контролируемую БИС управление блоками 5 и 7 памяти осуществляется адресным счетчиком и дешифратором команд блока k управления памятью, причем блок 7 памяти управляется через многоразрядный элемент 6 ИЛИ. В режиме считывания информации (проверка БИС)дополнительный блок 5 памяти управляется адресным счетчиком блока управления памятью, а блок 7 памяти через многоразрядную схему ИЛИ - блоком 5 памяти, являющимся адресным устройством для блока 7 памяти. Сокращение времени контроля в предлагаемом устройстве без прямого увеличения объема памяти осуществляется благодаря введению блока 5 памяти и элемента 6 ИЛИ, если число различных входных воздействий, подаваемых на контролируемую БИС, ограничено, а количество их комбинаций значительно. Это дает возможность в блок 7 памяти записать минимальное число расличных кодовых последовательностей, необходимых длЯ контроля БИС, а в дополнительный блок 5 памяти - адреса вышеназванных последовательностей. Благодаря введению многоразрядного элемента схемы ИЛИ обеспечивается рациональное использование памяти устройства, а также повышение е,е емкости без прямого увеличения объема. Уменьшегие времени контроля достигается за счет сокращения количес ва обращений ЭВМ 1 к накопителям 2. Формула изобретения Устройство для контроля больших интегральных схем (БИС), содержаще ЭВМ, соединенную с накопителем и бл ком управления, блок памяти, управляющий вход которого соединен через блок управления памятью с блоком управления, а выходы соединены с соответствующими входами блока формирования входных сигналов и компаратором, выход и вход которых соеди нены с соответствующим входом и выходом контактного блока для включения контролируемой БИС, а также с блоком упра1вления, отличающ е е с я тем, что, с целью уменьfKfШения времени контроля, в него введены дополнительный блок памяти и элемент ИЛИ, причем первые сигнальные входы элемента ИЛИ соединены с выходом дополнительного лока памяти, вторые сигнальные входы - с адресными выходами блока управления памятью, а выходы соединены с адресными входами блока памяти, управляющие входы элемента ИЛИ, адресные и управляющие входы дополнительного блока памяти соединены с соответствующими выходами блока управления памятью. Источники информации, принятые во внимание .при экспертизе 1.Патент Великобритании 1Г 20058i8, кл. G 01; R 31/00, 1979. , 2.Техническое описание. Испытательная система для функциональной проверки БИС. Фирма Такеда Рикел. Япония (прототип).

Авторы

Даты

1982-04-07—Публикация

1980-06-10—Подача