Изобретение относится к вычислительной технике, а именно к гибридным вычислительным устройствам, предназначенным для точного и длительного интегрирования произвольно меняющихся функций времени.

Цел: .3 изобретения является расширение функциональных- возможностей усройства за счет оперативного изменения в процессе решения постоянной времени в широких пределах.

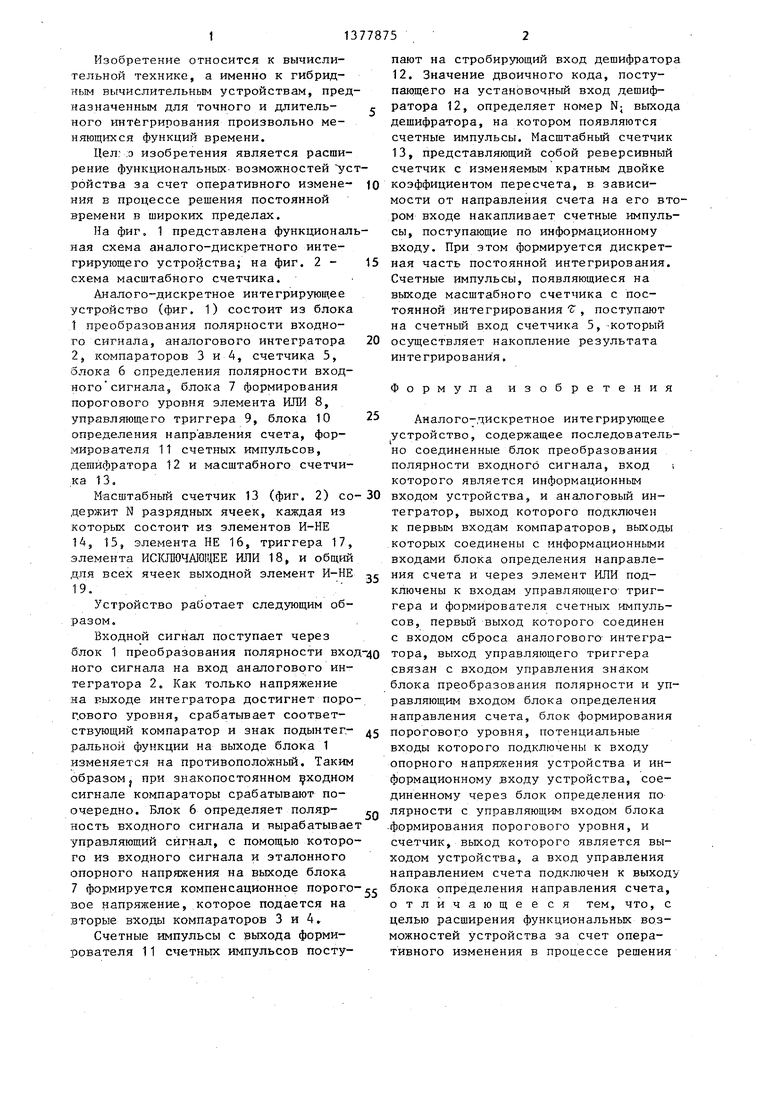

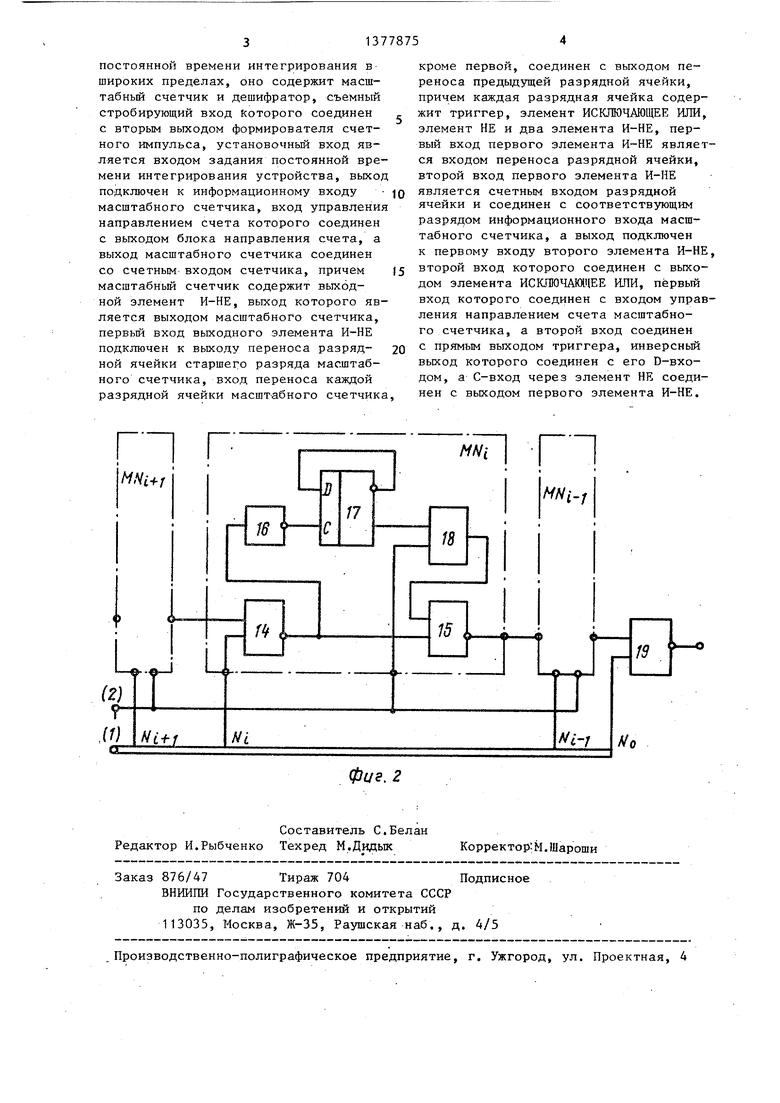

На фиг. 1 представлена функционалная схема аналого-дискретного интегрирующего устройства; на фиг. 2 - схема масштабного счетчика.

Аналого-дискретное интегрирующее устройство (фиг. 1) состоит из блока t преобразования полярности входного сигнала, аналогового интегратора 2, компараторов 3 и 4, счетчика 5, блока 6 определения полярности входного сигнала, блока 7 формирования порогового уровня элемента ИЛИ 8, управляющего триггера 9, блока 10 определения направления счета, формирователя It счетных импульсов, дешифратора 12 и масштабного счетчика 13.

М-асштабный счетчик 13 (фиг. 2) содержит N разрядных ячеек, каждая из которых состоит из элементов И-НЕ 14, 15, элемента НЕ 16, триггера 17, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18, и общий для всех ячеек выходной элемент И-НЕ 19, ,

Устройство работает следующим образом.

Входной сигнал поступает через блок 1 преобразования полярности вхоного сигнала на вход аналогового интегратора 2. Как только напряжение на выходе интегратора достигнет поро г.ового уровня, срабатывает соответствующий компаратор и знак подынтегральной функции на выходе блока 1 изменяется на противоположный. Таким образомJ при знакопостоянном ходном сигнале компараторы срабатывают поочередно. Блок 6 определяет полярность входного сигнала и вырабатывае управляющий сигнал, с помощью которого из входного сигнала и эталонного опорного напряжения на вькоде блока 7 формируется компенсационное пороговое напряжение, которое подается на вторые входы компараторов 3 и 4..

Счетные импульсы с выхода формирователя 11 счетных импульсов посту

пают на стробирующий вход дешифратора

12.Значение двоичного кода, поступающего на установочный вход дешифс ратора 12, определяет номер N; выхода дешифратора, на котором появляются счетные импульсы. Масштабный счетчик

13,представляющий собой реверсивный счетчик с изменяемьм кратным двойке

10 коэффициентом пересчета, в зависимости от направления счета на его втором входе накапливает счетные импульсы, поступающие по информационному входу. При этом формируется дискрет15 ная часть постоянной интегрирования. Счетные импульсы, появляющиеся на выходе масштабного счетчика с постоянной интегрирования о , поступают на счетный вход счетчика 5, -который

20 осуществляет накопление результата интегрирования.

Формула изобретения

25 Аналого-дискретное интегрирующее устройство, содержащее последовательно соединенные блок преобразования полярности входного сигнала, вход ; которого является информационным

30 входом устройства, и аналоговый интегратор, выход которого подключен к первым входам компараторов, выходы .которых соединены с информационными входами блока определения направле5 ния счета и через элемент ИЛИ подключены к входам управляющего триггера и формирователя счетных импульсов, первый выход которого соединен с входом сброса аналогового интегра- 0 тора, выход управляющего триггера связан с входом управления знаком блока преобразования полярности и управляющим входом блока определения направления счета, блок формирования

5 порогового уровня, потенциальные входы которого подключены к входу опорного напряжения устройства и информационному входу устройства, соединенному через блок определения по лярности с управляющим входом блока -формирования порогового уровня, и счетчик, выход которого является выходом устройства, а вход управления направлением счета подключен к выходу

5 блока определения направления счета, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет оперативного изменения в процессе решения

0

постоянной времени интегрирования в широких пределах, оно содержит масштабный счетчик и дешифратор, съемный стробирующий вход Которого соединен с вторым выходом формирователя счетного импульса, установочньй вход является входом задания постоянной времени интегрирования устройства, выход подключен к информационному входу масштабного счетчика, вход управления направлением счета которого соединен с выходом блока направления счета, а выход масштабного счетчика соединен со счетным входом счетчика, причем масштабньй счетчик содержит выходной элемент И-НЕ, выход которого является выходом масштабного счетчика, первый вход выходного элемента И-НЕ подключен к выходу переноса разряд- ной ячейки старшего разряда масштабного счетчика, вход переноса каждой разрядной ячейки масштабного счетчика

кроме первой, соединен с выходом переноса предыдущей разрядной ячейки, причем каждая разрядная ячейка содержит триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ и два элемента И-НЕ, первый вход первого элемента И-НЕ является входом переноса разрядной ячейки, второй вход первого элемента И-НЕ является счетным входом разрядной ячейки и соединен с соответствующим разрядом информационного входа масштабного счетчика, а выход подключен к первому входу второго элемента И-НЕ второй вход которого соединен с выходом элемента ИСКЛЮЧАЖЦЕЕ ИЛИ, первый вход которого соединен с входом управления направлением счета масштабного счетчика, а второй вход соединен с прямым выходом триггера, инверсньй выход которого соединен с его D-BXO- дом, а С-вход через элемент НЕ соединен с выходом первого элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| Аналого-дискретное интегрирующее устройство | 1975 |

|

SU556463A1 |

| Аналого-дискретное интегрирующее устройство | 1979 |

|

SU875407A1 |

| Аналого-дискретное интегрирующее устройство | 1985 |

|

SU1327128A1 |

| Аналого-дискретное интегрирующее устройство | 1986 |

|

SU1432563A2 |

| Дискретно-аналоговый интегратор | 1976 |

|

SU611218A1 |

| Функциональный аналого-цифровой преобразователь | 1983 |

|

SU1113813A1 |

| Устройство для определения степени затухания измерительных магнитоэлектрических преобразователей | 1988 |

|

SU1628028A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1986 |

|

SU1473083A1 |

| Функциональное интегрирующее устройство | 1977 |

|

SU732903A1 |

Изобретение относится к вычислительной технике, а именно к гиб- . ридным вычислительным устройствам, предназначенным для .точного и длительного интегрирования произвольно меняющихся функций времени. Целью Von изобретения является расширение функциональных возможностей за счет оперативного изменения в процессе расширения постоянной времени в широком диапазоне. Аналого-дискретное интегрирующее устройство содержит блок 1 преобразования полярности ВХ.ОДН о го сигнала, аналоговый интегратор 2, компараторы 3 и 4, счетчик 5, блок 6 определения полярности входного сигнала, блок 7 формирования порогового уровня, элемент ИЛИ 8, управляющий триггер 9, блок 10 определения направления счета, формирователь 11 счетных импульсов, дешифратор 12 и масштабный счетчик 13. Введенный в устройство масштабный счетчик 13 позволяет дискретно в широком диапазоне изменять постоянную времени интегрирования. 2 ил. W со ч| 00 4j ел (JiUtl

| Аналого-дискретное интегрирующее устройство | 1975 |

|

SU556463A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналого-дискретное интегрирующее устройство | 1979 |

|

SU875407A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-28—Публикация

1986-02-07—Подача