Изобретение относится к аналого- цифровой вьшислительной технике, а Именно к гибридным вычислительным |устройствам, предназначенным для де- йитель юго и точного интегрирования произвольно меняющейся функции времени, и является усовершенствованием изобретения по авт. св. № 1377875.

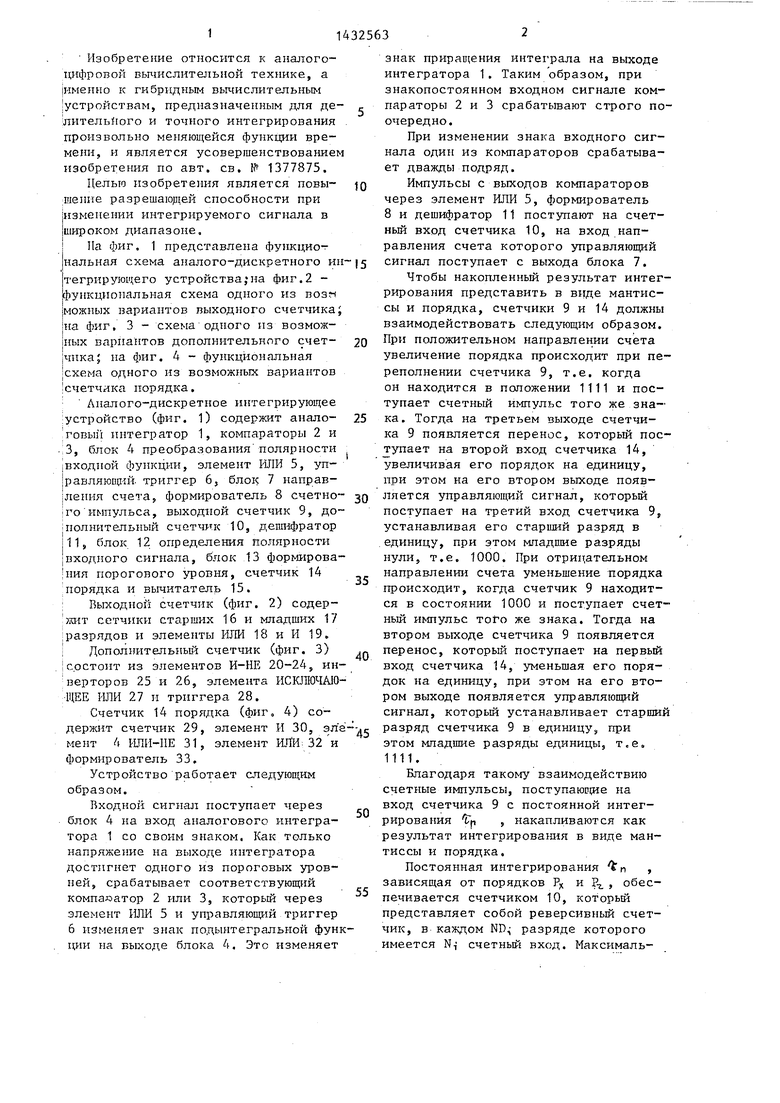

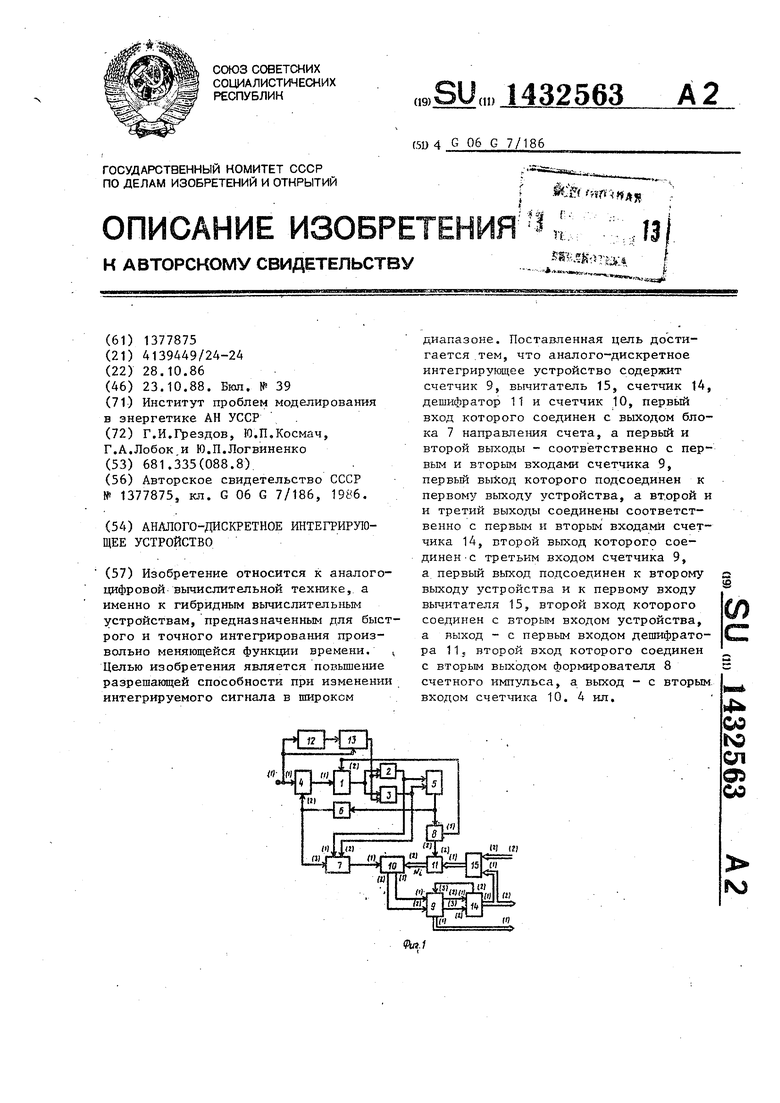

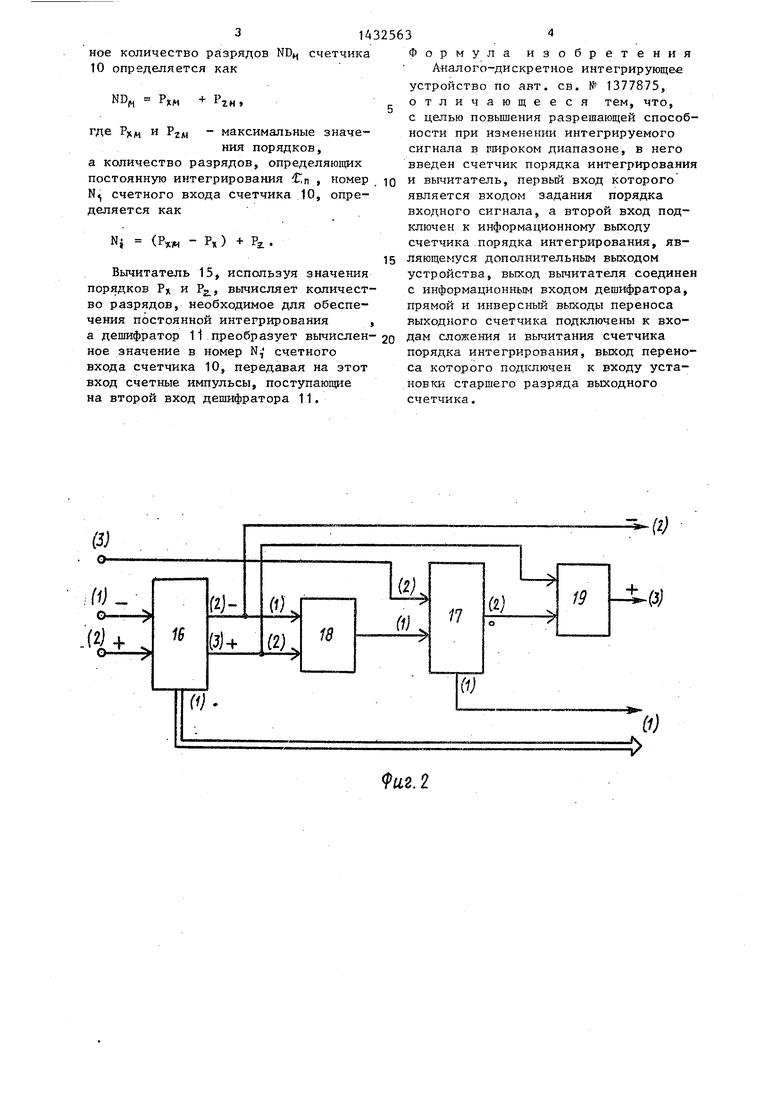

Целью изобретения является новы- шеппе разрешающей способности при |изменении интегрируемого сигнала в |широком диапазоне. I Па фиг, 1 представлена функдио- |нальная схема аналого-дискретного ин тегрирующего устройства;на фиг.2 - функциональная схема одного из возм 1МОЖНЫХ вариантов выходного счетчика; на фиг. 3 - схема одного из возмож- |ных вариантов дополнительного счет- |чпка; на фиг. А - функциональная |схема одного из возможных вариантов счетчлка порядка.

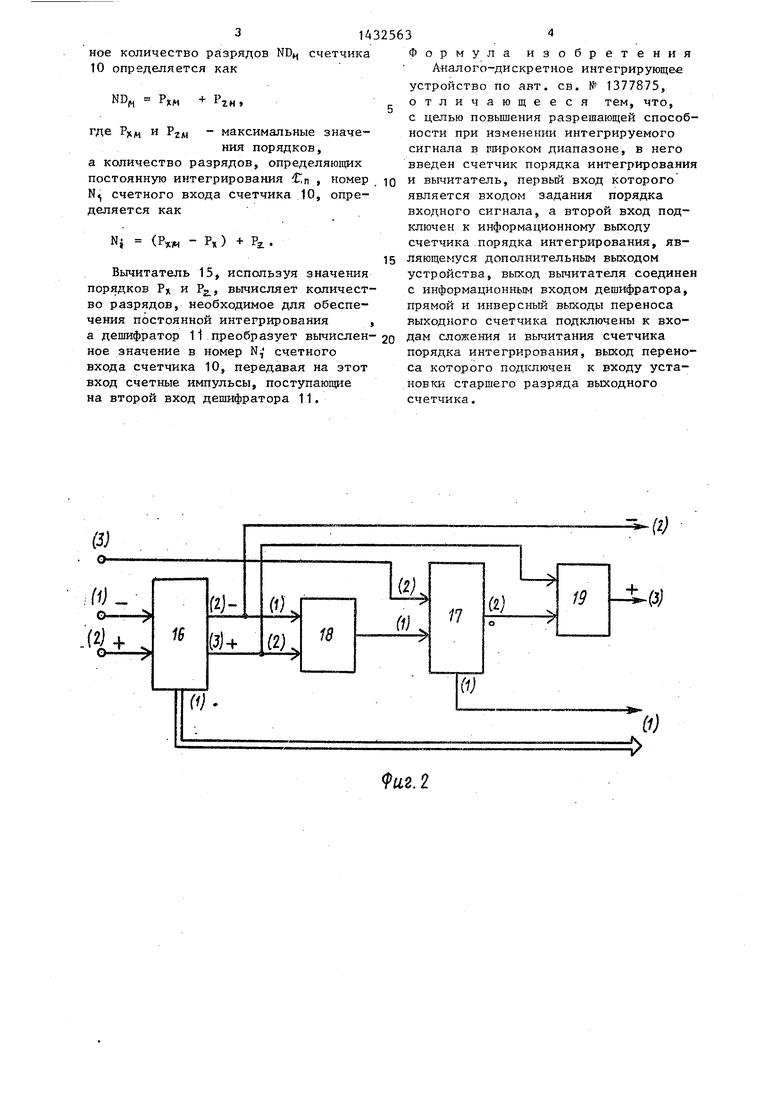

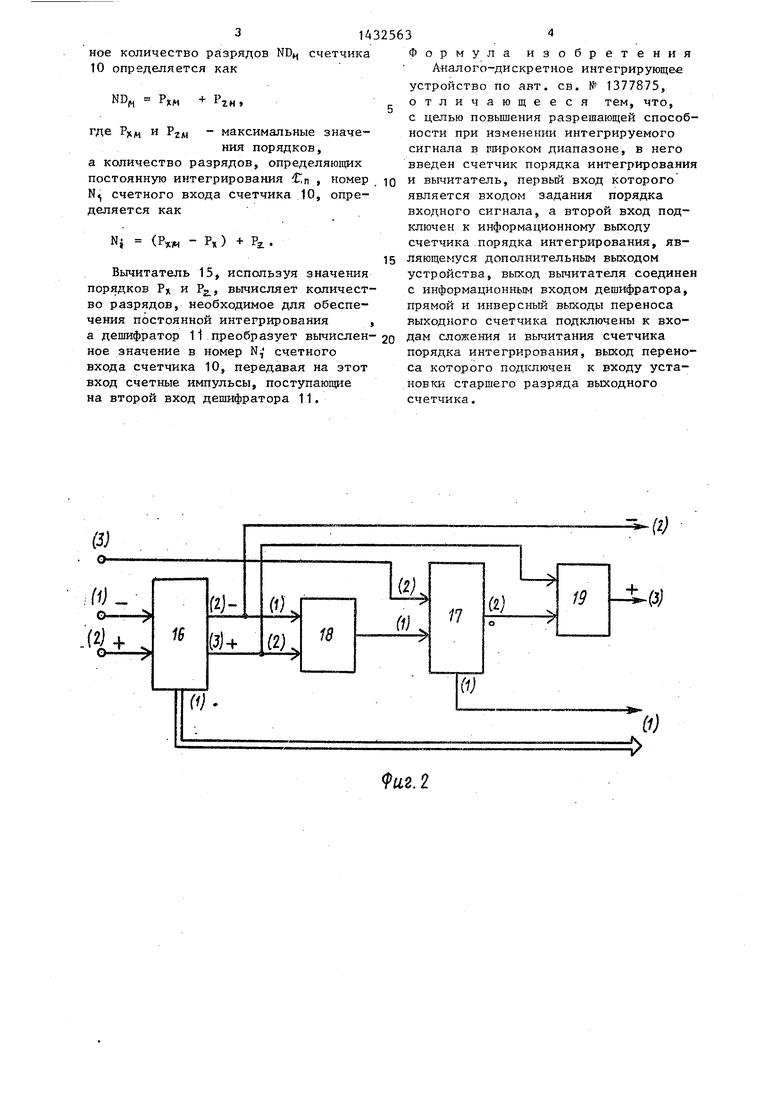

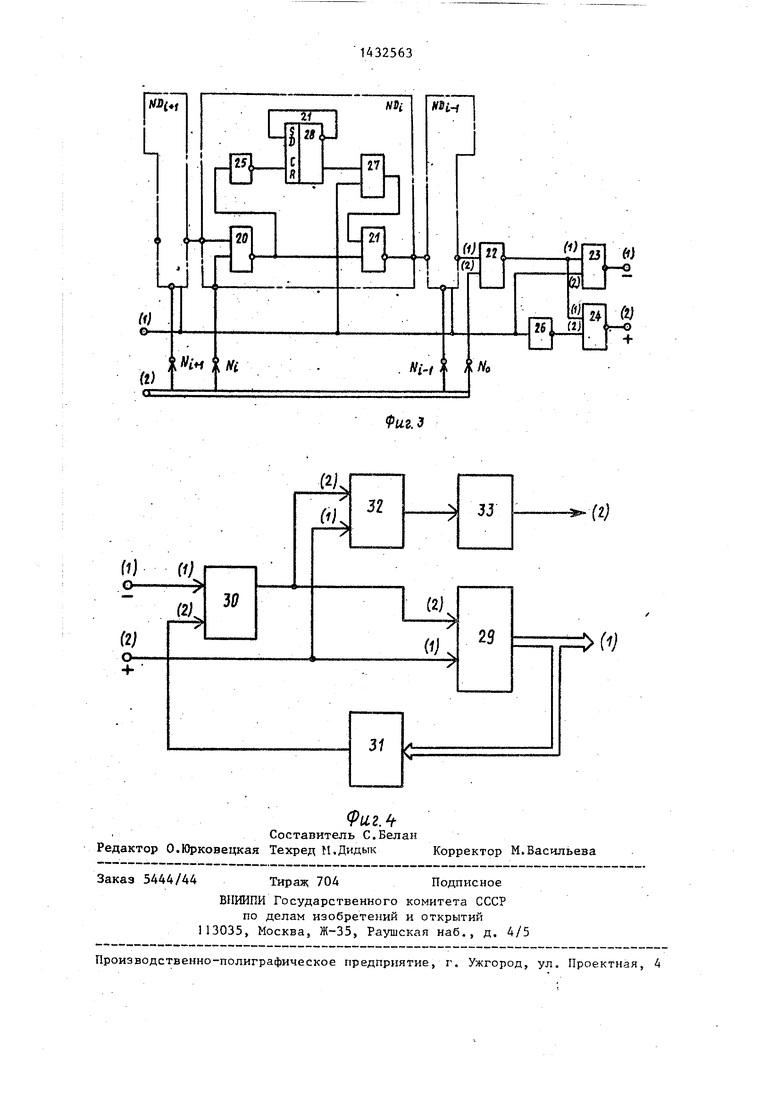

Лналого-дискретное интегрирующее :устройство (фиг. 1) содержит анало- :говыГ1 интегратор 1, компараторы 2 и .3, блок А преобразования полярности |входной фуюсции, элемент ИЛИ 5, уп- ipaвляюи Iiй. триггер 6, блок 7 направ- ;ления счета, формирователь 8 счетно- Iго импульса, выходной счетчик 9, до- |полнительный счетчик 10, дeшiфpaтop 11, блок 12 определения полярности входного сигнала, блок 13 формирова ;ния порогового уровня, счетчик 1А ;порядка и вычитатель 15. : Выходной счетчик (фиг. 2) содер- сетчики старших 16 и младших 17 ;разрядов и элементы ИЛИ 18 и И 19. : Дополнительный счетчик (фиг. 3) I состоит из элементов И-НЕ 20-2А, ин вер торов 25 и 26, элемента ИСЮ1ЮЧА10 ;ЩЕЕ ИЛИ 27 и триггера 28.

Счетчик 1А порядка (фиг. А) со- деряшт счетчик 29, элемент И 30, эл мент 4 1 ШИ-11Е 31, элемент ИЛИ 32 и формирователь 33.

Устройство работает следующим образом.

Входной сигнал поступает через блок А на вход аналогового интегратора 1 со своим знаком. Как только напряжение на выходе интегратора достигнет одного из пороговых у1эов- ней, срабатывает соответствующий компалатор 2 или 3, который через элемент ИЛИ 5 и управляющий триггер 6 изменяет знак подынтегральной фунции на выходе блока А. Это изменяет

0

О Q

с

5

0

5

знак приращения интеграла на выходе интегратора 1. Таким образом, при знакопостоянном входном сигнале компараторы 2 и 3 срабатывают строго поочередно.

При изменении знака входного сигнала один из кo fflapaтopoв срабатывает дважды подряд.

Импульсы с выходов компараторов через элемент ИЛИ 5, формирователь 8 и дешифратор 11 поступают на счетный вход счетчика 10, на вход направления счета которого управляющий сигнал поступает с выхода блока 7.

Чтобы накопленньй результат интегрирования представить в виде мантиссы и порядка, счетчики 9 и 1А должны взаимодействовать следующим образом. При положительном направлении увеличение порядка происходит при переполнении счетчика 9, т.е. когда он находится в положении 1111 и поступает счетный импульс того же знака. Тогда на третьем выходе счетчика 9 появляется перенос, который поступает на второй вход счетчика 1А, увеличивая его порядок на единицу, при этом на его втором выходе появляется управляющий сигнал, которьй поступает на третий вход счетчика 9, устанавливая его старший разряд в единицу, при этом младшие разряды нули, т.е. 1000. При отрицательном направлении счета уменьшение порядка происходит, когда счетчик 9 находится в состоянии 1000 и поступает счетный импульс тог о же знака. Тогда на втором выходе счетчика 9 появляется перенос, который поступает на первый вход счетчика 1А, уменьшая его порядок на единицу, при этом на его втором выходе появляется управляющий сигнал, который устанавливает старший разряд счетчика 9 в единицу, при этом мпадшие разряды единицы, т.е. 1111.

Благодаря такому взаимодействию счетные импульсы, поступаюп ие на вход счетчика 9 с постоянной интегрирования Тр , накапливаются как результат интегрироваш1я в виде мантиссы и порядка.

Постоянная интегрирования tn , зависящая от порядков Р и Bj. , обеспечивается счетчиком 10, которьй представляет собой реверсивный счетчик, в каждом ND разряде которого имеется N счетный вход. Максимальное количество разрядов ND счетчика 10 определяется как

ND Р

хи

+ Р

гн

где и Ргл1 - максимальные значения порядков,

а количество разрядов, определяющих постоянную интегрирования Сп , номер N счетного входа счетчика 10, определяется как

Ni (Р.„ - РХ ) + Р

г

Вычитатель 15, используя значения порядков Pf, и Рд, вычисляет количество разрядов, необходимое для обеспечения постоянной интегрирования , а дешифратор 11 преобразует вычислен- ное значение в номер счетного входа счетчика 10, передавая на этот вход счетные импульсы, поступающие на второй вход дешифратора 11.

0

5

о

Формула изобретения

А-налого-дискретное интегрирующее устройство по авт. св. № 1377875, отличающееся тем, что, с целью повышения разрешающей способности при изменении интегрируемого сигнала в широком диапазоне, в него введен счетчик порядка интегрирования и вычитатель, первый вход которого является входом задания порядка входного сигнала, а второй вход подключен к информационному выходу счетчика порядка интегрирования, являющемуся дополнительным выходом устройства, выход вычитателя соединен с информационном входом дешифратора, прямой и инверсный выходы переноса ВЫХОД1ЮГО счетчика подключены к входам сложения и вычитания счетчика порядка интегрирования, выход переноса которого подключен к входу уста- новтси старшего разряда выходного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-дискретное интегрирующее устройство | 1986 |

|

SU1377875A1 |

| Аналого-дискретное интегрирующее устройство | 1975 |

|

SU556463A1 |

| Устройство для определения спектральных коэффициентов разложения случайного процесса по функциям Хаара | 1980 |

|

SU935814A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Цифроаналоговый измеритель средней частоты | 1991 |

|

SU1775678A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Способ преобразования угла поворота вала в код | 1983 |

|

SU1124358A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| СПОСОБ ОЦИФРОВКИ АНАЛОГОВОЙ ВЕЛИЧИНЫ, ОЦИФРОВЫВАЮЩЕЕ УСТРОЙСТВО, ОСУЩЕСТВЛЯЮЩЕЕ УКАЗАННЫЙ СПОСОБ, И ДЕТЕКТОР ЭЛЕКТРОМАГНИТНОГО ИЗЛУЧЕНИЯ, СОДЕРЖАЩИЙ ТАКОЕ УСТРОЙСТВО | 2008 |

|

RU2430465C2 |

Изобретение относится к аналого- цифровой вьгаи с лит ель ной технике, а именно к гибридным вычислительным устройствам, предназначенным для быстрого и точного интегрирования произвольно меняющейся функции времени. Целью изобретения является повьшение разрешающей способности при изменении интегрируемого сигнала в широком диапазоне. Поставленная цель достигается тем, что аналого-дискретное интегрирующее устройство содержит счетчик 9, вычитатель 15, счетчик 14, дешифратор 11 и счетчик 10, первый вход которого соединен с выходом блока 7 направления счета, а первый и второй выходы - соответственно с первым и вторым входами счетчика 9, первый которого подсоединен к первому выходу устройства, а второй и и третий выходы соединены соответственно с первым и вторым входами счетчика 14, второй выход которого соединен -с третьим входом счетчика 9, а первый выход подсоединен к второму выходу устройства и к первому входу вычнтателя 15, второй вход которого соединен с вторым входом устройства, а выход - с первым входом дешифратора 11; второй вход которого соединен с вторым выходом формирователя 8 счетного импульса, а выход - с вторым входом счетчика 10. 4 ил. а 4 СО О1 ОЭ со М

te.2

| Аналого-дискретное интегрирующее устройство | 1986 |

|

SU1377875A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1986-10-28—Подача