1ПГ ТНГ irif If II It

10

15

20

25

Изобретение относится к автоматике и вычислительной технике, а имение к устройствам для формирования тестовых воздействий.

Цель изобретения - расширение функциональных возможностей за счет формирования тестовых поСледователь- ностей с различными свойствами.

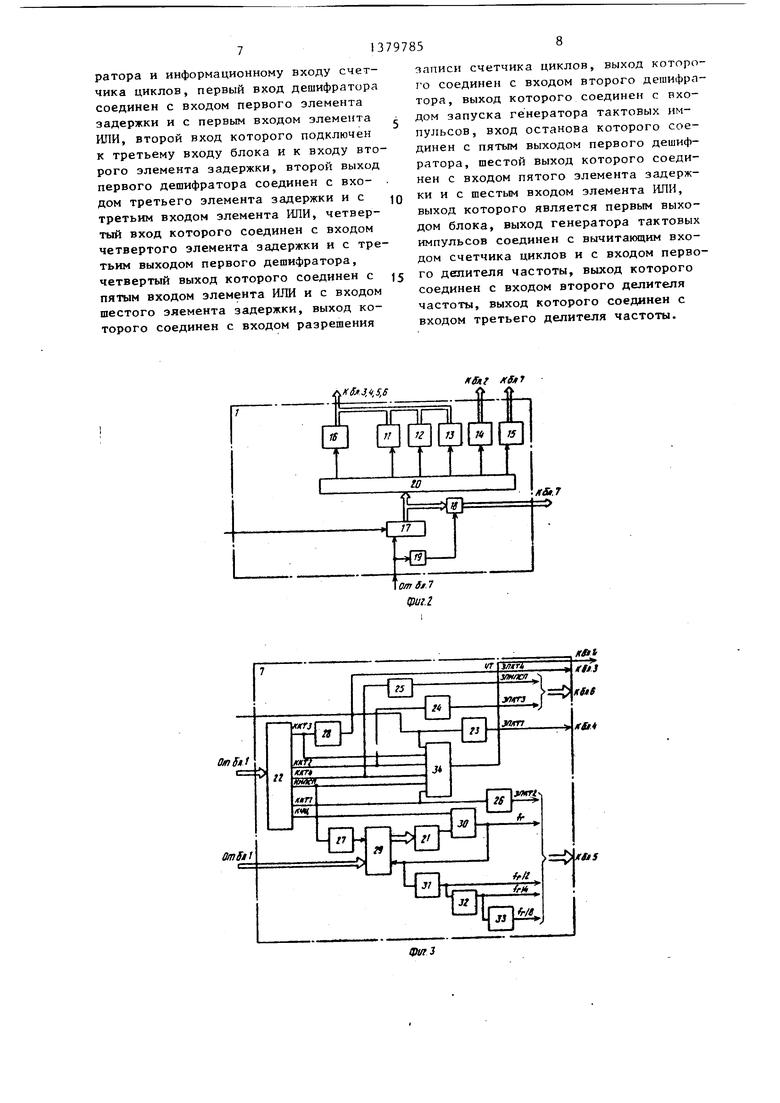

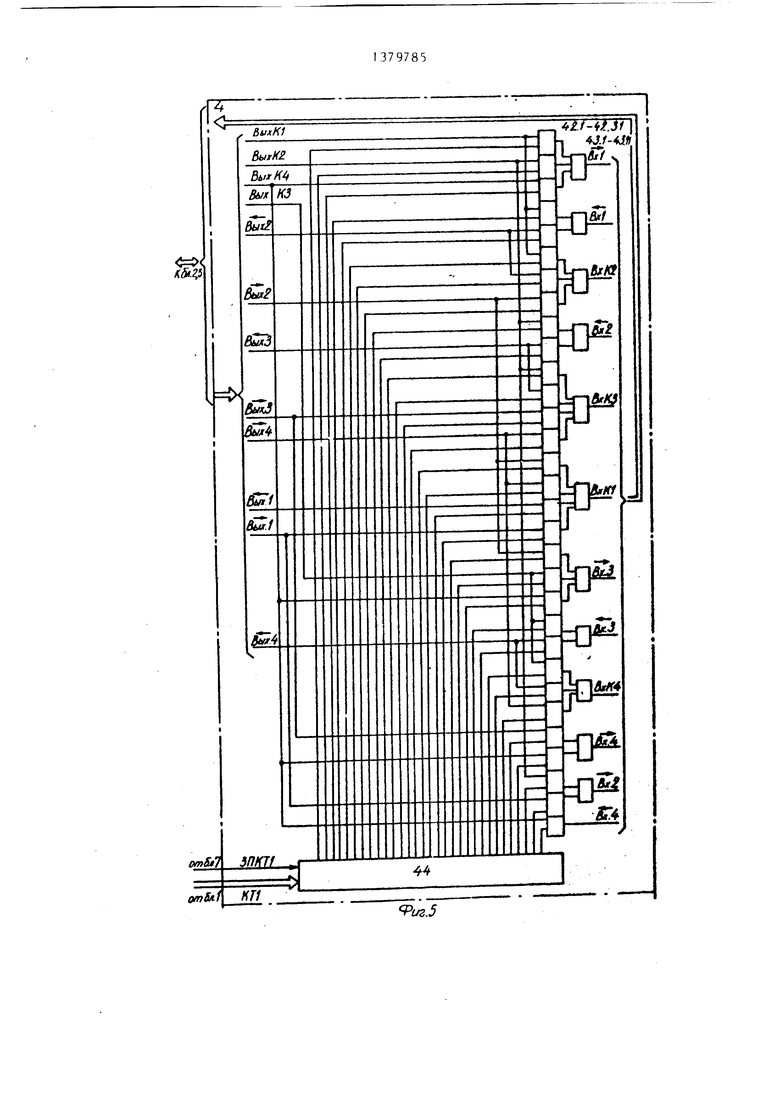

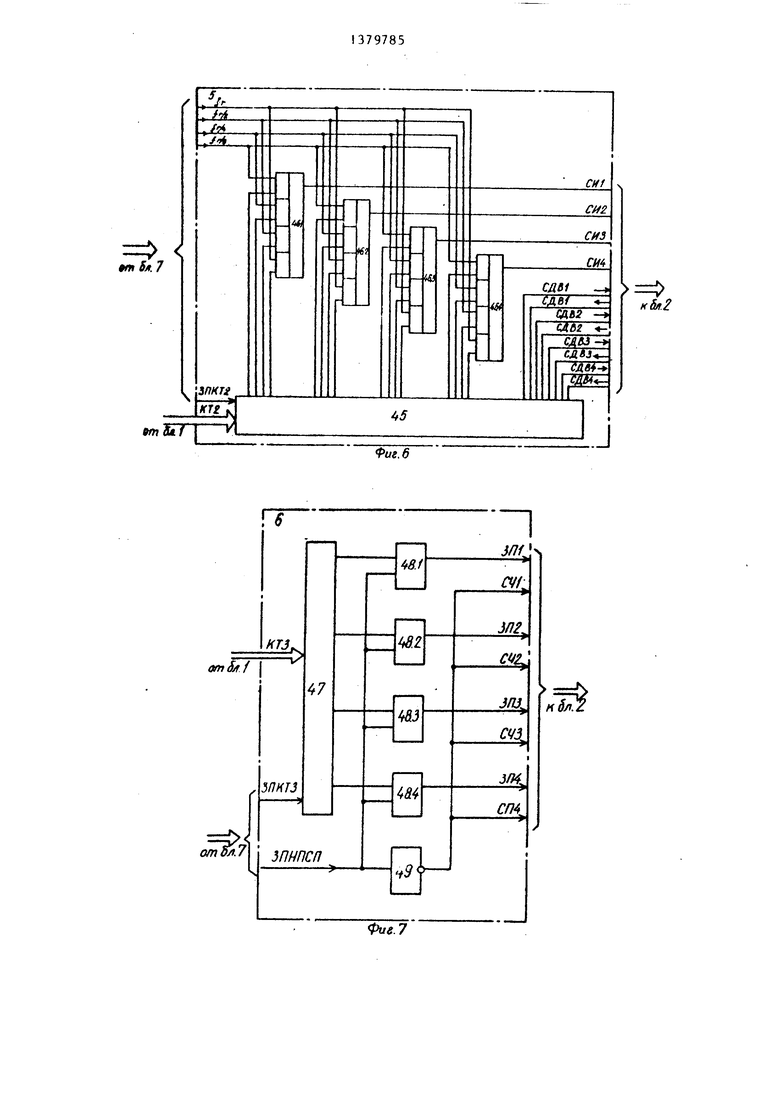

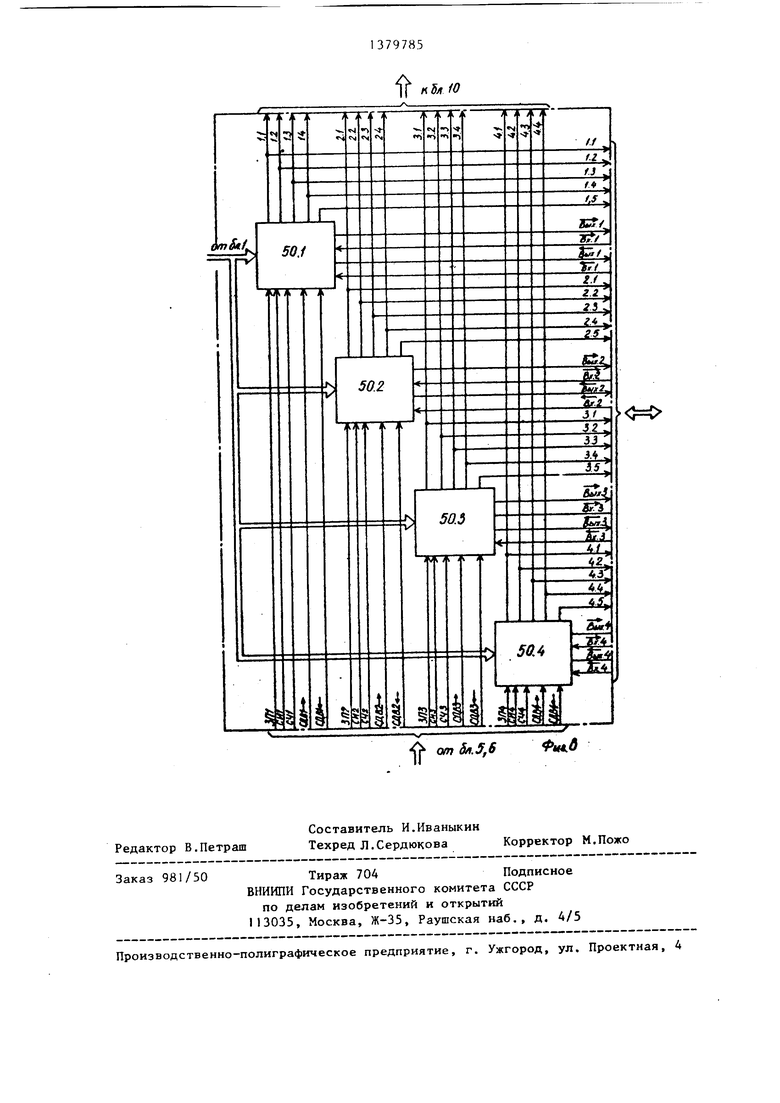

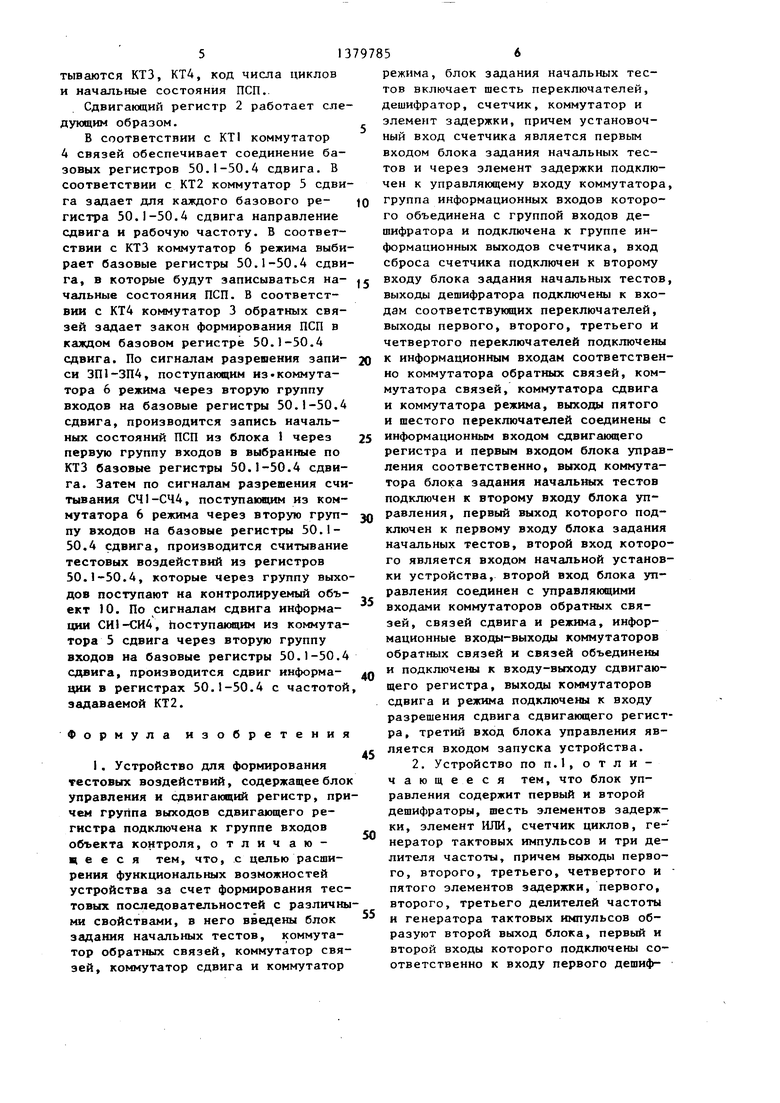

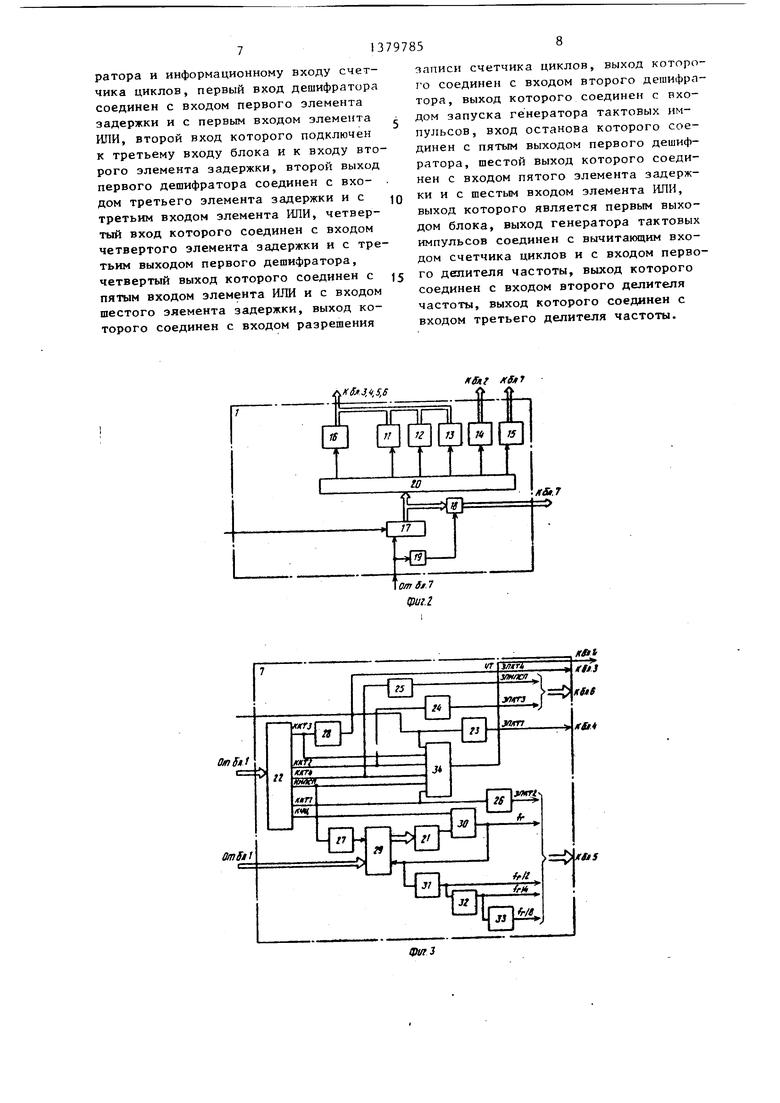

На фиг.I представлена схема устройства; на фиг.2 - схема блока задания начальных тестов; на фиг.З - схема блока управления; на фиг.4 - схема коммутатора обратных связей; на фиг.З - схема коммутатора связей; на фиг.6 - схема коммутатора сдвига; на фиг.7 - схема коммутатора режима; на фиг.8 - схема сдвигающего регистра.

Устройство для формирования тестовых воздействий содержит«блок 1 задания начальных тестов, сдвигающий регистр 2, коммутатор 3 обратных связей, коммутатор 4 связей, коммутатор 5 сдвига, коммутатор 6 режима, блок 7 управления, вход 8 начальной установки, вход 9 запуска устройства, кроме того, изображен контролируемый объект 10.

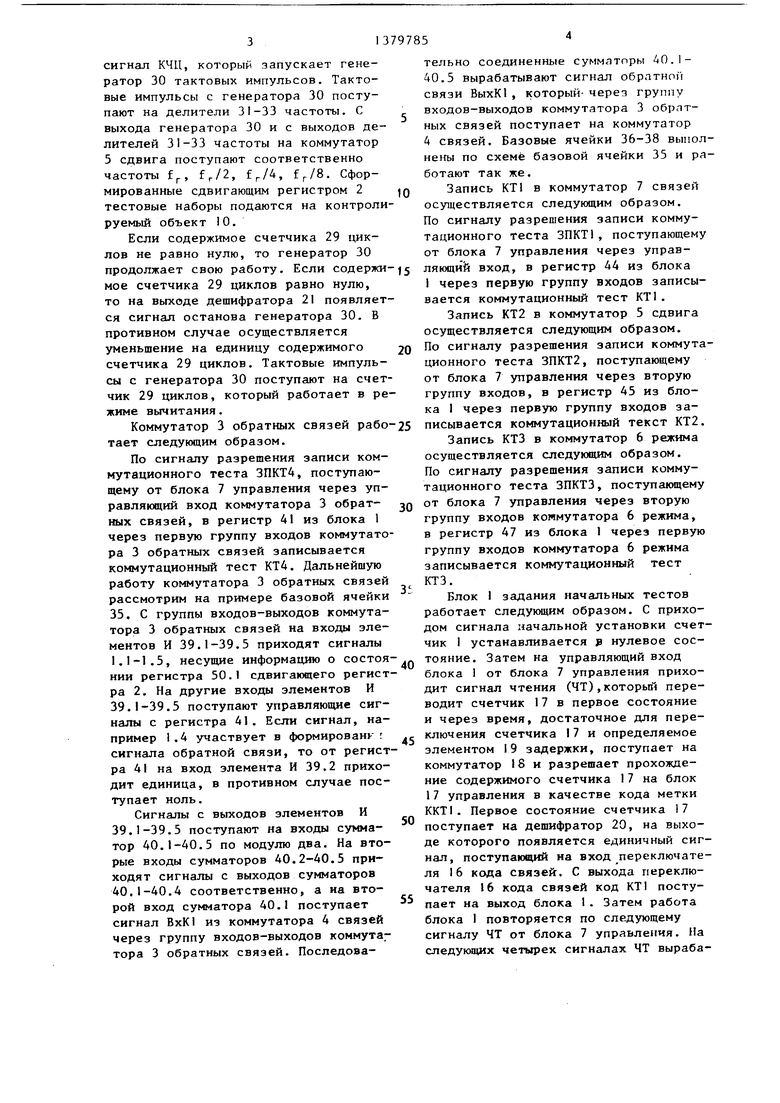

Блок 1 задания начальных тестов (фиг.2) содержит переключатели 11- 16, счетчик 17, коммутатор 18, элемент 19 задержки, дешифратор 20.

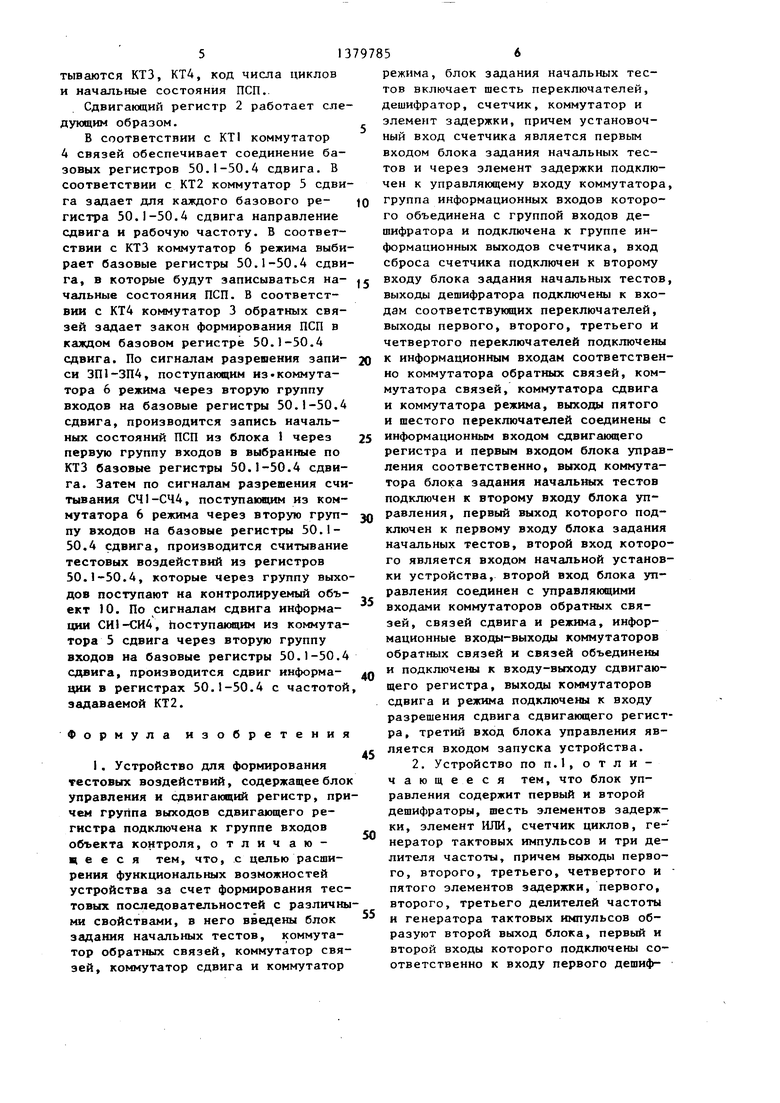

Блок 7 управления (фиг.З) содержит дешифраторы 21 и 22, элементы 23-28 задержки, счетчик 29 циклов, генератор 30 тактовых импульсов, делители 31-33 частоты, элемент ИЛИ 34.

Коммутатор 3 обратных связей (фиг.4) содержит базовые ячейки 35- 38, каждая из которых содержит элементы И 39.1-39.5 и сумматоры 40.1- 40.5 по модулю два, и регистр 41.

Коммутатор 4 связей (фиг.З) содержит элементы И 42.1-42.31, элементы «с ИЛИ 43.1-43.11 и регистр 44.

Коммутатор 5 сдвига (фиг.6) содержит регистр 45 и элементы 2И-4ИЛИ 46.1-46.4.

Коммутатор 6 режима (фиг.7) содержит регистр 47, элементы И 48.1-48.4 и элемент И-НЕ 49.

Сдвигающий регистр 2 (фиг.8) содержит базовые регистры 50.1-50.4 сдвига.

Устройство работает следующим образом.

Работа устройства начинается с записи коммутационного теста КТ1 в

13797852 коммутатор 4 связей. Сигнал запуска устройства проходит на блок 7 управления и через элемент ИЛИ 34 и элемент 23 задержки обеспечивает выдачу сигналов чтения (ЧТ) и записи КТ1 (ЗПКТ1). По этим сигналам производится считывание из блока 1 задания начальных тестов и запись в коммутатор 4 связей КТ1.

По окончании записи КТ1 в коммутатор 4 связей блок 1 вырабатывает код метки конца КТ1 (KKTI). Эта метка считывается в блок 7 управления, где дешифратор 22 вырабатывает сигнал ККТ1, который проходит через элемент ИЛИ 34 и элемент 26 задержки и обеспечивает считывание и запись КТ2 в коммутатор 5 сдвига по сигналам ЧТ и ЗПКТ2.

После считывания метки ККТ2 дешифратор 22 вырабатывает сигиал ККТ2, проходящий через элемент ИЛИ 34 и элемент 24 задержки и вызываюсций считывание и запись КТЗ в коммутатор 6 режима по сигналам ЧТ и ЗПКТЗ.

После считывания метки ККТЗ деошф- ратор 22 вырабатывает сигнал ККТЗ, проходящий через элемент ИЛИ 34 и элемент 28 задержки и вызьшающий считывание и запись КТ4 в коммутатор 3 обратных связей по сигналам ЧТ и ЗПКТ4.

После считывания метки ККТ4 дешифратор 22 вырабатывает сигнал ККТ4, проходящий через элемент ИЛИ 34 и элемент 25 задержки и вызывающий считывание и запись в выбранные по КТЗ части сдвигающего регистра 2 начального состояния ПСП по сигналам ЧТ и ЗПНПСП.

Считывание метки конца записи начального состояния ПСП (КНПСП) вызывает появление на выходе дешифратора 22 сигнала КППСП, который, пройдя через элемент ИЛИ 34, обеспечивает считывание числа циклов с блока 1. Через время, определяемое элементом 27 задержки, на счетчик 29 циклов поступает сигнал разрешения записи ин- формации ЗПСЧ в счетчик 29 циклов, по которому записывается число циклов в счетчик 29 циклов и задается временной интервал работы устройства. На этом заканчивается установка режима работы устройства.

Из задатчика блока 1 считывается код метки конца записи числа циклов (КЧ11), дешифратор 22 вырабатывает

30

35

40

50

55

сигнал КЧЦ, который запускает генератор 30 тактовых импульсов. Тактовые импульсы с генератора 30 поступают на делители 31-33 частоты. С выхода генератора 30 и с выходов делителей 31-33 частоты на коммутатор 5 сдвига поступают соответственно частоты f, fr/2, fp/4, . Сформированные сдвигающим регистром 2 тестовые наборы подаются на контролируемый объект 10.

Если содержимое счетчика 29 циклов не равно нулю, то генератор 30 продолжает свою работу. Если содержимое счетчика 29 циклов равно нулю, то на выходе дешифратора 21 появляется сигнал останова генератора 30. В противном случае осуществляется уменьшение на единицу содержимого счетчика 29 циклов. Тактовые импульсы с генератора 30 поступают на счетчик 29 циклов, который работает в режиме вычитания.

Коммутатор 3 обратных связей рабо тает следующим образом.

По сигналу разрешения записи коммутационного теста ЗПКТ4, поступающему от блока 7 управления через управляющий вход коммутатора 3 обратных связей, в регистр 41 из блока 1 через первую группу входов коммутатора 3 обратных связей записывается коммутационный тест КТ4. Дальнейшую работу коммутатора 3 обратных связей рассмотрим на примере базовой ячейки 35. С группы входов-выходов коммутатора 3 обратных связей на входы элементов И 39.1-39.5 приходят сигналы 1.1-1.5, несущие информацию о состоянии регистра 50.1 сдвигающего регистра 2. На другие входы элементов И 39.1-39.5 поступают управляющие сигналы с регистра 41. Если сигнал, например 1.4 участвует в формированк : сигнала обратной связи, то от регистра 41 на вход элемента И 39.2 приходит единица, в противном случае поступает ноль.

Сигналы с выходов элементов И 39.1-39.5 поступают на входы сумматор 40.1-40.5 по модулю два. На вторые входы сумматоров 40.2-40.5 приходят сигналы с выходов сумматоров 40.1-40.4 соответственно, а на второй вход сумматора 40.1 поступает сигнал BxKI из коммутатора 4 связей через группу входов-выходов коммутатора 3 обратных связей. Последова10

15

20

25

30

40

45

50

55

тельно соединенные сумматоры 40.1- 40.5 вырабатывают сигнал обратной связи ВыхК, который- через группу входов-выходов коммутатора 3 обрлт- ных связей поступает на коммутатор 4 связей. Базовые ячейки 36-38 выполнены по схеме базовой ячейки 35 и работают так же.

Запись КТ1 в коммутатор 7 связей осуществляется следующим образом. По сигналу разрешения записи коммутационного Теста ЗПКТ1, поступающему от блока 7 управления через управляющий вход, в регистр 44 из блока 1 через первую группу входов записывается коммутационный тест КТ1.

Запись КТ2 в коммутатор 5 сдвига осуществляется следующим образом. По сигналу разрешения записи коммутационного теста ЗПКТ2, поступающему от блока 7 управления через вторую группу входов, в регистр 45 из блока I через первую группу входов записывается коммутационный текст КТ2. Запись КТЗ в коммутатор 6 режима осуществляется следующим образом. По сигналу разрешения записи коммутационного теста ЗПКТЗ, поступающему от блока 7 управления через вторую группу входов коммутатора 6 режима, в регистр 47 из блока 1 через первую группу входов коммутатора 6 режима записывается коммутационный тест КТЗ.

Блок I задания начальных тестов работает следующим образом. С приходом сигнала начальной установки счетчик 1 устанавливается р нулевое состояние. Затем на управляющий вход блока 1 от блока 7 управления приходит сигнал чтения (ЧТ),который переводит счетчик 17 в первое состояние и через время, достаточное для переключения счетчика I7 и определяемое элементом 19 задержки, поступает на коммутатор 18 и разрешает прохождение содержимого счетчика 17 на блок 17 управления в качестве кода метки KKTI. Первое состояние счетчика 17 поступает на дешифратор 20, на выходе которого появляется единичный сигнал, поступающий на вход переключателя 16 кода связей. С выхода переключателя 16 кода связей код КТ1 поступает на выход блока 1. Затем работа блока 1 повторяется по следующему сигналу ЧТ от блока 7 управления. На следующих четырех сигналах ЧТ выраба513

тываются КТЗ, КТ4, код числа циклов и начальные состояния ПСП.

Сдвигающий регистр 2 работает следующим образом.

В соответствии с KTI коммутатор 4 связей обеспечивает соединение базовых регистров 50.1-50.4 сдвига. В соответствии с КТ2 коммутатор 5 сдвига задает для каждого базового ре- гистра 50.1-50.4 сдвига направление сдвига и рабочую частоту. В соответствии с КТЗ коммутатор 6 режима выбирает базовые регистры 50.1-50.4 сдви

режима, блок задания начальных тестов включает шесть переключателей, дешифратор, счетчик, коммутатор н элемент задержки, причем установочный вход счетчика является первым входом блока задания начальных тестов и через элемент задержки подключен к управляющему входу коммутатора группа информационных входов которого объединена с группой входов дешифратора и подключена к группе информационных выходов счетчика, вход сброса счетчика подключеи к второму

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностирования цифровых блоков | 1987 |

|

SU1548789A1 |

| Устройство для диагностирования цифровых блоков | 1988 |

|

SU1631546A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1667073A1 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

Изобретение относится к автоматике и вычислительной технике, а именно к устройствам формирования тестовых воздействий. Цель изобретения - расширение функциональных возможностей. Устройство содержит блок 1 задания начальных тестов, сдвигающий регистр 2, коммутатор 3 обратных связей, коммутатор 4 связей, коммутатор 5 сдвига, коммутатор 6 режима, блок 7 управления. Входы сдвигающего регистра 2 являются выходами устройства, выходы блока 1 задания начальных тестов соединены с входамн коммутатора 3 обратных связей, коммутатора 4 связей, коммутатора 5 сдвига, коммутатора 6 входов сдвигающего регистра. Вторая группа входов сдвигающего регистра 2 соединена с выходами коммутатора 5 сдвига и коммутатора 6 режима. Входы-выходы сдвигающего регистра 2 соединены с входами-выходами коммутатора 3 обратных связей и коммутатора 4 связей. Выходы блока управления соединены с управляющими входами коммутаторов 3-6 и блока 1 задания начальных тестов. Расширение функциональных возможностей достигается введением коммутаторов 3-6 обратных связей, связей, сдвига, режима и блока 1 задания начальных тестов, что позволяет оперативно ме- нять конфигурацию сдвигающего регистра и режим его работы, тем самым формировать тестовые последовательности с различными свойствами. 1 з.п. , 8 ил. Ш (Л со со 00 СП

га, в которые будут записываться на- входу блока задания начальных тестов.

чальные состояния ПСП. В соответствии с КТ4 коммутатор 3 обратных связей задает закон формирования ПСП в каждом базовом регистре 50.1-50.4 сдвига. По сигналам разрешения записи ЗП1-ЗП4, поступающим из«коммутатора 6 режима через вторую группу входов на базовые регистры 50.1-50.4 сдвига, производится запись начальных состояний ПСП из блока J через первую группу входов в выбранные по КТЗ базовые регистры 50.1-50.4 сдвига. Затем по сигналам разрешения считывания СЧ1-СЧ4, поступающим из коммутатора 6 режима через вторую группу входов на базовые регистры 50.1- 50.4 сдвига, производится считывание тестовых воздействий из регистров 50.1-50.4, которые через группу выходов поступают на контролируемый объект 10. По сигналам сдвига информации СИ1-СИ4, Поступающим из коммутатора 5 сдвига через вторую группу входов иа базовые регистры 50.1-50.4 сдвига, производится сдвиг информации в регистрах 50.1-50.4 с частотой, задаваемой КТ2.

Формула изобретения

I. Устройство для формирования тестовых воздействий, содержащее блок управления и сдвигающий регистр, причем группа выходов сдвигающего регистра подключена к группе входов объекта контроля, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет формирования тестовых последовательностей с различными свойствами, в него введены блок задания начальных тестов, коммутатор обратных связей, коммутатор связей, коммутатор сдвига и коммутатор

20

25

30

35

40

45

50

55

выходы дешифратора подключены к входам соответствующих переключателей, выходы первого, второго, третьего и четвертого переключателей подключены к информационным входам соответственно коммутатора обратных связей, коммутатора связей, коммутатора сдвига и коммутатора режима, выходы пятого и шестого переключателей соединены с информационным входом сдвигающего регистра и первым входом блока управления соответственно, выход коммутатора блока задания начальных тестов подключен к второму входу блока управления , первый выход которого подключен к первому входу блока задания начальных тестов, второй вход которого является входом начальной установки устройства, второй вход блока управления соединен с управляющими входами коммутаторов обратных связей, связей сдвига и режима, информационные входы-выходы коммутаторов обратных связей и связей объединены и подключены к входу-выходу сдвигающего регистра, выходы коммутаторов сдвига и режима подключены к входу разрешення сдвига сдвигающего регистра, третий вход блока управления является входом запуска устройства.

5

0

5

0

5

0

5

выходы дешифратора подключены к входам соответствующих переключателей, выходы первого, второго, третьего и четвертого переключателей подключены к информационным входам соответственно коммутатора обратных связей, коммутатора связей, коммутатора сдвига и коммутатора режима, выходы пятого и шестого переключателей соединены с информационным входом сдвигающего регистра и первым входом блока управления соответственно, выход коммутатора блока задания начальных тестов подключен к второму входу блока управления , первый выход которого подключен к первому входу блока задания начальных тестов, второй вход которого является входом начальной установки устройства, второй вход блока управления соединен с управляющими входами коммутаторов обратных связей, связей сдвига и режима, информационные входы-выходы коммутаторов обратных связей и связей объединены и подключены к входу-выходу сдвигающего регистра, выходы коммутаторов сдвига и режима подключены к входу разрешення сдвига сдвигающего регистра, третий вход блока управления является входом запуска устройства.

KKTJ

От If л

KHTf

п

Г7

fOWi

НП

1«Щ

OmSti

записи счетчика циклов, выход которого соединен с входом второго дешифратора, выход которого соединен с входом запуска генератора тактовых импульсов, вход останова которого соединен с пятым выходом первого дешифратора, шестой выход которого соединен с входом пятого элемента задержки и с шестым входом элемента ИЛИ, выход которого является первым выходом блока, выход генератора тактовых импульсов соединен с вычитающим входом счетчика циклов и с входом первого делителя частоты, выход которого соединен с входом второго делителя частоты, выход которого соединен с входом третьего делителя частоты.

,,S,Б

KSiil Хвл1

тх

Л5.7

Mffi

злнася

зпигз

зтт

fin

KM xfn

J

i

//

IS

К/

Hits

CM

c

vS

I

i

ГУ

н6л2

7

НОЛ.2

t

и 5л 10

от 5л.У,6 .б

| Дозмеров Г.М | |||

| и др | |||

| Управляемая от ЭВМ система диагностического контроля схем памяти | |||

| - Электронная про- ьшпшенность, № 2, с | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| Устройство для формирования тестовых воздействий | 1980 |

|

SU911533A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-07—Публикация

1985-04-02—Подача