со

СХ)

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1982 |

|

SU1104508A1 |

| Делительное устройство | 1983 |

|

SU1168929A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1980 |

|

SU1062713A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для умножения | 1985 |

|

SU1283750A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении различных моделирующих устройств. Целью изобретения является повышение точности датчика. Поставленная цель достигается тем, что датчик содержит регистры, блок деления, блок умножения, вычитатель и блок управления, состоящий из RS-триггеров, элементов И, элементов ИЛИ и элементов задержки. I ил.

СО

;о

Изобретение относится к вычислительной технике и может быть использовано при построении устройств для статистического моделирования.

Цель изобретения - повышение точности датчика.

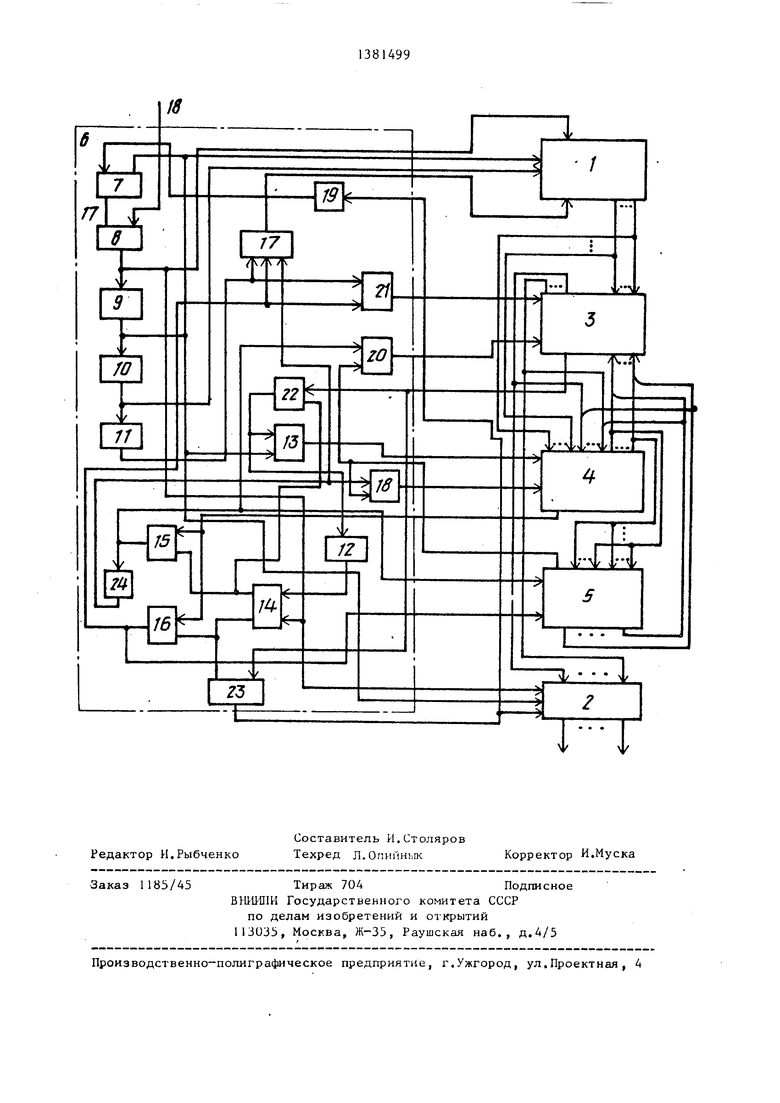

На чертеже представлена структурная схема датчика.

Датчик содержит регистр 1 памяти, регистр 2, блок 3 деления, блок 4 умножения, вычитатель 5 и блок 6 управления.

Блок Ь управления содержит RS- триггер 7, элемент И 8, элементы 9-12 задержки, элемент ШШ 13, RS- триггер 14, элементы И 15 и 16, элементы ИЛИ 17 и 18, элемент 1У задержки, элементы ШП1 20 и 21, элементы И 22 и 23, элемент 24 задержки.

Датчик работает следующим образом В исходном состоянии случайное число W находится в регистре 2.RS- триггер 7 блока 6 управления установлен в состояние, при котором на его выходе присутствует высокий уровень, свидетельствующий о том, что датчик готов к работе. Высоким уровнем подготовлен к срабатыванию элемент И 8. Число W находится в блоке 4 в качестве первого операнда. Сигнал запуска от внешнего устройства через элемент И 8 поступает на регистры 1 и 2 и на Ш-триггер 14. В регистр 1 заносится параллельным кодом константа К, 47U001 jg 011100101U1 1 1 1 1 1UOUI7. Из регистра 2 на выход датчика выдается случайно число. КБ-триггер 14 переводится в состояние, при котором на его выходе появляется высокий уровень, подготавливающий к работе элемент И 15. Сигнал запуска датчика после элемента И 8 последовательно проходит элементы 9,10 и 11 задержки. С элемента 9 задержки сигнал поступает на R-вход RS-триггера 7 и через элемент ИЛИ 13 - на вход записи блока 4 умножения. КБ-триггер 7 переводится в состояние, при котором на его выходе появляется низкий уровень, свидетельствующий о том, что датчик запущен и до окончания формирования случайного числа W элемент И 8 закрыт.Сигг

налом с выхода элемента 10 задержки в регистр 1 заносится константа

К,

11010000001000101 ц

- 999563 J- - llJIVJI JUVyV UVJlWWJWIIrtl

которая по сигналу с элемента 11 задержки заносится в блок 3 деления в

0

5

0

5

Q

0

5

качестве первого операнда. По окончании умножения на выходе конца операции блока 4 умножения появляется сигнал, который проходит через элемент И 15 на первый вход записи вычи- тателя 3 и элемент ИЛИ -20 на второй вход записи блока 3 деления, В блок 3 заносится произведение, и он запускается. Кроме того, произведение W К, заносится в качестве первого операнда в вычитатель 5, Сигнал с выхода элемента И 15 после задержки на элементе 24 задержки поступает через элементы ИЛИ 17 и 18 соответственно на первый вход чтения регистра 1 и второй вход записи блока 4 умножения. После окончания операции деления на выходе конца операции блока 3 появляется сигнал, который пройдя элемент И 22, открытый высоким уровнем с KS-триггера 14, элемент ИЛИ 13, поступает на второй вход записи блока 4 и осуществляет занесение результата деления и запуск блока 4 на выполнение второй операции умножения. С элемента И 22 сигнал через элемент 12 задержки поступает на RS-триггер 14 и переводит его в противоположное состояние. Теперь высоким уровнем по первому входу подготовлены элементы И 16 и 23, После второго умножения

г W - К результат ч по сигналу

iV J

с выхода конца операции блока 4 через элемент И 16 заносится в вычитатель 5 в качестве второго операнда и вычи- татель 5 запускается. Одновременно по сигналу с выхода элемента И 16 из регистра 1 считывается константа К И заносится в блок 3 деления в качестве первого операнда. После вычиQ

5

0

5

W

WK-K,

тания результат ,. , - „

г KI ,

К, заносится в блок

л ,

4 в качестве первого, а в блок 3 - второго операнда. Блок 3 запускается на выполнение второй операции деления. Сигнал с выхода конца операции блока 3 проходит через элемент И 23, открытый высоким уровнем с КЗ-триггера 14, на вхрд записи регистра 2

обеспечивает занесение в него случайного числа W,,, w К

того.

и

п |Inт

- Р°

этот же сигнал с выхода элемента И 23 через элемент 19 задержки по

S-входу переводит KS-триггер 7 в состояние, при котором на его выходе появляется высокий уровень, открывающий по первому входу элемент И 8 и свидетельствующий о готовности датчика к выдаче случайного числа

W h-n

Формула изобретения

Датчик равномерно распределенных случайных чисел, содержащий регистр памяти, выход которого является выходом датчика, отли чающий- с я тем, что, с целью повышения точ ности, он содержит регистр, блок деления, блок умножения,, вычитатель и блок управления, который содержит два RS-триггера, пять элементов И, пять элементов ИЛИ, шесть элементов задержки, причем выход первого элемента И блока управления через последовательно соединенные второй и третий элементы задержки соединен с первым входом первого элемента ИЛИ,вто- рой вход которого соединен с выходом второго элемента И, первый вход которого соединен с первым входом третьего элемента И и подключен к выходу конца операции блока умноже- ния, выход третьего элемента И через четвертый элемент задержки соединен с третьим входом первого элемента ШШ, выход которого соединен с первым входом чтения регистра, выход первого RS-триггера соединен с первым входом первого элемента И,второй вход которого является входом Пуск датчика, R-вход первого RS-триггера

соединен с выходом первого элемента

задержки,и с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с прямым выходом второго RS-тpиг гера и подключен к второму входу третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с первым входом четвертого элемента ИЛИ и подключен к выходу конца операции вычитателя, второй вход четвертого элемента ИЛИ соединен с выходом четвертого элемента задержки, второй вход четвертого элемента И соединен с первым входом пятого элемента И и подключен к выходу конца операции блока деления, вто

|п

j 20 25 -jo

35

40

д5

0

5

рой вход пятого элемента И соединен с инверсным выходом второго RS- триггера и подключен к второму входу второго элемента И, S-вход второго RS-триггера соединен с выходом первого элемента И, Н-вход второго RS- триггера соединен с выходом пятого элемента задержки, вход которого соединен с выходе четвертого элемента И, первый вход первого элемента ИЛИ соединен с первым входом пятого элемента ШШ и подключен к выходу третьего элемента задержки, второй вход пятого элемента ИЛИ соединен с вторым входом первого элемента ИЛИ, выход шестого элемента задержки подключен к S-входу первого RS-триггера, выход первого элемента И блока управления соединен с первым входом записи регистра, выход которого соединен с первым информационным входом блока деления и с первым информационным входом блока умножения, выход первого элемента задержки соединен с вторым входом чтения регистра,второй вход записи которого соединен с выходом второго элемента задержки блока управления, выход блока деления соединен с вторым информационным входом блока умножения, выход которого соединен с вторым информационным входом блока деления, выход пятого элемента ИЛИ блока соединен с первым входом записи блока деления, второй вход записи которого соединен с выходом третьего элемента ИЛИ блока управления, информацион11ый выход блока умножения соединен с первым и вторым информационными входами вычитателя, выход которого подключен к второму информационному входу блока деления, первый вход записи вычита- теля соединен с выходом третьего элемента И блока управления, второй вход записи вычитателя соединен с выходом второго элемента И блока управления, выход блока деления соединен с информационным входом регистра памяти, вход чтения которого соединен с S- входом второго RS-триггера блока управления, вход обнуления регистра памяти соединен с выходом первого элемента задержки блока управления, вход записи регистра памяти соединен с выходом пятого элемента И блока управления и входом шестого элемента задержки блока управления.

i-l

| ГЕНЕРАТОР РАВНОМЕРНО РАСПРЕДЕЛЕННЫХ СЛУЧАЙНЫХ ВЕЛИЧИН | 1973 |

|

SU430400A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор равномерно распределенных случайных чисел | 1985 |

|

SU1256023A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1985-11-29—Подача