Изобретение относится к автоматике и вычислительной технике и предназначено для сравнения трех двоичных чисел с выбором максимального, минимального или среднего из них.

Цель изобретения - расширение функциональных возможностей за счет определения минимального из сравниваемых чисел.

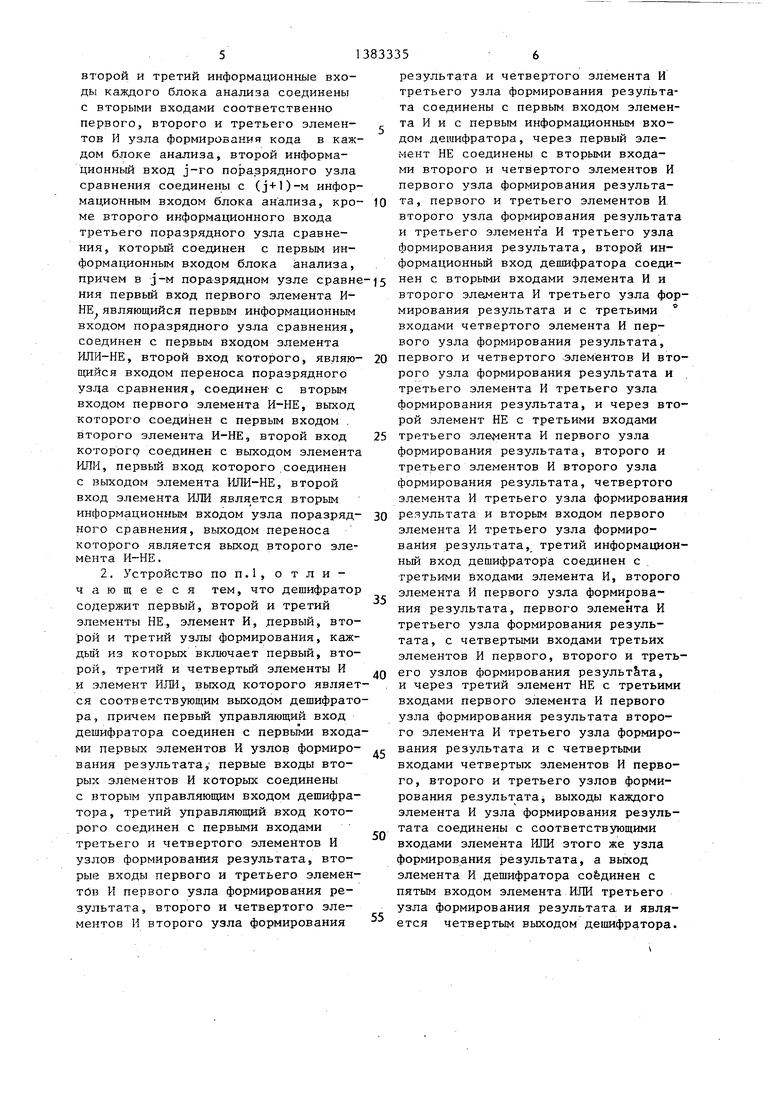

На фиг.1 представлена структурная схема устройства для сравнения чисел; на фиг.2 - функциональная схема i-ro блока анализа; на фиг.З - схема дешифратора.

Устройство содержит п блоков 1,,I,...,1 анализа, информационные входы 2-4 сравниваемых чисел А,В,С соответственно, дешифратор 5, входы 6-8 управления (m,n,k),ши- ну 9 логической единицы, первые информационные выходы 10 устройства, второй выход 1 устройства равенства чисел, выходы 12-14 дешифратора 5.

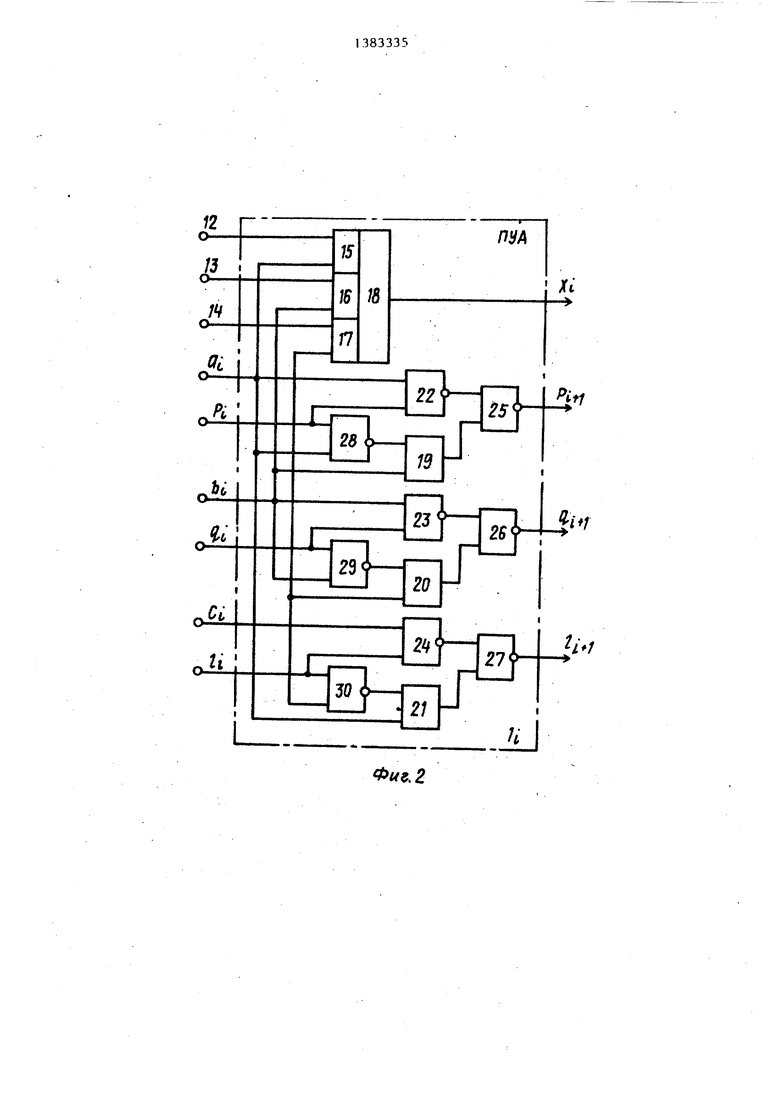

Первый блок анализа содержит узел формирования кода, состоящий из элементов И 15 - 17 и элемента ИЛИ 18, первый , второй и третий поразрядные узлы сравнения, состоящие соответственно из элементов ИЛИ 19 - 21, первых 22 - 24 и вторых 25 - 27 элементов И-НЕ и элементов ИЛИ-НЕ 28 - 30.

Дешифратор содержит элементы НЕ 31 - 33, элемент И 34, первый, второй и третий узлы формирования результата, состоящие соответственно из первых 35 - 37, вторых 38 - 40 третьих 41 - 43 и четвертых 44 - 46 элементов И, элементов ИЛИ 47 - 49.

Устройство работает следующим образом.

Последовательно включеннь;е поразрядные узлы сравнения блоков 1, , 1,2 , ... , 1 fi анализа представляют со- бой собственно схемы сравнения пар сравниваемых чисел А и В, В и С, Си А. Эти схемы попарного сравнения чисел на своих выходах Р,,, 1 (, + ( переноса вырабатывают сигналь: логической единицы, если первое число пары больше или равно второму числу пары, и сигнал логического нуля, если первое число меньше второго.

Принцип работы схемы сравнения заключается в том, что результат сравнения кодов чисел определяется, начиная от старших разрядов. Если старпше разряды пары чисел имеют на

г

0

5

20

25 ЗО

Q

5 п

35

5

своих информационных входах сигналы разного уровня, то результат сравнения определяется состоянием выхода последнего поразрядного узла сравнения р„, (q „, Дп, ),т.е., если на информационном входе первого числа пары сигнал логической единицы (нуля , а на информационном входе вто. рого числа пары - логический нуль (единица), то на выходе последнего узла поразрядного сравнения сигнал логической единицы (нуля) независимо от сигнала на входе переноса последнего узла поразрядного сравнения p(-q,l). Если на информационных входах последнего сравнения одинако - вые уровни сигналов, то на его выход Рц41 (Чп4г И4 передается сигнал, присутствующий на входе p(q, 1) переноса. Если же часть старших разрядов сравниваемых чисел равна то выход схемы сравнения, определяется выходом ближайшего к концу пораз-- рядного узла сравнения, на информационных входах которого разные уровни сигналов. Если сравниваемые числа равны, то единичный сигнал с шины 9 логической единицы передается на вькод P,,(q,,, 1„„).

Комбинация выходных сигналов РПМ Чп + 1 if выходах схем сравнения несет информацию о соотношении между сравниваемыми числами. Поэтому выходные сигналы р„,, .мк nocTjmaioT на информационные входы дешифратора, который в соответствии с заданием определяет число, которое посылается на информационный выход 10 устройства X заданием является выбор максимального, минимального или среднего чисел). Выделение максимального, минимального или среднего значений из сравниваемых чисел осуществляется с помощью сигналов на управляющих входах 6-8 устройства ,

Для выделения максимального значения по входу 6 управления устройства подается сигнал логической единицы на вход m дешифратора 5, при этом на входах n,k дешифратора - сигналы логического нуля, Дпя выделения минимального значения из сравниваемых чисел сигнал логической единицы подается по входу 7 управления устройства, который поступает на вход п дешифратора 5 при этом m k 0. Для выделения среднего

значения по входу 8 управления устройства поступает сигнал логической единицы на вход k дешифратора (т п 0).

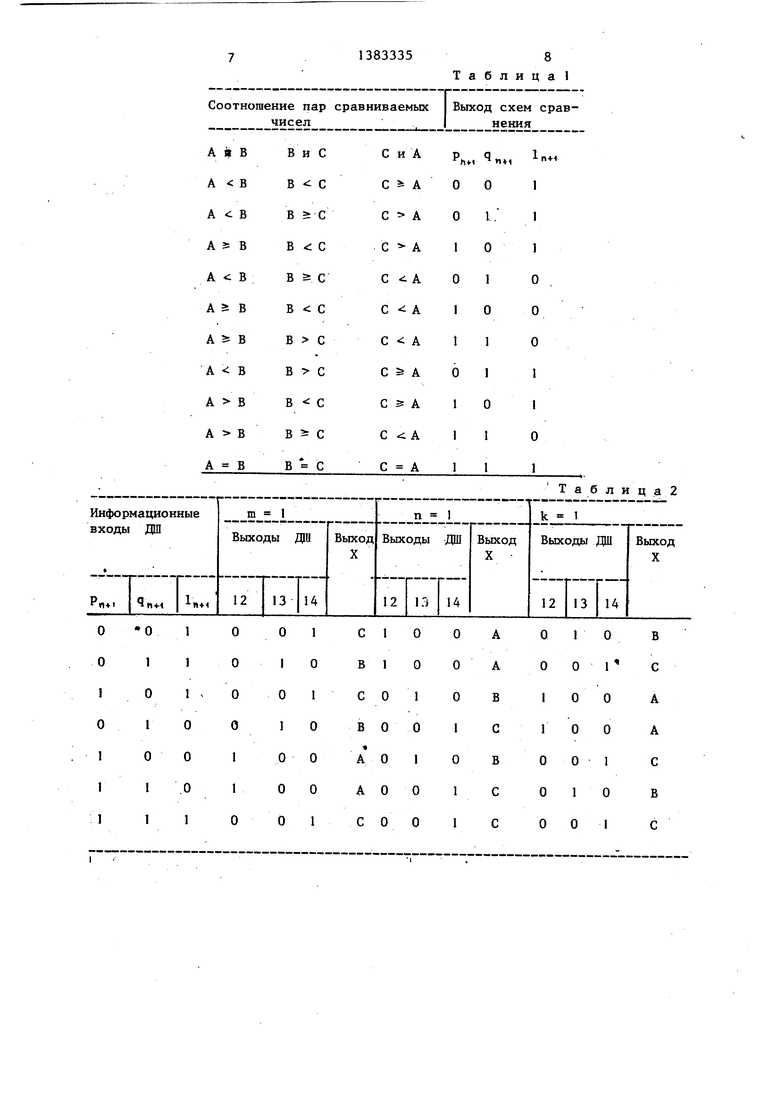

В табл. 1 приведены логические уровни сигналов на выходах переноса схем сравнения .пар сравнивае- мых чисел р„,, , q, , 1„, в зависимости от соотношения между сравниваемыми числами.

В табл.2 приведены логические уровни сигналов на выходах 12-14 дешифратора 5 и число на информационном выходе 10 устройства X в зави- симости от состояния информационных входов Phu q ПЧ1 Inti и управляю- щнх входов m,n, k дешифратора.

Сигнал логической единицы присутствует одновременно на всех инфор- мационных входах р,, q,, 1, дешифратора 5 лишь в одном случае, когда сравниваемые числа равны друг другу . Этот случай выделяется на элементе И 34 дешифратора, с. которого единичный сигнал следует на третий управляющий выход дешифратора 14 и на выход 1 1 устройства.

Группа выходов 12 - 14 дешифрато- ра следует на управляющие входы блоков 1, ,1,...,1„ анализа и определяет какое из сравниваемых чисел передавать на информационный выход устройства X. Если возбужден выход 12 дешифратора, то на выход X устройства передается число А,если возбужден выход 13 - число В, выход 14 число С.

При равенстве трех чисел

возбуждается выход 14 дешифратора, с выхода элемента И 34 через элемент ИЛИ 49 и на выход X устройства передается число С (в этом случае, в принципе, на выход X устройства можно передавать любое из сравниваемых чисел.

Формула изобрет е н и я

1. Устройство для сравнения чисел, содержащее п блоков анализа, где п - разрядность уравниваемых чисел, каждый из которых включает узел формирования кода, содержащий первый, второй и третий элементы И и элемент ИЛИ, первый, второй и третий поразрядные узлы сравнения, каждый из ко

5

0 5

о

0

-

5

0

торых включает элемент ИЛИ, причем первый, второй и третий информационные входы каждого блока анализа являются входами соответствующего разряда первого, второго и третьего чисел устройства соответственно, в каждом блоке анализа первый, второй и третий информационные входы соединены с первыми информационными входами первых, вторых и третьих поразрядных узлов сравнения соответственно, первые входы управления блоков анализа объединены, первый, второй и третий выходы переноса i-ro блока анализа, являющиеся выходами переноса соответствующих поразрядных узлов сравнения, где i 1,2,...,п-1, соединены соответ,ственно с первым, вторым и третьим входами переноса (i+l)-ro блока анализа, являющиеся соответственно входами переноса первого, второго и третьего .поразрядных узлов сравнения, входы переноса пер- вого блока анализа соединены с входами логической единицы устройства, выходы элементов ИЛИ узлов формирования кода блоков анализа являются /информационными выходами устройства, в каждом узле формирования кода выходы первого, второго и третьего элементов И соединены с входами элемента ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей за счет определения минимального из сравниваемых чисел, в него введен дешифратор, в каждый j-и поразрядный узел сравнения, где j 1,2,3, каждого блока анализа введены первый и второй элементы И-НЕ и элемент ИЛИ-НЕ, причем первый выход дешифратора соединен с первьми входами управления блоков анализа, в каждом блоке анализа первый вход управлении соединен с первым входом первого элемента И узла формирования кодов, второй и третий выходы дешифратора соединены с первыми входами соответственно второго и третьего элементов И узлов формирования кодов всех блоков анализа, выходы переноса п-го блока анализа соединены с соответствующими информационными входами дещифратора первый, второй и третий управляющие входы которого являются входами задания режима устройства, четвертый выход дешифратора является выходом равенства чисел устройства, первый

второй и третий информационные входы каждого блока анализа соединены с вторыми входами соответственно первого, второго и третьего элементов И узла формирования кода в каждом блоке анализа, второй информационный вход j-ro поразрядного узла сравнения соединены с (j+l)-M информационным входом блока анализа, кроме второго информационного входа третьего поразрядного узла сравнения, который соединен с первым информационным входом блока анализа, причем в J-M поразрядном узле сравне НИН первый вход первого элемента И- НЕ являющийся первым информационным входом поразрядного узла сравнения, соединен с первым входом элемента ИЛИ-НЕ, второй вход которого, являющийся входом переноса поразрядного узда сравнения, соединен с вторым входом первого элемента И-НЕ, выход которого соединен с первым входом . второго элемента И-НЕ, второй вход которогр соединен с выходом элемента ИЛИ, первьш вход которого .соединен с выходом элемента ИЛИ-НЕ, второй вход элемента ИЛИ вторым информационным входом узла поразрядного сравнения, выходом переноса которого является выход второго элемента И-НЕ.

2. Устройство по П.1, о т л и - чающееся тем, что дешифратор содержит первый, второй и третий элементы НЕ, элемент И, первый, второй и третий узлы формирования, каж- дьш из которых включает первый, второй, третий и четвертый элементы И и элемент ИЛИ, выход которого является соответствзгющим выходом дешифратора, причем первьй управляющий вход дешифратора соединен с первьми входами первых элементов И узлов формирования результата, первые входы вторых элементов И которых соединены с вторым управляющим входом дешифратора, третий управляющий вход которого соединен с первыми входами третьего и четвертого элементов И узлов формирования результата, вторые входы первого и третьего элементов И первого узла формирования результата, второго и четвертого элементов И второго узла формирования

10

15

20

25

30

35

40

45

50

55

результата и четвертого элемента И третьего узла формирования результата соединены с первым входом элемента И и с первым информационным входом дешифратора, через первый элемент НЕ соединены с вторыми входами второго и четвертого элементов И первого узла формирования результата, первого и третьего элементов И второго узла формирования результата и третьего элемент а И третьего узла формирования результата, второй информационный вход дешифратора соединен с вторыми входами элемента И и второго элемента И третьего узла формирования результата и с третьими входами четвертого элемента И первого узла формирования результата, первого и четвертого элементов И второго узла формирования результата и третьего элемента И третьего узла формирования результата, и через второй элемент НЕ с третьими входами третьего элемента И первого узла формирования результата, второго и третьего элементов И второго узла формирования результата, четвертого элемента И третьего узла формирования результата и вторым входом первого элемента И третьего узла формирования результата, третий информационный вход дешифратор а соединен с третьими входами элемента И, второго элемента И первого узла формирования результата, первого элемента И третьего узла формирования результата, с четвертыми входами третьих элементов И первого, второго и третьего узлов формирования результата, и через третий элемент НЕ с третьими входами первого элемента И первого узла формирования результата второго элемента И третьего узла формирования результата и с четвертыми входами четвертых элементов И первого, второго и третьего узлов формирования результата, выходы каждого элемента И узла формирования результата соединены с соответствующими входами элемента ИЛИ этого же узла формирования результата, а выход элемента И дещифратора соединен с пятым входом элемента ИЛИ третьего узла формирования результата и является четвертым выходом дешифратора.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для упорядочивания @ чисел | 1982 |

|

SU1062687A1 |

| Устройство для выбора упорядоченной последовательности данных | 1983 |

|

SU1109738A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для определения экстремального из @ чисел | 1984 |

|

SU1171779A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Устройство для сравнения весов кодов | 1979 |

|

SU798810A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для сравнения трех двоичных чисел с выбором максимального, минимального или среднего из них. Цель изобретения - расширение функциональных возможностей за счет определения минимального из сравниваемых чисел. Устройство содержит п блоков 1(- 11, анализа, информационные входы 2 - 4, входы 6-8 управления и дешифратор 5, каждый блок анализа содержит узел формирования кода, состоящий из трех элементов И и элементы ИЛИ, и трех поразрядных узлов сравнения, каждый из которых содержит два элемента И-НЕ, элементы .ИЛИ, НЕ, а депшфра- тор содержит три элемента НЕ, элемент И и три узла формирования результата, каждый из которых состоит из четырех элементов И и элемента ИЛИ. Устройство для сравнения чисел за счет попарного сравнения чисел на схемах сравнения, состоящих из поразрядных узлов сравнения, заключенных в блоки анализа и последующего дешифрирования состояний выходов переноса попарных схем сравнения в зависимости от задания, позволяет выбрать либо максимальное, либо минимальное, либо среднее значение из . сравниваемкх чисел. 1 з.п. ф-лы, 3 ил., 2 табл. сл

Т а б л и ц а 2

иг, Z

/

11

Фиг.З

| Устройство для выбора экстремальногочиСлА | 1977 |

|

SU809163A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сравнения чисел | 1980 |

|

SU949651A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-17—Подача