(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Тестопригодный сумматор | 1987 |

|

SU1522214A1 |

| СПОСОБ ТЕСТОПРИГОДНОЙ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 2008 |

|

RU2413282C2 |

| СПОСОБ ТЕСТОПРИГОДНОСТИ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 2011 |

|

RU2497182C2 |

| Управляемый @ -триггер | 1982 |

|

SU1081777A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2279184C2 |

| Устройство для обработки реакции логических блоков | 1990 |

|

SU1725221A1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1059630A1 |

| @СЕСОЮЗН*.Я | 1973 |

|

SU378919A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении тестопригодных устройств обработки цифровой информации. Целью изобретения является повышение быстродействия проверки разрядов регистра. Для этого в каж дый разряд регистра введены элемент ИЛИ и элемент РАВНОЗНАЧНОСТЬ, что позволяет определять техническое состояние регистра по выходу последнего разряда. Предлагаемый регистр приспособлен к ускоренному поиску места возникновения дефекта. В предлагаемом регистре возможно наращивание разрядности регистра без внесения дополнительной аппаратуры и без изменения системы диагностирования, что особенно важно при интегральном исполнении. 1 ил.

со

00

со

4

СО

Изобретение относится к вычислительной -ехнике и может быть использовано при 1 остроении тестопригодНых устройств обработки цифровой информации.

Цель изобретения - повышение быстродействия проверки регистра.

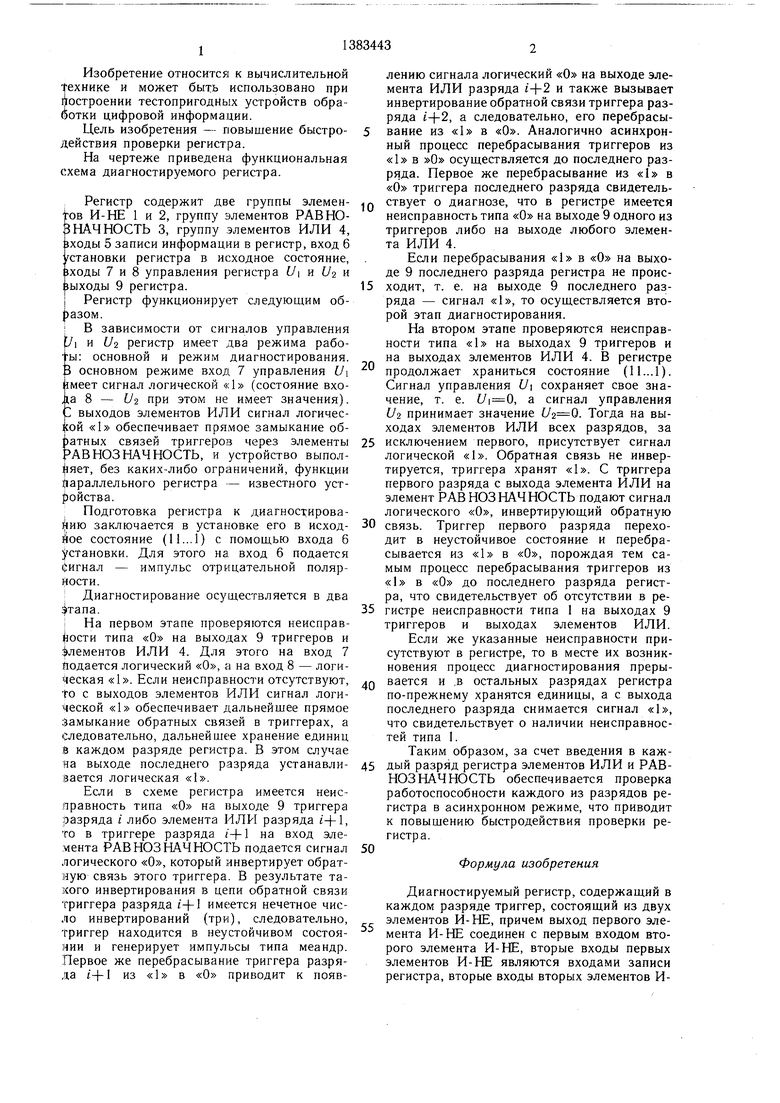

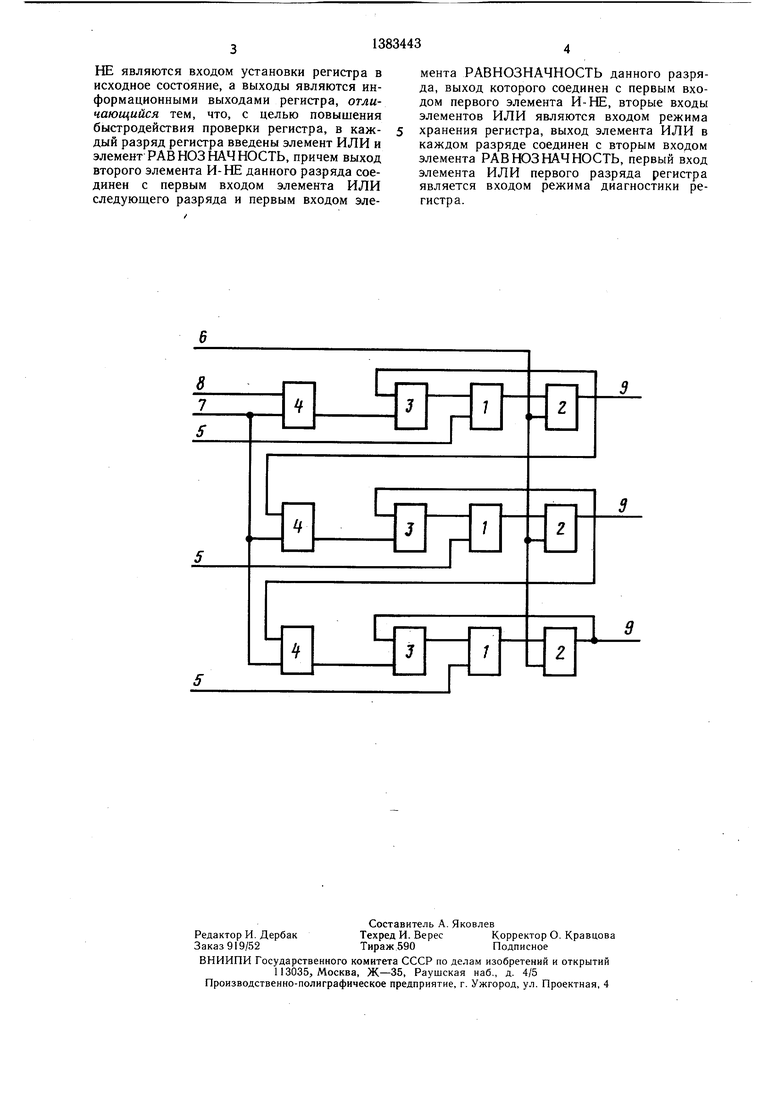

На чертеже приведена функциональная схема диагностируемого регистра.

Регистр содержит две группы элементов И-НЕ 1 и 2, группу элементов РАВНОЗНАЧНОСТЬ 3, группу элементов ИЛИ 4, :5ходы 5 записи информации в регистр, вход 6 установки регистра в исходное состояние, иходы 7 и 8 управления регистра f/i и i/2 и иыходы 9 регистра.

I Регистр функционирует следующим об- |)азом.

i В зависимости от сигналов управления 7i и f/2 регистр имеет два режима работы: основной и режим диагностирования. 3 основном режиме вход 7 управления 11 имеет сигнал логической «1 (состояние входа 8 - Uz при этом не имеет значения). С выходов элементов ИЛИ сигнал логичес- 1ШЙ «1 обеспечивает прямое замыкание об- )атных связей триггеров через элементы :РАВНОЗНАЧНОСТЬ, и устройство выпол- яет, без каких-либо ограничений, функции Параллельного регистра - известного уст- |)ойства.

Подготовка регистра к диагнос1;ирова- 1)(ию заключается в установке его в исход- йое состояние (11...1) с помощью входа 6 установки. Для этого на вход 6 подается (Сигнал - импульс отрицательной полярности.

; Диагностирование осуществляется в два $тапа.

На первом этапе проверяются неисправ- Йости типа «О на выходах 9 триггеров и Элементов ИЛИ 4. Для этого на вход 7 Додается логический «О, а на вход 8 - логическая «1. Если неисправности отсутствуют, to с выходов элементов ИЛИ сигнал логической «1 обеспечивает дальнейшее прямое замыкание обратных связей в триггерах, а Следовательно, дальнейшее хранение единиц в каждом разряде регистра. В этом случае «а выходе последнего разряда устанавливается логическая «1.

Если в схеме регистра имеется неисправность типа «О на выходе 9 триггера разряда / либо элемента ИЛИ разряда г+1, то в триггере разряда на вход элемента РАВНОЗНАЧНОСТЬ подается сигнал логического «О, который инвертирует обратную связь этого триггера. В результате такого инвертирования в цепи обратной связи триггера разряда /+1 имеется нечетное число инвертирований (три), следовательно, триггер находится в неустойчивом состоянии и генерирует импульсы типа меандр. Первое же перебрасывание триггера разряда г+1 из «1 в «О приводит к появлению сигнала логический «О на выходе элемента ИЛИ разряда i+2 и также вызывает инвертирование обратной связи триггера разряда г+2, а следовательно, его перебрасывание из «1 в «О. Аналогично асинхронный процесс перебрасывания триггеров из «1 в 0 осуществляется до последнего разряда. Нервое же перебрасывание из «1 в «О триггера последнего разряда свидетельQ ствует о диагнозе, что в регистре имеется неисправность типа «О на выходе 9 одного из триггеров либо на выходе любого элемента ИЛИ 4.

Если перебрасывания «1 в «О на выходе 9 последнего разряда регистра не происходит, т. е. на выходе 9 последнего разряда - сигнал «1, то осуществляется второй этап диагностирования.

На втором этапе проверяются неисправности типа «1 на выходах 9 триггеров и на выходах элементов ИЛИ 4. В регистре продолжает храниться состояние (11...1). Сигнал управления U сохраняет свое значение, т. е. , а сигнал управления Uz принимает значение . Тогда на выходах элементов ИЛИ всех разрядов, за

5 исключением первого, присутствует сигнал логической «1. Обратная связь не инвертируется, триггера хранят «1. С триггера первого разряда с выхода элемента ИЛИ на элемент РАВНОЗНАЧНОСТЬ подают сигнал логического «О, инвертирующий обратную

0 связь. Триггер первого разряда переходит в неустойчивое состояние и перебрасывается из «1 в «О, порождая тем самым процесс перебрасывания триггеров из «1 в «О до последнего разряда регистра, что свидетельствует об отсутствии в ре5 гистре неисправности типа 1 на выходах 9 триггеров и выходах элементов ИЛИ. Если же указанные неисправности присутствуют в регистре, то в месте их возникновения процесс диагностирования прерыQ вается и ,в остальных разрядах регистра по-прежнему хранятся единицы, а с выхода последнего разряда снимается сигнал «1, что свидетельствует о наличии неисправностей типа I.

Таким образом, за счет введения в каж5 дый разряд регистра элементов ИЛИ и РАВНОЗНАЧНОСТЬ обеспечивается проверка работоспособности каждого из разрядов регистра в асинхронном режиме, что приводит к повышению быстродействия проверки регистра.

0

Формула изобретения

Диагностируемый регистр, содержащий в каждом разряде триггер, состоящий из двух элементов И-НЕ, причем выход первого элемента И-НЕ соединен с первым входом второго элемента И-НЕ, вторые входы первых элементов И-НЕ являются входами записи регистра, вторые входы вторых элементов ИНЕ являются входом установки регистра в исходное состояние, а выходы являются информационными выходами регистра, отличающийся тем, что, с целью повышения быстродействия проверки регистра, в каждый разряд регистра введены элемент ИЛИ и элемент РАВНОЗНАЧНОСТЬ, причем выход второго элемента И-НЕ данного разряда соединен с первым входом элемента ИЛИ следующего разряда и первым входом элемента РАВНОЗНАЧНОСТЬ данного разряда, выход которого соединен с первым входом первого элемента И-НЕ, вторые входы элементов ИЛИ являются входом режима хранения регистра, выход элемента ИЛИ в каждом разряде соединен с вторым входом элемента РАВНОЗНАЧНОСТЬ, первый вход элемента ИЛИ первого разряда регистра является входом режима диагностики регистра.

г-Г -

| Уильяме Т | |||

| У., Перкер К | |||

| П | |||

| Проектирование контролируемых устройств.- ТИИЭР, т | |||

| Контрольный стрелочный замок | 1920 |

|

SU71A1 |

| Самофалов К | |||

| Г | |||

| и др | |||

| Цифровые электронные вычислительные машины.-Киев: Вища школа, 1983, с | |||

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

Авторы

Даты

1988-03-23—Публикация

1986-03-12—Подача