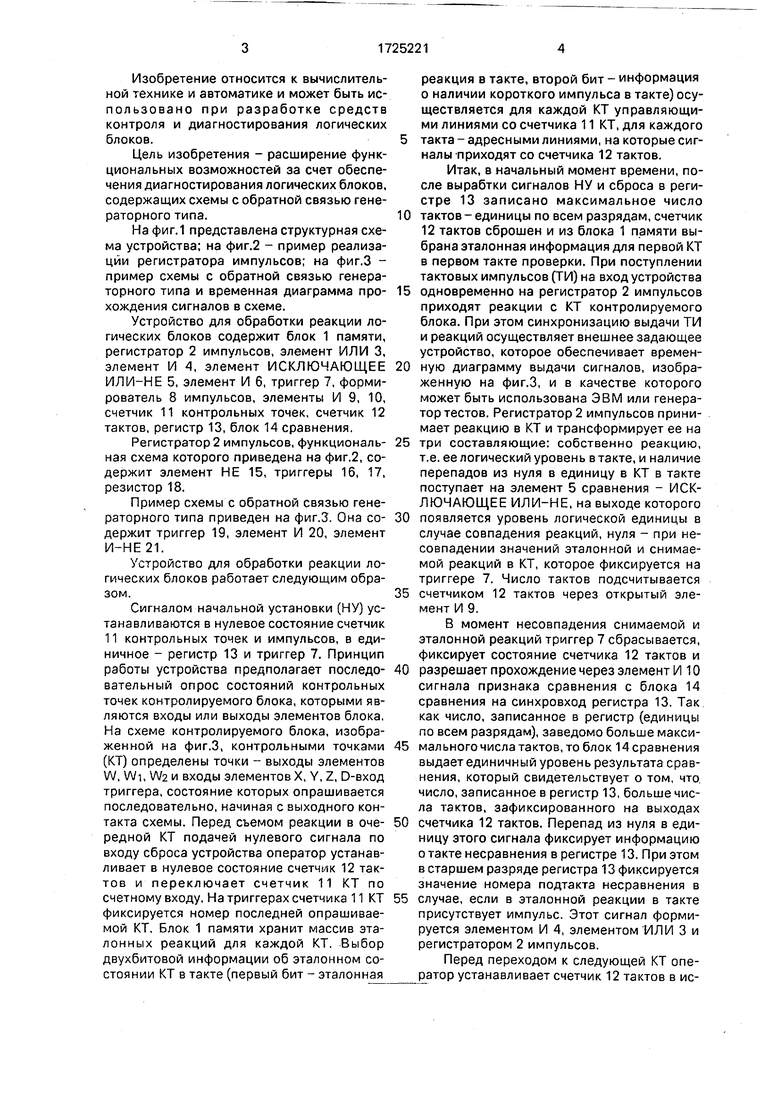

Фиг.1

Изобретение относится к вычислительной технике и автоматике и может быть ис- пользовано при разработке средств контроля и диагностирования логических блоков.

Цель изобретения - расширение функциональных возможностей за счет обеспечения диагностирования логических блоков, содержащих схемы с обратной связью генераторного типа.

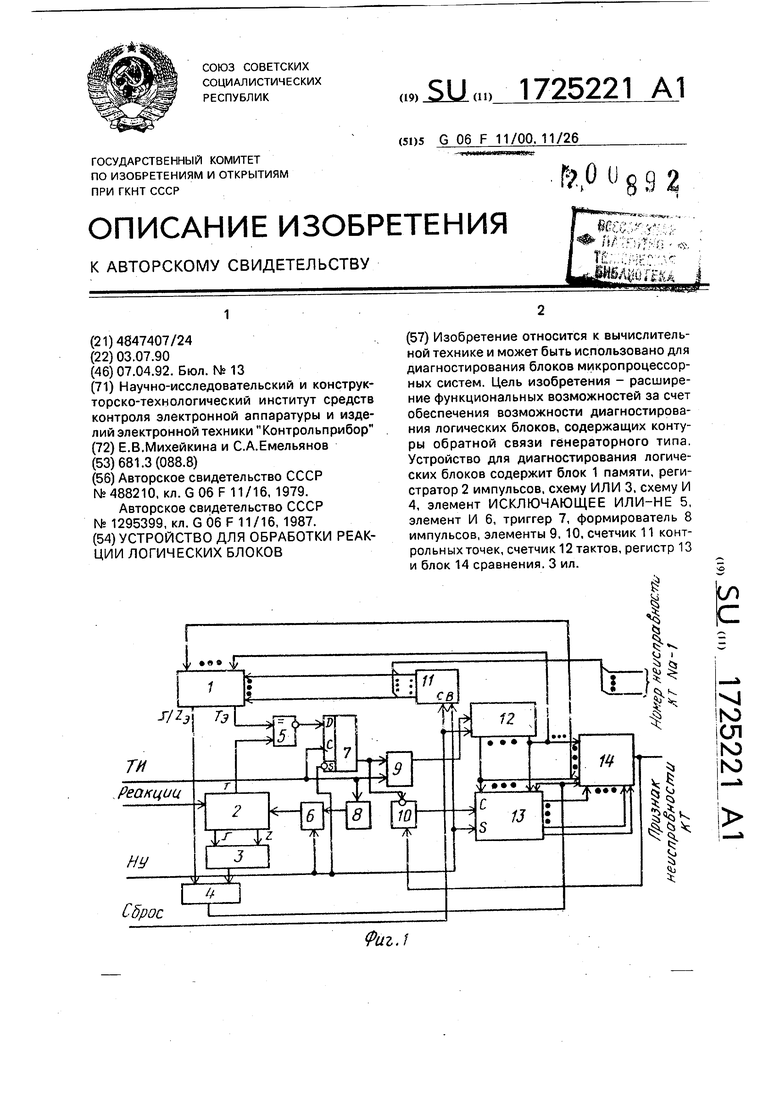

На фиг.1 представлена структурная схема устройства; на фиг.2 - пример реализации регистратора импульсов; на фиг.З - пример схемы с обратной связью генераторного типа и временная диаграмма прохождения сигналов в схеме.

Устройство для обработки реакции логических блоков содержит блок 1 памяти, регистратор 2 импульсов, элемент ИЛИ 3, элемент И 4, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 5, элемент И 6, триггер 7, формирователь 8 импульсов, элементы И 9, 10, счетчик 11 контрольных точек, счетчик 12 тактов, регистр 13, блок 14 сравнения.

Регистратор 2 импульсов, функциональная схема которого приведена на фиг.2, содержит элемент НЕ 15, триггеры 16, 17, резистор 18.

Пример схемы с обратной связью генераторного типа приведен на фиг.З. Она содержит триггер 19, элемент И 20, элемент И-НЕ21.

Устройство для обработки реакции логических блоков работает следующим образом.

Сигналом начальной установки (НУ) устанавливаются в нулевое состояние счетчик 11 контрольных точек и импульсов, в единичное - регистр 13 и триггер 7. Принцип работы устройства предполагает последовательный опрос состояний контрольных точек контролируемого блока, которыми являются входы или выходы элементов блока. На схеме контролируемого блока, изображенной на фиг.З, контрольными точками (КТ) определены точки - выходы элементов W, Wi, и входы элементов X, Y, Z, D-вход триггера, состояние которых опрашивается последовательно, начиная с выходного контакта схемы. Перед съемом реакции в очередной КТ подачей нулевого сигнала по входу сброса устройства оператор устанавливает в нулевое состояние счетчик 12 тактов и переключает счетчик 11 КТ по счетному входу. На триггерах счетчика 11 КТ фиксируется номер последней опрашиваемой КТ. Блок 1 памяти хранит массив эталонных реакций для каждой КТ. Выбор двухбитовой информации об эталонном состоянии КТ в такте (первый бит - эталонная

реакция в такте, второй бит - информация о наличии короткого импульса в такте) осуществляется для каждой КТ управляющими линиями со счетчика 11 КТ, для каждого

такта - адресными линиями, на которые сигналы приходят со счетчика 12 тактов.

Итак, в начальный момент времени, после вырабтки сигналов НУ и сброса в регистре 13 записано максимальное число

0 тактов-единицы по всем разрядам, счетчик 12 тактов сброшен и из блока 1 памяти выбрана эталонная информация для первой КТ в первом такте проверки. При поступлении тактовых импульсов (ТИ) на вход устройства

5 одновременно на регистратор 2 импульсов приходят реакции с КТ контролируемого блока. При этом синхронизацию выдачи ТИ и реакций осуществляет внешнее задающее устройство, которое обеспечивает времен0 ную диаграмму выдачи сигналов, изображенную на фиг.З, и в качестве которого может быть использована ЭВМ или генератор тестов. Регистратор 2 импульсов принимает реакцию в КТ и трансформирует ее на

5 три составляющие: собственно реакцию, т.е. ее логический уровень в такте, и наличие перепадов из нуля в единицу в КТ в такте поступает на элемент 5 сравнения - ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, на выходе которого

0 появляется уровень логической единицы в случае совпадения реакций, нуля - при несовпадении значений эталонной и снимаемой реакций в КТ, которое фиксируется на триггере 7. Число тактов подсчитывается

5 счетчиком 12 тактов через открытый элемент И 9.

В момент несовпадения снимаемой и эталонной реакций триггер 7 сбрасывается, фиксирует состояние счетчика 12 тактов и

0 разрешает прохождение через элемент И 10 сигнала признака сравнения с блока 14 сравнения на синхровход регистра 13. Так как число, записанное в регистр (единицы по всем разрядам), заведомо больше макси5 мальногочисла тактов, то блок 14 сравнения выдает единичный уровень результата сравнения, который свидетельствует о том, что. число, записанное в регистр 13, больше числа тактов, зафиксированного на выходах

0 счетчика 12 тактов. Перепад из нуля в единицу этого сигнала фиксирует информацию о такте несравнения в регистре 13. При этом в старшем разряде регистра 13 фиксируется значение номера подтакта несравнения в

5 случае, если в эталонной реакции в такте присутствует импульс. Этот сигнал формируется элементом И 4, элементом ИЛИ 3 и регистратором 2 импульсов.

Перед переходом к следующей КТ оператор устанавливает счетчик 12 тактов в исходное состояние и выбирает область памяти эталонных реакций для следующей КТ. В момент несовпадения сигналов в следующей точке запускается триггер 7, который фиксирует состояние счетчика 12 тактов и осуществляет опрос состояния блока 14 сравнения. Если число, хранящееся в регистре 13, больше числа, зафиксированного счетчиком 12 тактов, то это свидетельствует о том, что ошибка в исследуемой точке появилась раньше на определенное количество тактов, чем в предыдущей, и, таким образом, элементы проверяемой схемы между этими точками не являются источником неисправности. В этом случае блок 14 сравнения выдает сигнал высокого уровня, который разрешает запись содержимого счетчика 12 тактов в регистр 13. Если число, хранящееся на регистре 13, меньше числа, зафиксированного счетчиком 12 тактов, то это Свидетельствует о том, что неисправность в исследуемой КТ появилась позже, чем в предыдущей, и, таким образом, элементы проверяемой схемы между этими точками являются источником неисправности. В этом случае блок сравнения выдает сигнал нулевого уровня, а регистр 13 сохраняет свое состояние до исследования сигнала в следующей точке. Если в результате опроса и сигналов на всех входах подозреваемого элемента установлено, что ошибки на входах появляются позже, чем на выходе элемента, то элемент считается неисправным по выходу.

Возможна ситуация (фиг.З), когда такт несравнения на входе и выходе элемента одинаков. Тогда в результате сравнения участвует и номер подтакта несравнения, который формируется элементом И 4, элементом ИЛИ 3 и регистратором 2 импульсов.

Перед переходом к опросу состояния следующей КТ оператор выработкой сигнала Сброс сбрасывает счетчик 12 тактов и выбирает область памяти эталонных реакций для следующей УТ. Процедура определения минимального такта и подтакта несравнения повторяется. Так, для схемы, изображенной на фиг.З, при наличии неисправности типа Л/2 1 такт несравнения в точках Wi и АЛ/2 одинаков и равен трем, но подтакт несравнения разный: в точке Wi - 2,5, (так как сигнал Г равен 0, а сигнал Z. - 1), в точке W - 2,0 (оба сигнала Г и 1 равны 0). Номер подтакта при этом определяется значениями сигналов „Г и 1. Так как вначале опрашивается состояние точки Wi, затем Wa, то значения такта и подтакта несравнения в КТ Wi фиксируются в регистре 13, в КТ-на счетчике 12 тактов. Результат

сравнения выдается с выхода блока 14 сравнения в виде 1, что означает: число, хранящееся на счетчике 12 тактов, меньше или равно числу, зафиксированному на регистре

13. Единичный уровень выходного сигнала блока 14 сравнения фиксирует значение счетчика 12 тактов в регистре 13. Опрос входа элемента И 20 фиксирует на счетчике 12 тактов число, большее записанного в регистре 13. При этом нулевой уровень с выхода блока 14 сравнения является признаком присутствия неисправности в предыдущей КТ. Если из числа, которое фиксируется при этом на счетчике 11 КТ, вычесть единицу, то

можно получить номер КТ, на которой зафиксирована неисправность. Эти результаты могут быть обработаны на ЭВМ, либо выведены на индикацию.

Регистратор 2 импульсов работает следующим образом. Триггеры 16 и 17 сбрасываются по входу сброса в каждом такте проверки импульсом, получаемым формирователем 8 импульсов по положительному перепаду ТИ. Если реакция в такте не меняет своего значения, то оба выхода триггеров находятся в нулевом состоянии. В противном случае в зависимости от знака перепада (из 0 в 1 или наоборот) выдается единичный уровень сигнала с триггеров 16 или 17. Если

в такте появляется импульс, то выходы обоих триггеров будут находиться в единичном состоянии.

Формула изобретения

Устройство для обработки реакции логических блоков, содержащее блок памяти, регистр и блок сравнения, причем выходы регистра соединены с первой группой входов блока сравнения, отличающееся

тем, что, с целью расширения функциональных возможностей за счет обеспечения ди- агностирования логических блоков, содержащих контуры обратной связи генераторного типа, оно содержит регистратор

импульсов, счетчик контрольных точек, элемент ИЛИ, счетчик тактов, четыре элемента

И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, триггер, формирователь импульсов, причем адресные входы блока памяти соединены с

разрядными выходами счетчика тактов, син- хровход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом триггера и с инверсным входом второго элемента И, синхровход

триггера, а также второй вход первого элемента И и вход формирователя импульсов объединены и образуют тактовый вход устройства, выход поля эталонных реакций блока памяти соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, выход которого соединен с информационным входом триггера, инверсный вход установки которого соединен с входом начальной установки устройства, первым входом третьего элемента И, с входом сброса счетчика контрольных точек и установочным входом регистра, информационные входы которого, кроме старшего, а также вторая группа входов, кроме старшего, блока сравнения соединены с информационными .выходами счетчика тактов, вход сброса которого соединен с входом сброса устройства и с синх- ровходом счетчика контрольных точек, разрядные выходы которого соединены с управляющими входами блока памяти, а также являются выходными сигналами устройства, синхровход регистратора импуль сов соединен с информационным входом устройства, разрядные выходы регистрато0

5

0

ра импульсов соединены с входами элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом признака фиксации короткого импульса в такте эталонной реакции блока памяти, выход четвертого элемента И соединен со старшим информационным входом регистра и старшим разрядом второй группы входов блока сравнения, выход которого является выходным сигналом устройства и соединен с прямым входом второго элемента И, выход которого соединен с синхровходом регистра, выход формирователя импульсов соединен с вторым входом третьего элемента И, выход которого соединен с входом сброса регистратора импульсов, разрядный выход которого соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ.

Регистратор имлульсоб 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для поиска дефектов дискретных блоков | 1990 |

|

SU1714610A1 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Устройство для контроля монтажных соединений | 1988 |

|

SU1608696A1 |

| Устройство для контроля и диагностики цифровых блоков | 1976 |

|

SU605216A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

Изобретение относится к вычислительной технике и может быть использовано для диагностирования блоков микропроцессорных систем. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности диагностирования логических блоков, содержащих контуры обратной связи генераторного типа. Устройство для диагностирования логических блоков содержит блок 1 памяти, регистратор 2 импульсов, схему ИЛИ 3, схему И 4, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 5, элемент И 6, триггер 7, формирователь 8 импульсов, элементы 9, 10, счетчик 11 конт- рольныхточек, счетчик 12 тактов, регистр 13 и блок 14 сравнения. 3 ил.

L

Фиг. 2

J

fe,

Ф,

ut . 3

Ш -/ay

uec/v&t&Kijt

| Устройство для обнаружения ошибок | 1973 |

|

SU488210A1 |

| Авторское свидетельство СССР № 1295399, кл.С 06 F 11/16, 1987 | |||

Авторы

Даты

1992-04-07—Публикация

1990-07-03—Подача