Изобретение относится к вычислительной технике и может быть использовано для построения арифметических устройств.

Целью изобретения является повышение быстродействия и обеспечение тестопригодности.

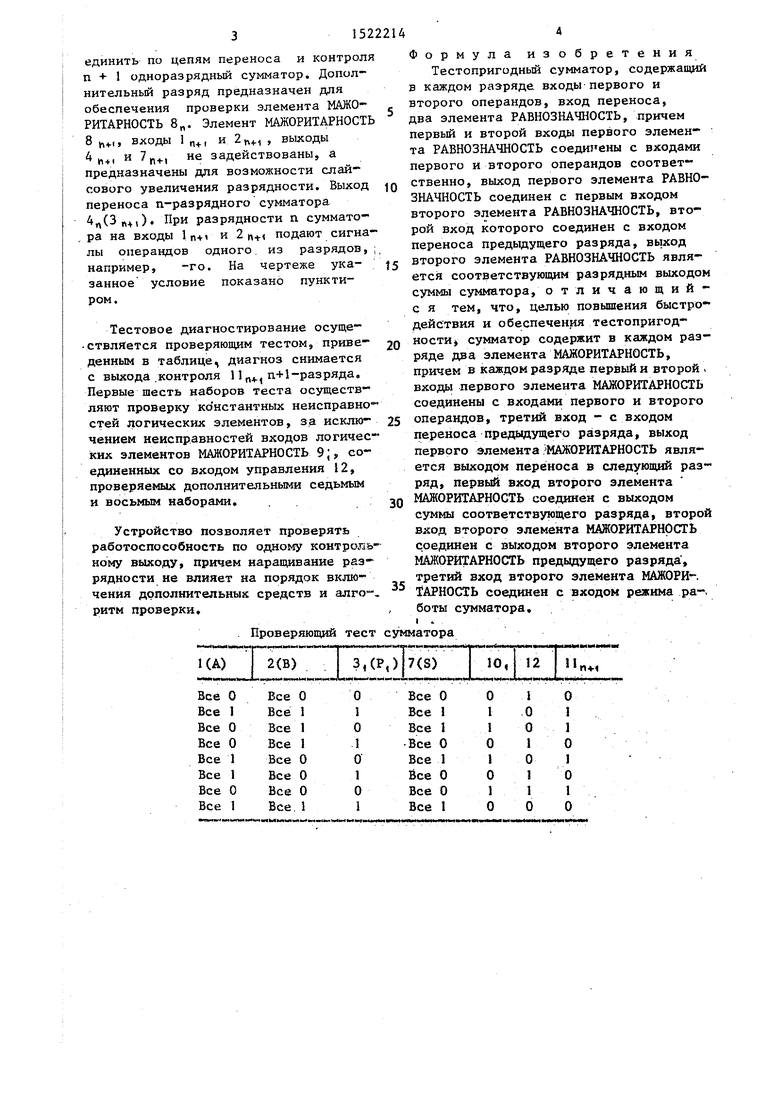

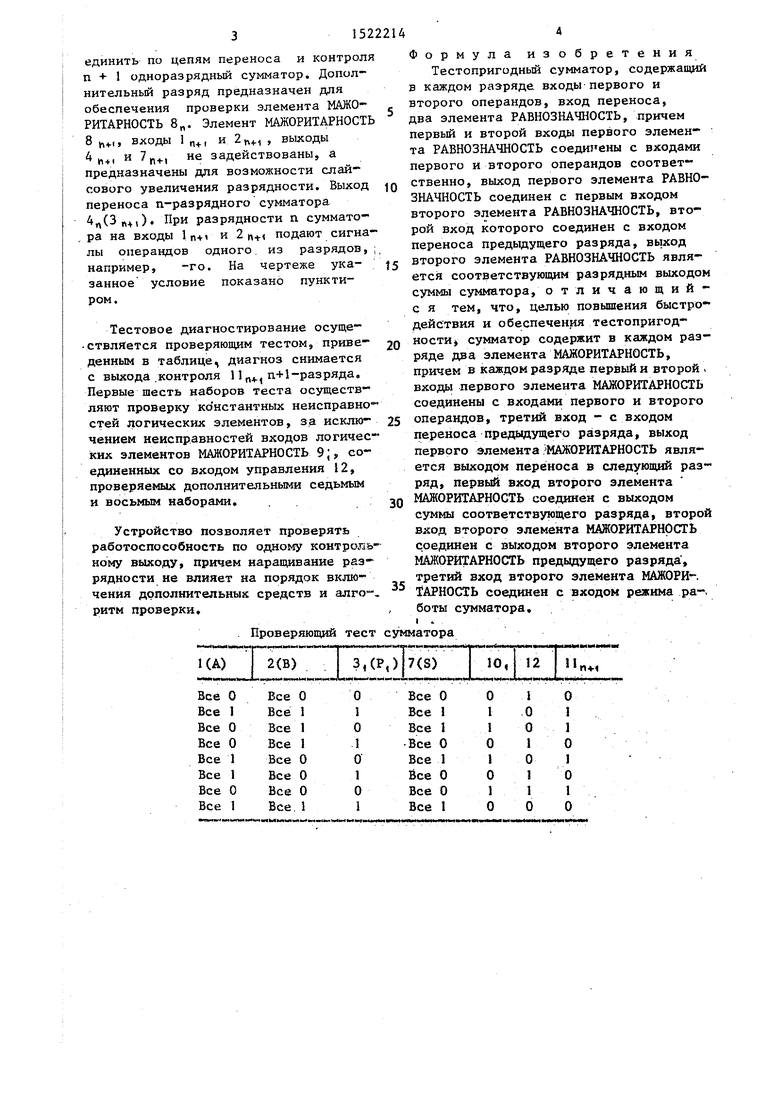

На чертеже представлена функциональная схема тестопригодного сумматора.

Сумматор содержит информационные входы операндов А, В - 1;, 2;, переноса Р, 3J, выход переноса в следующий разряд Р 4, элементы РАБ НОЗНАЧНОСТЬ 5;, 6;, выход суммы

S; - 7 i, элементы НАЖОРИТАРНОСТЬ 8;,9-, вход контроля 10j, выход контроля 11, вход управления 12.

Сумматор функционирует следующим образом.

При подаче на информационные входы операндов А, В и переноса Р каждый разряд выполняет функции

S; - А;®В;®Р;;

Р; A P;VA,-B..VBjP,-. ,

Для построения п-разрядного тесто- пригодного сумматора необходимо ND N9 Ю

единить по цепям переноса и контроля + 1 одноразрядный сумматор. Дополнительный разряд предназначен для обеспечения проверки элемента МАЖО- РИТАРНОСТЬ 8„, Элемент МАЖОРИТАРНОСТЬ 8 ,, входы 1 п, и 2. , выходы п+( и 7., не задействованы, а предназначены для возможности слай- сового увеличения разрядности. Выход переноса п-разрядного сумматора A,y(3n4i)« При разрядности п суммато- ра на входы In+t и 2 |,- подают сигналы операндов одного. из разрядов, ;, например, то. На чертеже указанное условие показано пунктиром.

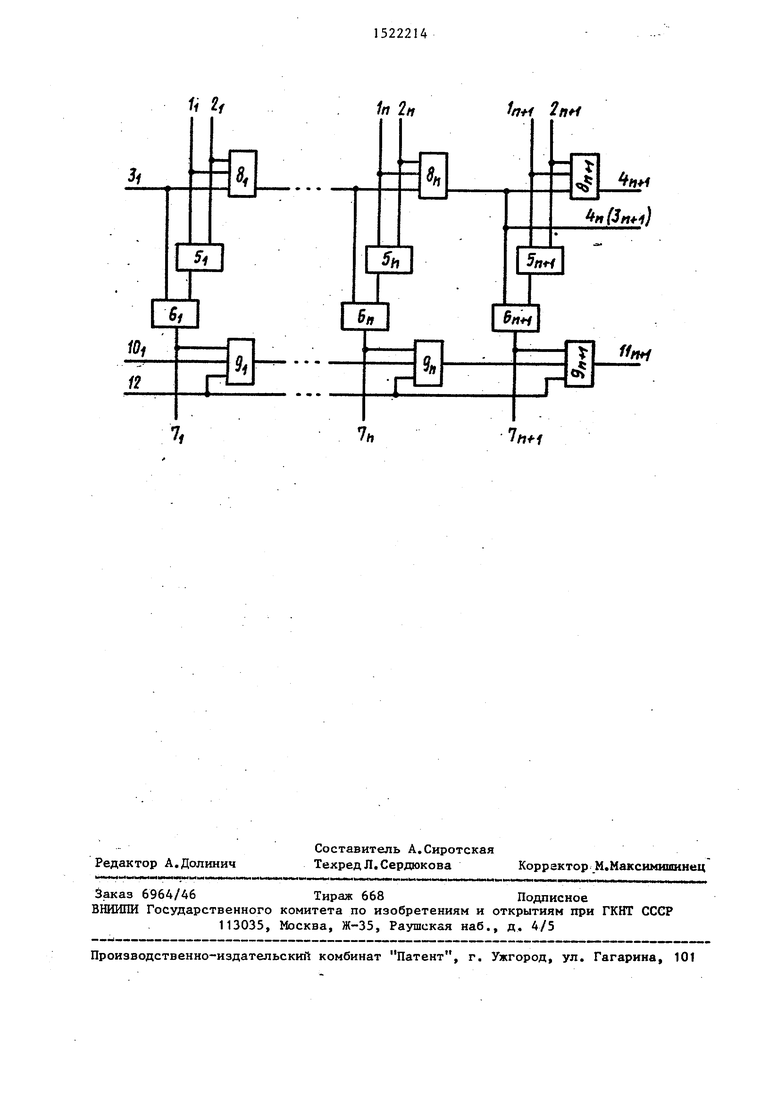

Тестовое диагностирование осуще- ствлЯется проверяющим тестом, приведенным в таблице, диагноз снимается с выхода .контроля 11 „. п+1-разряда. Первые шесть наборов теста осуществляют проверку ко нстантных неисправно стей логических элементов, за исключением неисправностей входов логических элементов МАЖОРИТАРНОСТЬ 9;, соединенных со входом управления 12, проверяемых дополнительными седьмым и восьмым наборами.

Устройство Позволяет проверять работоспособность по одному контрольному выходу, причем наращивание разрядности не влияет на порядок включения дополнительных средств и алго-. ритм проверки.

5

0

5

0

5

Формула изобретения

Тестопригодный сумматор, содержащий в каждом разряде входы первого и второго операндов, вход переноса, два элемента РАВНОЗНАЧНОСТЬ, причем первьш и второй входы первого элемента РАВНОЗНАЧНОСТЬ соединены с входами первого и второго операндов соответственно, выход первого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с входом переноса предьщущего разряда, выход второго элемента РАВНОЗНАЧНОСТЬ является соответствующим разрядным выходом суммы сумматора, отличающий- с я тем, что, целью повышения быстродействия и обе.спечения тестопригод- ностиу сумматор содержит в каждом разряде два элемента МАЖОРИТАРНОСТЬ, причем в каждом разряде первый и второй входы первого элемента МАЖОРИТАРНОСТЬ соединены с входами первого и второго операндов, третий вход - с входом переноса предыдущего разряда, выход первого элемента /МАЖОРИТАРНОСТЬ является выходом переноса в следующий разряд, первый вход второго элемента МАЖОРИТАРНОСТЬ соединен с выходом суммы соответствующего разряда, второй вход второго элемента МАЖОРИТАРНОСТЬ соединен с выходом второго элемента МАЖОРИТАРНОСТЬ предыдущего разряда, третий вход второго элемента МАЖОРИ-. ТАРНОСТЬ соединен с входом режима ра-. боты сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Тестопригодное логическое устройство | 1986 |

|

SU1451695A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Одноразрядный адаптируемый четверичный сумматор | 1981 |

|

SU1053102A1 |

| Диагностируемый регистр | 1986 |

|

SU1383443A1 |

| СПОСОБ ТЕСТОПРИГОДНОЙ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 2008 |

|

RU2413282C2 |

| Суммирующе-вычитающее устройство | 1986 |

|

SU1363192A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Сумматор | 1989 |

|

SU1735841A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение быстродействия, обеспечение тестопригодности. Цель достигается тем, что тестопригодный сумматор, содержащий в каждом разряде входы первого и второго операндов, вход переноса, два элемента РАВНОЗНАЧНОСТЬ, причем входы первого элемента соединены со входами первого и второго операндов, выход соединен с первым входом второго элемента РАЗНОЗНАЧНОСТЬ, второй вход которого соединен со входом переноса из предыдущего разряда, а выход является выходом суммы, сумматор в каждом разряде имеет первый и второй элементы МАЖОРИТАРНОСТЬ, причем первый и второй входы первого элемента соединены со входами первого и второго операндов, третий вход- со входом переноса из предыдущего разряда, а выход является выходом переноса в следующий разряд, первый вход второго элемента МАЖОРИТАРНОСТЬ соединен с выходом суммы, второй вход соединен с выходом второго элемента МАЖОРИТАРНОСТЬ предыдущего разряда, а третий вход соединен со входом управления устройства. 1 ил., 1 табл.

. Проверяющий тест сумматора

1i 2f

0Ш

10i

12

In 2ft

ffjH 2nH

Tl /m/

7h

| Саофалов К.Г | |||

| и др | |||

| Цифровые электронные вычислительные машины | |||

| К.: Вища школа, 1983, с.146 | |||

| Сумматор-вычитатель | 1985 |

|

SU1251070A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-15—Публикация

1987-11-17—Подача