Изобретение относится к вычисли- I тельной технике и может быть исполь- зовано при построении быстродействующих вычислительных систем, реализуе- мых в интегральном исполнении.

Цель изобретения - повышение быстродействия и уменьшение потребляемой мощности.

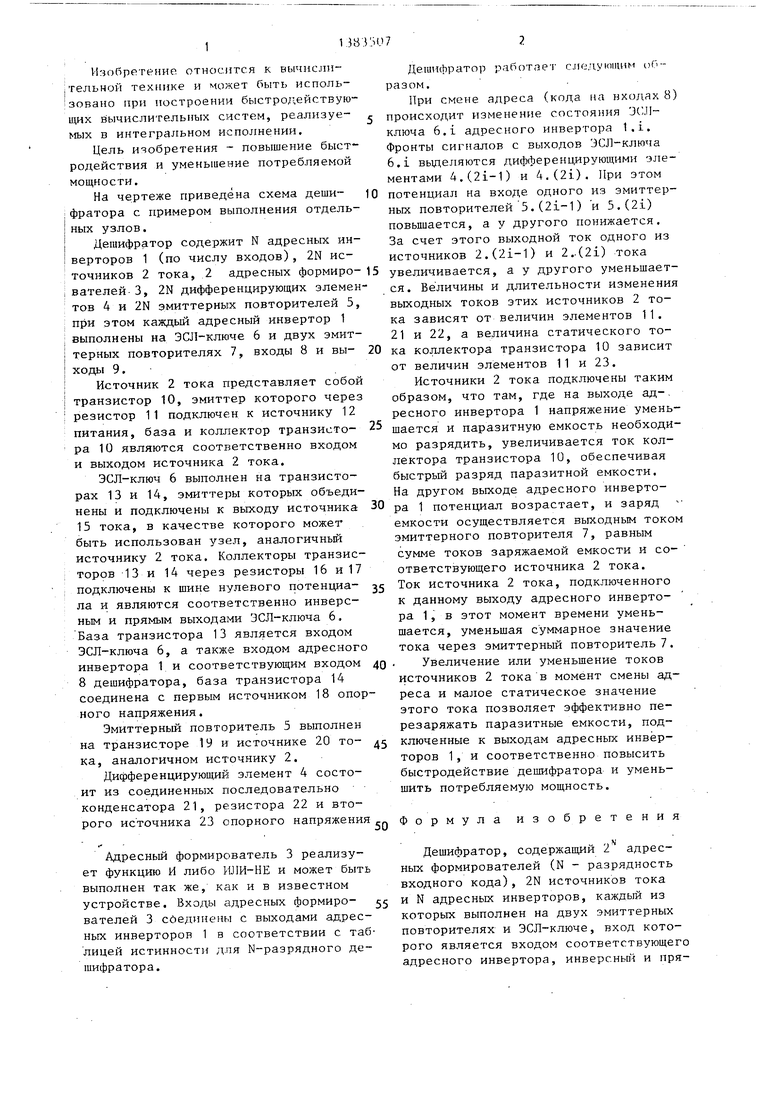

На чертеже приведена схема деши- фратора с примером выполнения отдельных узлов.

Дешифратор содержит N адресных инверторов 1 (по числу входов), 2N источников 2 тока, 2 адресных формиро- вателей-3, 2N дифференцирующих элементов 4 и 2N эмиттерных повторителей 5, при этом каждый адресный инвертор 1 выполнены на ЭСЛ-ключе 6 и двух эмиттерных повторителях 7, входы 8 и вы- ходы 9.

Источник 2 тока представляет собой транзистор 10, эмиттер которого через резистор 11 подключен к источнику 12 питания, база и коллектор транзисто- ра 10 являются соответственно входом и выходом источника 2 тока.

ЭСЛ-ключ 6 выполнен на транзисторах 13 и 14, эмиттеры которых объединены и подключены к выходу источника 15 тока, в качестве которого можег быть использован узел, аналогичный источнику 2 тока. Коллекторы транзисторов 13 и 14 через резисторы 16 и 17 подключены к шине нулевого потенциа- ла и являются соответственно инверсным и прямым выходами ЭСЛ-ключа 6. База транзистора 13 является входом ЭСЛ-ключа 6, а также входом адресного инвертора 1 и соответствующим входом 8 дешифратора, база транзистора 14 соединена с первым источником 18 опорного напряжения.

Эмиттерный повторитель 5 выполнен на транзисторе 19 и источнике 20 то- ка, аналогичном источнику 2,

Дифференцирующий элемент 4 состоит из соединенных последовательно конденсатора 21, резистора 22 и второго источника 23 опорного напряжения

I

Адресный формирователь 3 реализует функцию И либо Ш1И-НЕ и может быть выполнен так же, как и в известном устройстве. Входы адресных формиро- вателей 3 соединены с выходами адрес- ньк инверторов 1 в соответствии с таблицей истинности для N-разрядного дешифратора.

Дешифратор работает следующим оО-- разом.

При смене адреса (кода ка входах 8 происходит изменение состояния Jd.II- ключа 6.i адресного инвертора 1.1. Фронты сигналов с выходов ЭСЛ-ключа 6.1 вьщеляются дифференцирующими элементами 4. (21-1) и 4,(21). При этом потенциал на входе одного из эмиттерных повторителей 5.(21-1) и 5.(21) повышается, а у другого понижается. За счет этого выходной ток одного из источников 2.(21-1) и 2..(21) тока увеличивается, а у другого уменьшается. Величины и длительности изменени выходных токов этих источников 2 тока зависят от величин элементов 11. 21 и 22, а величина статического тока коллектора транзистора 10 зависит от величин элементов 11 и 23.

Источники 2 тока подключены таким образом, что там, где на выходе ад-, ресного инвертора 1 напряжение уменьшается и паразитную емкость необходимо разрядить, увеличивается ток коллектора транзистора 10, обеспечивая быстрьш разряд паразитной емкости. На другом выходе адресного инвертора 1 потенциал возрастает, и заряд емкости осуществляется выходным токо эмиттерного повторителя 7, равным сумме токов заряжаемой емкости и соответствующего источника 2 тока. Ток источника 2 тока, подключенного к данному выходу адресного инвертора 1, в этот момент времени уменьшается, уменьшая суммарное значение тока через эмиттерный повторитель 7.

Увеличение или уменьшение токов источников 2 тока в момент смены адреса и малое статическое значение этого тока позволяет эффективно перезаряжать паразитные емкости, подключенные к выходам адресных инверторов 1, и соответственно повысить быстродействие дешифратора и уменьшить потребляемую мощность.

Формула изобретения

JU

Дешифратор, содержащий 2 адресных формирователей (N - разрядность входного кода), 2N источников тока и N адресньк инверторов, каждый из которых выполнен на двух эмиттерных повторителях и ЭСЛ-ключе, вход которого является входом соответствующег адресного инвертора, инверсньп и прямой пыходы ЭСЛ-ключя соединены с рходами соответственно первого и второго эмиттерных повторителей, выходы первого и второго эмиттерных повторителей i-ro адресного инвертора объединены с выходами соответственно (2i)-ro и (2i-1)-ro источников тока и подключены к соответствующим входам соответствующих адресных формировате- лей, выходы которых являются одноименными выходами дешифратора, входы адресных инверторов являются одноименными входами дешифратора, о т

личающийсч тем, что, с целью повьпиения быстродействия и уменьшения потребляемой мощности, в дешифратор введены 2N дифференцирую- элементов и 2N эмиттерных повторителей, входы (21-1)-го и (21)-го дифференцирующих элементов подключены соответственно к инверсному и прямому выходам ЭСЛ-ключа i-ro адресного инвертора, выход каждого дифференцирующего элемента через одноименный эмиттерньм повторитель подключен к входу одноименного источника тока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор запоминаюшего устройства | 1979 |

|

SU871330A1 |

| Матричный коммутатор | 1984 |

|

SU1198541A1 |

| Многопортовое запоминающее устройство | 1990 |

|

SU1718270A1 |

| ЯЧЕЙКА БАЗОВОГО МАТРИЧНОГО КРИСТАЛЛА | 1992 |

|

RU2035088C1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1327293A1 |

| Импульсный модулятор | 1978 |

|

SU765998A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Транзисторный ключ | 1988 |

|

SU1573535A1 |

| Дешифратор | 1986 |

|

SU1336251A1 |

Изобретение относится к вычислительной технике. Его использование при построении быстродействующих вычислительных систем, реализуемых в виде интегральных схем, позволяет повысить быстродействие и уменьшить потребляемую мощность. Дешифратор содержит источники 2 тока, адресные формирователи 3 и адресные инверторы 1, выполненные на ЭСЛ-ключе 6 и эмиттерных повторителях 7. Введение дифференцируюпдах элементов 4 и эмиттерных повторителей 5 обеспечивает соответствующен изменение токов источников 2 тока в момент смены входного кода и малое статическое значение этих токов, благодаря чему производится эффективный перезаряд паразитных емкостей, подключенных к выходам адресных инверторов 1. 1 1Ш. i (Л со 00 00 сд

| Дешифратор | 1986 |

|

SU1336251A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Валиев К.А., Орликовский А.А | |||

| Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах | |||

| - М.: Советское радио, 1979, с | |||

| Камневыбирательная машина | 1921 |

|

SU222A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-14—Подача