4

to СП vj

ел

1А2

ная модель экспоненциального типа для оценки любых распределений. Работа устройства основывается на предварительной оценке параметров распределения, по которым определяются параметры модели. Устройство содержит блок 1 вычисления моментов, блок 2 вычисления натурального логарифма, блок 3 вычисления параметра аппроксимации контрэксцесса, блок 4 вычисления параметров распределения, делители 5,6,7, вычитатели 8,9, регистры 10,11, синхронизатор 12,

умножители 13,14, генератор 15 линейно изменяющегося напряжения, аналого-цифровой преобразователь 13,14, генератор 15 линейно изменяющегося напряжения, аналого-цифровой преобразователь 16, сумматоры 17,18, блоки 19,20 вычисления модуля, блоки 21,22 возведения в степень, элементы НЕ 23,24, блоки 25,26 вычисления экспоненты, множительно-делительный блок 27, элемент 28 сравнения, элемент 29 задержки, коммутирующий элемент 30, интегратор 31. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Устройство для определения закона распределения | 1986 |

|

SU1388900A1 |

| Устройство для определения закона распределения | 1987 |

|

SU1520545A1 |

| Статистический анализатор | 1989 |

|

SU1695328A1 |

| Коррелометр | 1987 |

|

SU1478225A1 |

| Генератор случайных чисел | 1990 |

|

SU1817093A1 |

| Статистический анализатор | 1986 |

|

SU1401482A1 |

| Статистический анализатор | 1987 |

|

SU1425716A1 |

| Статистический анализатор | 1989 |

|

SU1631557A1 |

| Статистический анализатор | 1986 |

|

SU1354211A1 |

Изобретение относится к вычислительной технике и может быть использовано при определении законов распределения случайньгх погрешностей приборов и измерений по ограниченной выборке. Целью изобретения является повышение точности определения закона. Для достижения цели в устройстве используется единая обобщен

1

Изобретение относится к вычислительной технике и может быть использовано при определении законов распределения случайных погрешностей приборов и измерений по ограниченной выборке.

Целью изобретения является повышение точности определения закона распределения при малом числе опытных .данных..

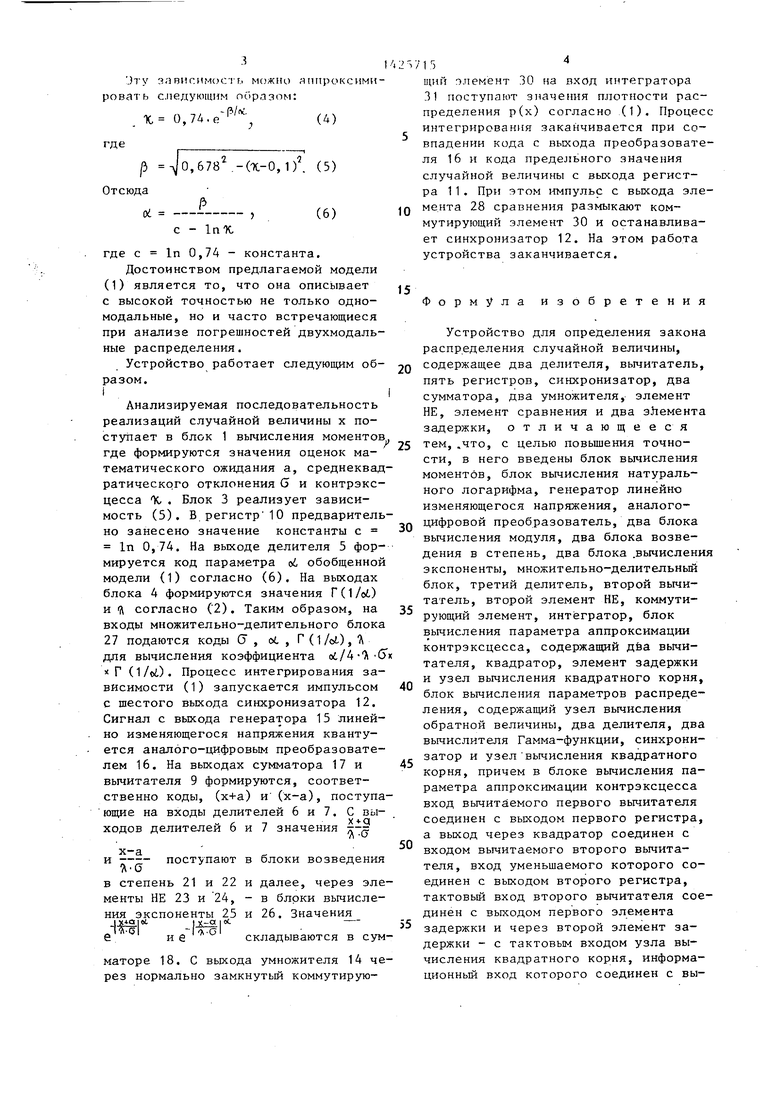

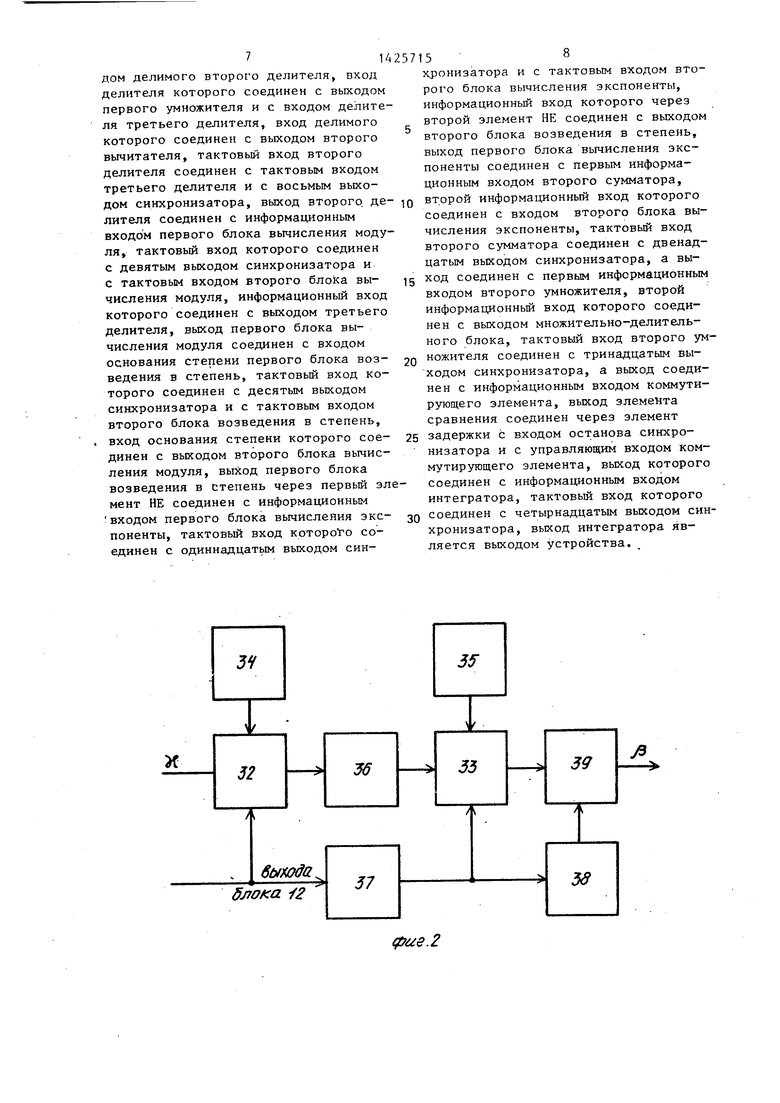

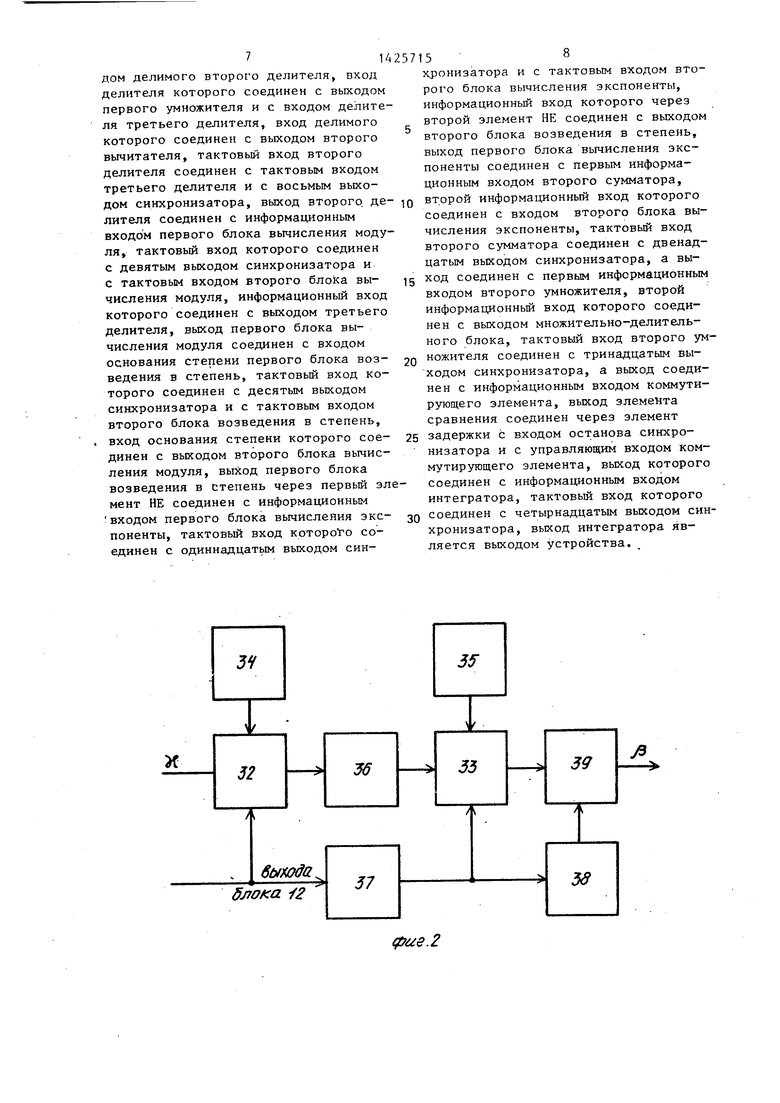

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока вычисления натурального логарифма; на фиг. 3 - функ- циональ.ная схема блока вьиисления параметров распределения.

Устройство содержит блок 1 вычисления моментов, блок 2 вычисления натурального логарифма, блок 3 вычисления параметра аппроксимации контрэкст цесса, блок 4 вычисления параметров распределения, делители 5-7, вычитатели 8 и 9, регистры 10 и 11, синхронизатор 12, умножители 13 и 14, генератор 15 линейно изменяющегося напряжения, аналого-цифровой преобразователь 16, сумматоры 17 и 18, блоки 19 и 20 вычисления модуля, блоки 21 и 22 возведения в степень, элементы НЕ 23 и 24, блоки 25 и 26 вычисления экспоненты, множительно-делительный блок 27,, элемент 28 сравнения элемент 29 задержки, коммутирующий элемент 30 и интегратор 31, блок 3 содержит вьиитатели 32 и 33, регистры 34 и 35, квадратор 36, элементы 37 и 38 задержки, узел 39 вычисле

5

0

5

0

ния квадратного корня, блок 4 содержит узел 40 вычисления обратной величины, делители 4.1 и 42, синхронизатор 43, вычислители 44 и 45 Гамма- функции, регистр 46 и узел 47 вычисления квадратного корня.

В основу работы устройства положены результаты исследований законов распределения погрешностей приборов и измерений по ограниченным данным наблюдений. Теоретическое и экспериментальное исследование позволяет разработать единую двухпараметричес- кую модель для описания любых симметричных (что характерно для погрешностей) законов распределения:

( -

r-x-cf-TcT/ Tl

х-а

ef.1

;

(1)

где р(х) а, (j

Г(у) oi

плотность вероятности распределения,- оценки среднего и средче- квадратического отклонений;

Гамма-функция; параметр, определяющий форму закона распределения , функция от oi вида

-Л |r(1/oi,)/r(3/o6). . (2) Доказано, что параметр «i связан с величиной Кх контрэксцесса распределения следующим образом:

Г (3/06) % -,. (3)

r().r(5/ot)

3

.Зту запяг.имостр.. можно аровать следующим образом: ,

. г 0,74.е - , где

Р Отсюда

oi -..

с - 1пХ

J

678V-()t-0,1).

где с In 0,74 - константа.

Достоинством предлагаемой модели (1) является то, что она описывает с высокой точностью не только одно- модальные, но и часто встречающиеся при анализе погрешностей двухмодаль- ные распределения.

Устройство работает следующим образом.

Анализируемая последовательность реализаций случайной величины х поступает в блок 1 вычисления моментов

где формируются значения оценок математического ожидания а, среднеквад- ратического отклонения G и контрэксцесса % . Блок 3 реализует зависимость (5). В регистр 10 предварительно занесено значение константы с In 0,74. На выходе делителя 5 формируется код параметра об обобщенной модели (1) согласно (6). На выходах блока 4 формируются значения Г(1/о{,) и Д согласно ( 2). Таким образом, на входы множительно-делительного блока 27 подаются коды G , оС , Г (1 /ot), для вычисления коэффициента Г (1/«i). Процесс интегрирования зависимости (1) запускается импульсом с шестого выхода синхронизатора 12. Сигнал с выхода генератора 15 линейно изменяющегося напряжения квантуется аналого-цифровым преобразователем 16. На выходах сумматора 17 и вычитателя 9 формируются, соответственно коды, (х+а) и (х-а), поступа- ющие на входы делителей 6 и 7. С выходов делителей 6 и 7 значения -

У

поступают в блоки возведения

х-а

« v5в степень 21 и 22 и далее, через элементы НЕ 23 и 24, - в блоки вычисления экспоненты 25 и 26. Значения I ы. I х-а I °t-

е не складываются в сумматоре 18. С выхода умножителя 14 через нормально замкнутый коммутирую1 - 4 2 S 7 1 5

щий элемент 30 на вход интегратора 31 поступают значения плотности распределения р(х) согласно (1). Процесс интегрирования заканчивается при совпадении кода с выхода преобразователя 16 и кода предельного значения случайной величины с выхода регистра 11. При этом импульс с выхода элемента 28 сравнения размыкают коммутирующий элемент 30 и останавливает синхронизатор 12. На этом работа устройства заканчивается.

15

20

I

30

-25

35

40

45

50

55

Формула изобретения

Устройство для определения закона распределения случайной величины, содержащее два делителя, вычитатель, пять регистров, синхронизатор, два сумматора, два умножителя, элемент НЕ, элемент сравнения и два элемента задержки, отличающееся тем,.что, с целью повышения точности, в него введены блок вычисления моментов, блок вычисления натурального логарифма, генератор линейно изменяющегося напряжения, аналого- цифровой преобразователь, два блока вычисления модуля, два блока возведения в степень, два блока .вычисления экспоненты, множительно-делительный блок, третий делитель, второй вычитатель, второй элемент НЕ, коммутирующий элемент, интегратор, блок вычисления параметра аппроксимации контрэксцесса, содержащий два вычитателя, квадратор, элемент задержки и узел вычисления квадратного корня, блок вычисления параметров распределения, содержащий узел вычисления обратной величины, два делителя, два вычислителя Гамма-функции, синхронизатор и узел вычисления квадратного корня, причем в блоке вычисления параметра аппроксимации контрэксцесса вход вычитаемого первого вычитателя соединен с выходом первого регистра, а выход через квадратор соединен с входом вычитаемого второго вычитателя, вход уменьшаемого которого соединен с выходом второго регистра, тактовый вход второго вычитателя соединен с выходом первого элемента задержки и через второй элемент задержки - с тактовым входом узла вычисления квадратного корня, информационный вход которого соединен с вы5I/,

ходом второго вьпштателя, н блоке вычисления параметров рлспределения первьш выход синхронизатора соединен с тактовым входом первого делителя и с тактовым входом узла вычисления обратной величины, выход которого соединен с информационным входом первого вьмислителя Гамма-функции, тактовый вход которого соединен с вторым выходом синхронизатора и с тактовым входом второго вычислителя Гамма-функции, информационный вход которого соединен с выходом первого делителя, вход делимого которого соединен с выходом регистра, выход - второго вычислителя Гамма-функции соединен с входом делителя второго делителя, тактовый вход которого соединен с третьим выходом синхронизатора, а выход соединен с информационным входом узла вычисления квадратного корня, тактовый вход которого соединен с четвертым выходом синхронизатора, информационный вход блока вычисления моментов является информационным входом устройства, вход задания числа реализаций блока вычисления моментов является входом задания числа реализаций устройства, тактовый вход блока вычисления моментов соединен с первым выходом синхронизатора, вход запуска которого соединен с выходом окончания вычислений блока вычисления моментов, выход контрэксцесса блока вычисления моментов соединен с информационным входом блока вычисления натурального логарифма и с входом уменьшаемого первого вычИтателя блока вычисления пар аметра аппроксимации контрэксцесса, тактовый вход блока вычисления натурального логарифма соединен с вторым выходом синхронизатора, с тактовым входом первого вьгчитателя блока, вычисления параметра аппроксимации контрэксцесса и с входом первого элемента задержки блока вычисления параметра аппроксимации контрэксцесса, выход блока вычисления натурального логарифма соединен с входом вычитаемого первого вычитателя, вход уменьшаемого которого соединен с выходом первого регистра, тактовый вход первого вычитателя соединен с третьим выходом синхронизатора, а выход соединен с входом делителя первого делителя, вход делимого которого соединен с выходом узла вычисления

25715

5

0

5

0

5

0

5

0

5

квадратного корня блока В1 гчислення параметра аппроксимации коятрзкс- цесса, -тактовый вход первого делителя соединен с четвертью выходом синхронизатора, а выход соединен с входом делимого множительно-делительного блока, с входами показателя степени первого и второго блоков возведения в степень, с информационным входом узла вычисления обратной величины блока вычисления параметров распределения и с входом делителя первого делителя блока вычисления параметров распределения, пятый выход синхронизатора соединен с входом запуска синхронизатора блока вычисления параметров распределения, вход первого делителя множительно-делительного блока соединен с вькодом первого вычислителя Гамма-функции блока вычисления параметров распределения и с входом делимого второго делителя блока вычисления параметров распределения, вход второго делителя множительно- делительного блока соединен с выходом узла вычисления квадратного корня блока вычисления параметров распределения и с первым информационным входом первого умножителя, второй информационный вход которого соединен с выходом среднеквадратического отклонения блока вычисления моментов и с входом третьего делителя множительно-делительного блока, тактовый вход которого соединен с тактовым входом первого умножителя, с шестым выходом синхронизатора, с входом запуска аналого-цифрового преобразователя и с входом запуска генератора линейно изменяющегося напряжения, вход задания наклона которого соединен с первым входом элемента сравнения и с выходом второго регистра, выход генератора линейно изменяющегося напряжения соединен с информационным, входом аналого-цифрового преобразователя, выход которого соединен с вто- рьм входом элемента сравнения, с входом уменьшаемого второго вычитателя и с первым информационным входом первого сумматора, второй информационный вход которого соединен с выходом блока вычисления моментов и с входом вычитаемого второго вычитателя, так- товьш вход которого соединен с тактовым входом первого сумматора и с седьмым выходом синхронизатора, выход первого сумматора .соединен с вхо71

дом делимого второго делителя, вход делителя которого соединен с выходом первого умножителя и с входом делителя третьего делителя, вход делимого которого соединен с выходом второго вычитателя, тактовый вход второго делителя соединен с тактовым входом третьего делителя и с восьмым выходом синхронизатора, выход второго, да лителя соединен с информационным входом первого блока вычисления модуля, тактовый вход которого соединен с девятым выходом синхронизатора и с тактовым входом второго блока вы- числения модуля, информационный вход которого соединен с выходом третьего делителя, выход первого блока вычисления модуля соединен с входом основания степени первого блока воз- ведения в степень, тактовый вход которого соединен с десятым выходом синхронизатора и с тактовым входом второго блока возведения в степень, вход основания степени которого сое- динен с выходом второго блока вычисления модуля, выход первого блока возведения в степень через первый элмент НЕ соединен с информационным входом первого блока вычисления экс- поненты, тактовый вход которого соединен с одиннадцатью выходом син15«

хронизатора и с тактовым входом второго блока вычисления экспоненты, информационный вход которого через второй элемент НЕ соединен с выходом второго блока возведения в степень, выход первого блока вычисления экспоненты соединен с первым информационным входом второго сумматора, второй информационный вход которого соединен с входом второго блока вычисления экспоненты, тактовый вход второго сумматора соединен с двенадцатым выходом синхронизатора, а выход соединен с первым информационным входом второго умножителя, второй информационньш вход которого соединен с выходом множительно-делитель- ного блока, тактовый вход второго умножителя соединен с тринадцатьм выходом синхронизатора, а выход соединен с информационным входом коммутирующего элемента, выход элемента сравнения соединен через элемент задержки с входом останова синхронизатора и с управляющим входом коммутирующего элемента, выход которого соединен с информационным входом интегратора, тактовый вход которого соединен с четырнадцатым выходом синхронизатора, выход интегратора является выходом устройства.

Фб1е.2

фие.З

| Статистический анализатор | 1980 |

|

SU964653A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Статистический анализатор | 1986 |

|

SU1352518A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-01-14—Подача