/5

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадрата и квадратного корня | 1987 |

|

SU1550512A1 |

| Устройство для вычисления квадрата и квадратного корня | 1983 |

|

SU1120320A1 |

| Устройство для возведения в квадрат | 1985 |

|

SU1280616A1 |

| Модуляционный радиометр | 1984 |

|

SU1409953A1 |

| Устройство для возведения в квадрат М-разрядных двоичных чисел | 1986 |

|

SU1399733A1 |

| Устройство для возведения в квадрат | 1984 |

|

SU1239713A1 |

| Число-импульсное множительное устройство | 1986 |

|

SU1424014A1 |

| Устройство для определения спектральных коэффициентов разложения случайного процесса по функциям Хаара | 1980 |

|

SU935814A1 |

| Устройство для вычисления разности квадратов двух чисел | 1987 |

|

SU1471189A2 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1399731A1 |

со

00 О5

;о со

ГЧ)

ф1/г.

Изобретение относится к вычислитель- ной технике, может быть использовано в цифровых вычислительных и функциональных устройствах, цифровых измерительных приборах для обработки информации, представленной число-импульсным кодом, и является усовершенствованием устройства для вычисления квадрата и квадратного корня по авт. св. № 1120320.

Цель изобретения - повышение точности вычисления квадратного корня.

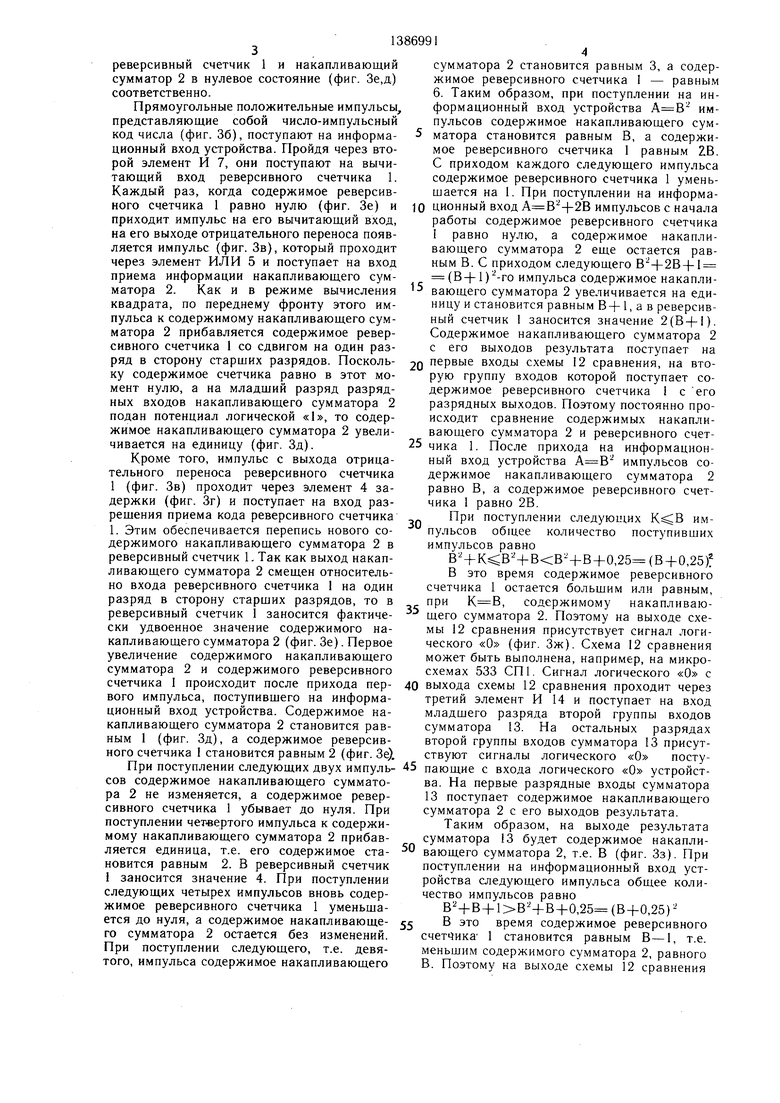

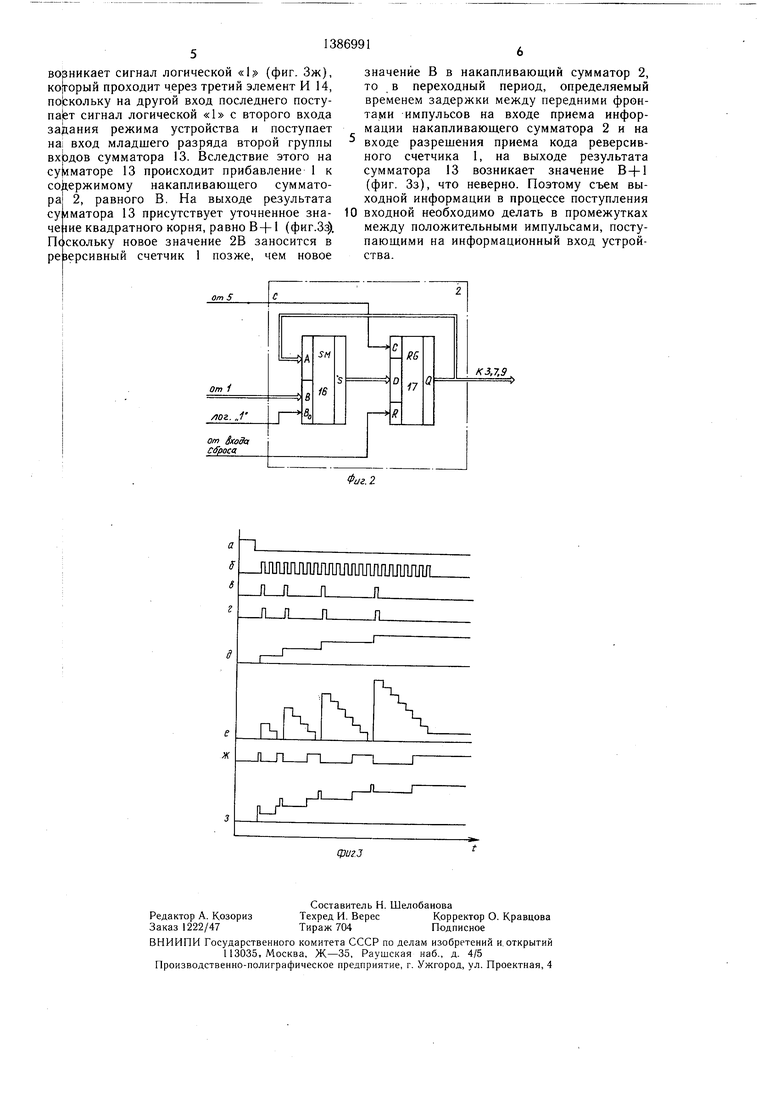

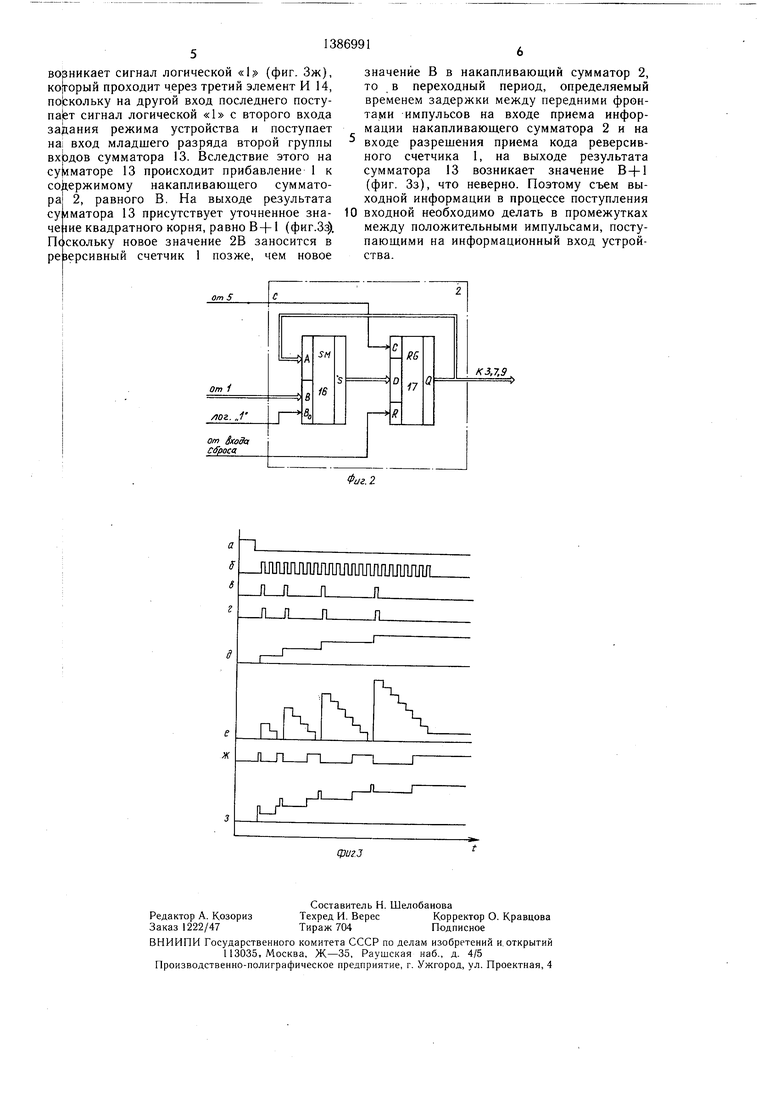

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - схема накапливающего сумматора; на фиг. 3 - временные диаграммы работы устройства.

Устройство содержит реверсивный счетчик 1, накапливающий сумматор 2, выход 3 (результата накапливающего сумматора), элемент 4 задержки, элемент ИЛИ 5, первый 6 и второй 7 элементы И, первый 8 и второй 9 управляюшие входы, информационный вход 10, вход 11 сброса устройства, схема 12 сравнения, сумматор 13, третий элемент И 14, выход 15 устройства. Накапливающий сумматор 2 (фиг. 2) содержит сумматор 16 и регистр 17.

На фиг. 3 обозначено: а - эпюра сигнала, поступающего на вход сброса уст- ройства; б - эпюра сигнала, поступаю- щего на информационный вход устройства; б - эпюра сигнала на выходе отрицательного переноса реверсивного счетчика 1; г - эпюра сигнала на выходе элемента 4 задержки, д - диаграмма состояния накапли- вающего сумматора 2; е - диаграмма состояния реверсивного счетчика 1; ж - эпюра сигнала на выходе схемы 12 сравнения, 3 - диаграмма кода на выходе результа- та сумматора 13.

Устройство для вычисления квадрата и квадратного корня работает следующим образом.

Перед началом работы реверсивный счетчик 1 и накапливающий сумматор 2 (фиг. 1) устанавливаются в нулевое состояние сигналом, поступающим на вход сброса устройства. Реверсивный счетчик 1 может быть выполнен, например, на микросхемах типа 133ИЕ7. Устанавливается режим работы устройства. В режиме вычисления квадрата на первый вход задания режима устройства подается потенциал логической «1, а на второй вход - потенциал логического «О. Входные положительные импульсы, представляющие число-импульсный код входного числа и поступающие на информационный вход устройства, проходят через открытый первый элемент И 6, поступают на суммирующий вход реверсивного счетчика 1 и через элемент ИЛИ 5 на вход приема информации накапливающего сумматора 2. В накапливающем сумматоре 2 (фиг. 2) эти импульсы поступают на вход записи регистра 17, информационные входы

которого соединены с выходами сумматора 16. Первые входы сумматора 16 соединены с выходами регистра 17. Вторые входы являются разрядными входами накапливаю- 5 щего сумматора 2. По переднему фронту импульса, поступающего на вход записи регистра 17, в него записывается сумма кода, находящегося в регистре 17 до поступления импульса, и кода, находящегося на

Q разрядных входах накапливающего сумматора 2, т.е. на вторых входах сумматора 16. Поскольку запись в регистр 17 происходит по фронту импульса, новая сумма, формирующаяся на выходах сумматора 16, не успевает поступить на информацион5 ные входы регистра 17.

Таким образом, по переднему фронту прямоугольных импульсов к содержимому накапливающего сумматора 2 прибавляется содержимое реверсивного счетчика 1. По заднему фронту этих импульсов содержимое

реверсивного счетчика 1 увеличивается на единицу. Поскольку содержимое реверсивного счетчика 1 поступает на разрядные входы накапливающего сумматора 2 смещенным на один разряд в сторону старших раз5 рядов, т.е. умноженным на два, а на вход младшего разряда разрядных входов накапливающего сумматора 2 подается потенциал логической «1 (фиг. 1), и кроме того, содержимое реверсивного счетчика 1 прибавляется к содержимому накапливающего сум0 матора 2 раньше, чем происходит увеличение содержимого реверсивного счетчика 1 на единицу, то в накапливающем сумматоре 2 формируется сумма нечетных чисел О, 1,3, 5,...(2п-1),...,т.е. после поступления на информационный вход устройства п

5 импульсов в накапливающем сумматоре 2

-м

находится сумма Е (2п-1), равная квадрату числа п. Код квадрата числа п с выхода результата накапливающего сумматора 2 поступает на первые разрядные входы сум матора 13. На первый разряд вторых разрядных входов сумматора 13 поступает потенциал логического «О с выхода третьего элемента И 14, поскольку на другой вход последнего поступает потенциал логического

5 «О с второго входа задания режима устройства. На остальные разряды вторых разрядных входов сумматора 13 поступают потенциалы логического «О с входа логического «О устройства. Вследствие этого код квадрата числа п присутствует на выходе

0 результата сумматора 13.

В режиме вычисления квадратного корня сигнал логической «1 подается на второй вход задания режима устройства, а сигнал логического «О - на первый вход задания режима устройства. Перед началом работы в режиме вь1числения квадратного корня на вход сброса устройства поступает сигнал (фиг. За), устанавливающий

реверсивный счетчик 1 и накапливающий сумматор 2 в нулевое состояние (фиг. Зе,д) соответственно.

Прямоугольные положительные импульсы, представляющие собой число-импульсный код числа (фиг. 36), поступают на информационный вход устройства. Пройдя через второй элемент И 7, они поступают на вычитающий вход реверсивного счетчика 1. Каждый раз, когда содержимое реверсивсумматора 2 становится равным 3, а содержимое реверсивного счетчика 1 - равным 6. Таким образом, при поступлении на информационный вход устройства импульсов содержимое накапливающего сум- 5 матора становится равным В, а содержимое реверсивного счетчика 1 равным 2В. С приходом каждого следующего импульса содержимое реверсивного счетчика 1 уменьшается на 1. При поступлении на информаного счетчика 1 равно нулю (фиг. Зе) и ю ционный вход импульсов с начала приходит импульс на его вычитающий вход,работы содержимое реверсивного счетчика

на его выходе отрицательного переноса появ- I равно нулю, а содержимое накапли- ляется импульс (фиг. Зв), который проходитвающего сумматора 2 еще остается равчерез элемент ИЛИ 5 и поступает на входным В. С приходом следующего В +2В-|-1

приема информации накапливающего сум- (В+1)-го импульса содержимое накаплиматора 2. Как и в режиме вычисления вающего сумматора 2 увеличивается на еди- квадрата, по переднему фронту этого им-ницу и становится равным В+1, а в реверсивный счетчик 1 заносится значение 2(В + 1)- Содержимое накапливающего сумматора 2 с его выходов результата поступает на

пульса к содержимому накапливающего сумматора 2 прибавляется содержимое реверсивного счетчика 1 со сдвигом на один разряд в сторону старщих разрядов. Посколь- 20 первые входы схемы 12 сравнения, на втоку содержимое счетчика равно в этот момент нулю, а на младший разряд разрядных входов накапливающего сумматора 2 подан потенциал логической «1, то содержимое накапливающего сумматора 2 увеличивается на единицу (фиг. Зд).

Кроме того, импульс с выхода отрицательного переноса реверсивного счетчика 1 (фиг. Зв) проходит через элемент 4 задержки (фиг. Зг) и поступает на вход раз- рещения приема кода реверсивного счетчика 1. Этим обеспечивается перепись нового содержимого накапливающего сумматора 2 в реверсивный счетчик 1. Так как выход накапливающего сумматора 2 смещен относительно входа реверсивного счетчика I на один разряд в сторону старщих разрядов, то в реверсивный счетчик 1 заносится фактически удвоенное значение содержимого накапливающего сумматора 2 (фиг. Зе). Первое увеличение содержимого накапливающего сумматора 2 и содержимого реверсивного

рую группу входов которой поступает содержимое реверсивного счетчика 1 с его разрядных выходов. Поэтому постоянно происходит сравнение содержимых накапливающего сум.матора 2 и реверсивного счет- 25 чика 1. После прихода на информационный вход устройства импульсов содержимое накапливающего сумматора 2 равно В, а содержимое реверсивного счетчика 1 равно 2В.

При поступлении следующих импульсов общее количество поступивших импульсов равно

В +К В +В В +В+0,25 (B+0,25)f В это время содержимое реверсивного счетчика 1 остается большим или равным, при , содержимому накапливающего сумматора 2. Поэтому на выходе схемы 12 сравнения присутствует сигнал логического «О (фиг. Зж). Схема 12 сравнения может быть выполнена, например, на микросхемах 533 СП1. Сигнал логического «О с

30

35

счетчика 1 происходит после прихода пер- 40 выхода схемы 12 сравнения проходит через

вого импульса, поступивщего на информационный вход устройства. Содержимое накапливающего сумматора 2 становится равным 1 (фиг. Зд), а содержимое реверсивного счетчика 1 становится равным 2 (фиг. Зе).

третий элемент И 14 и поступает на вход младшего разряда второй группы входов сумматора 13. На остальных разрядах второй группы входов сумматора 13 присутствуют сигналы логического «О постуПри поступлении следующих двух импуль- 45 пающие с входа логического «О устройст- сов содержимое накапливающего суммато- ва. На первые разрядные входы сумматора ра 2 не изменяется, а содержимое ревер-13 поступает содержимое накапливающего

сивного счетчика 1 убывает до нуля. При сумматора 2 с его выходов результата, поступлении четвертого импульса к содержи-Таким образом, на выходе результата

мому накапливающего сумматора 2 прибав- сумматора 13 будет содержимое накапли- ляется единица, т.е. его содержимое ста- вающего сумматора 2, т.е. В (фиг. Зз). При новится равным 2. В реверсивный счетчик 1 заносится значение 4. При поступлении следующих четырех импульсов вновь содержимое реверсивного счетчика 1 уменьща- ется до нуля, а содержимое накапливающе- 55

го сумматора 2 остается без изменений. При поступлении следующего, т.е. девятого, импульса содержимое накапливающего

поступлении на информационный вход устройства следующего импульса общее количество импульсов равно

B -fB+l B +B+0,25(B-fO,25)- В это время содержимое реверсивного счетчика 1 становится равным В-1, т.е. меньшим содержимого сумматора 2, равного В. Поэтому на выходе схемы 12 сравнения

сумматора 2 становится равным 3, а содержимое реверсивного счетчика 1 - равным 6. Таким образом, при поступлении на информационный вход устройства импульсов содержимое накапливающего сум- матора становится равным В, а содержимое реверсивного счетчика 1 равным 2В. С приходом каждого следующего импульса содержимое реверсивного счетчика 1 уменьшается на 1. При поступлении на информационный вход импульсов с начала работы содержимое реверсивного счетчика

рую группу входов которой поступает содержимое реверсивного счетчика 1 с его разрядных выходов. Поэтому постоянно происходит сравнение содержимых накапливающего сум.матора 2 и реверсивного счет- чика 1. После прихода на информационный вход устройства импульсов содержимое накапливающего сумматора 2 равно В, а содержимое реверсивного счетчика 1 равно 2В.

При поступлении следующих импульсов общее количество поступивших импульсов равно

В +К В +В В +В+0,25 (B+0,25)f В это время содержимое реверсивного счетчика 1 остается большим или равным, при , содержимому накапливающего сумматора 2. Поэтому на выходе схемы 12 сравнения присутствует сигнал логического «О (фиг. Зж). Схема 12 сравнения может быть выполнена, например, на микросхемах 533 СП1. Сигнал логического «О с

выхода схемы 12 сравнения проходит через

третий элемент И 14 и поступает на вход младшего разряда второй группы входов сумматора 13. На остальных разрядах второй группы входов сумматора 13 присутствуют сигналы логического «О поступающие с входа логического «О устройст- ва. На первые разрядные входы сумматора 13 поступает содержимое накапливающего

сумматора 13 будет содержимое накапли- вающего сумматора 2, т.е. В (фиг. Зз). При

поступлении на информационный вход устройства следующего импульса общее количество импульсов равно

B -fB+l B +B+0,25(B-fO,25)- В это время содержимое реверсивного счетчика 1 становится равным В-1, т.е. меньшим содержимого сумматора 2, равного В. Поэтому на выходе схемы 12 сравнения

возникает сигнал логической «1 (фиг. Зж), ко}горый проходит через третий элемент И 14, поскольку иа другой вход последнего посту- па|ет сигнал логической «1 с второго входа задания режима устройства и поступает на| вход младшего разряда второй группы вх|эдов сумматора 13. Вследствие этого на сумматоре 13 происходит прибавление 1 к содержимому накапливающего сумматора 2, равного В. На выходе результата суйматора 13 присутствует уточненное зна- че 1ие квадратного корня, равно В +1 (фиг.Зз). Поскольку новое значение 2В заносится в резерсивный счетчик 1 позже, чем новое

значение В в накапливающий сумматор 2, то в переходный период, определяемый временем задержки между передними фронтами импульсов на входе приема информации накапливающего сумматора 2 и на

входе разрешения приема кода реверсивного счетчика I, на выходе результата сумматора 13 возникает значение В+1 (фиг. Зз), что неверно. Поэтому съем выходной информации в процессе поступления

10 входной необходимо делать в промежутках между положительными импульсами, поступающими на информационный вход устройства.

Ж

| Устройство для вычисления квадрата и квадратного корня | 1983 |

|

SU1120320A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-07—Публикация

1986-10-22—Подача