со со со м

ОО

со

Изобретение относится к вычислительной технике и может быть использвано в информационно-преобразовательных устройствах, в частности в ана- лого-цифровом преобразователе с извлечением квадратного корня, реали- ззтощем принцип последовательных приближений.

Цель изобретения - расширение % класса решаемых задач за счет обеспечения возможности вычисления квадратов последовательных приближений исходного числа.

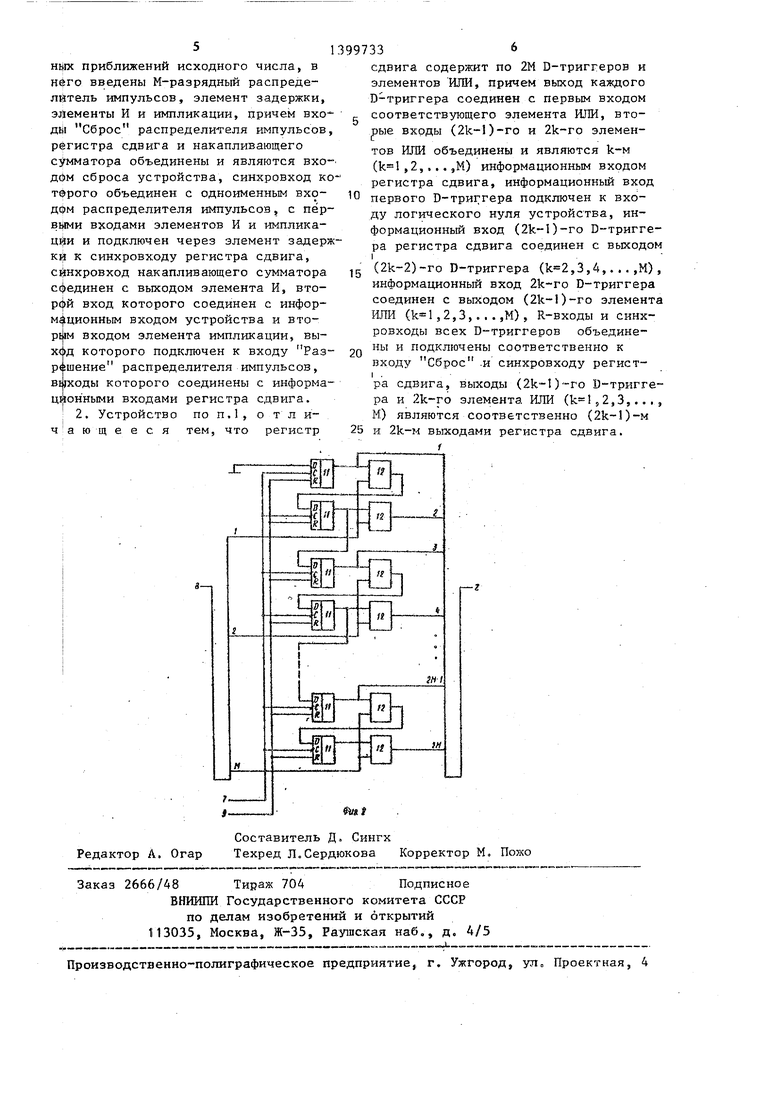

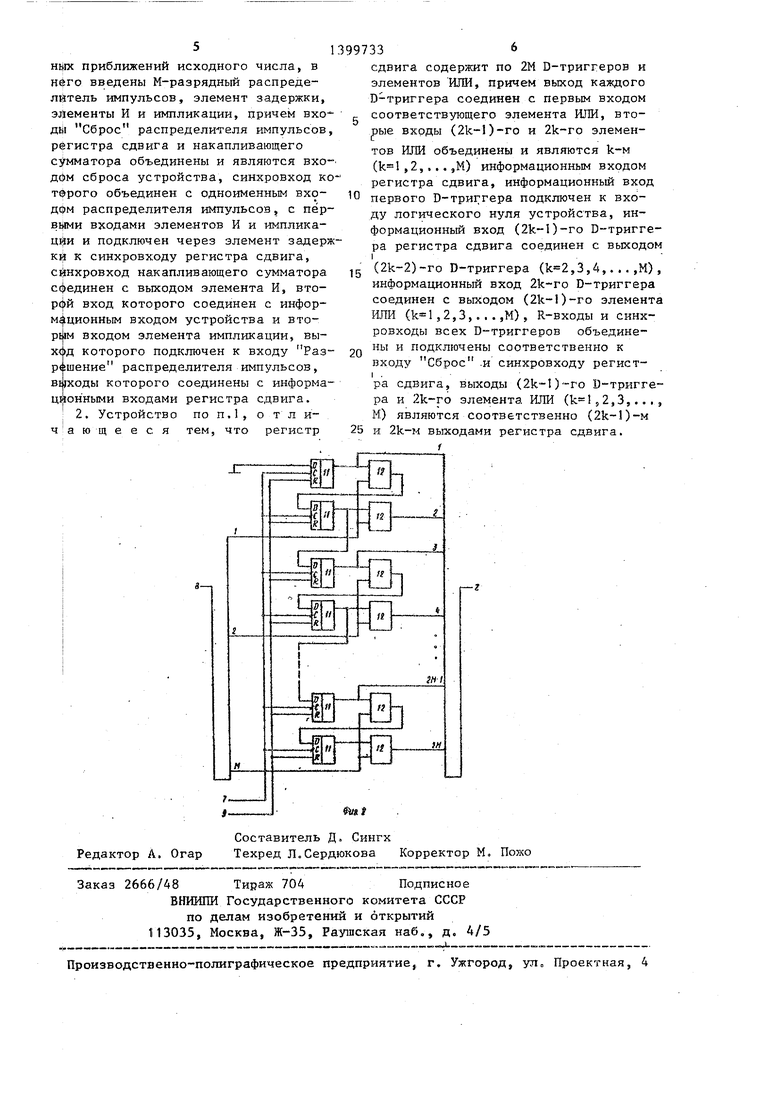

На фиг.1 представлена схема уст- ройства; на фиг.2 - схема регистра сдвига.

Устройство содержит М-разрядный распределитель 1 импульсов, регистр 2 сдвига, накапливающий сумматор 3, элемент 4 задержки, элемент 5 импликации, элемент И 6, устройство имеет синхровход 7, информационный вход 8, вход 9 Сброс и выходы 10.

Регистр сдвига образуют D-триг- ; геры 11 и элементы ИЛИ 12, Устройство работает следующим об- разом.

Исходное число в последователь

йом коде старшими разрядами вперед поступает на информационньй вход устройства, каждый k-й разряд Ck- «I ,2,3,.., ,М) сопровождается синхроимпульсом на сийхровходе устройства. До прихода 1-го разряда подачей еди- йичного сигнала на вход Сброс устройства обеспечивается установка распределителя 1 в первое состояние и установка в нуль регистра 2 и на-г капливающего сзшматора 3. Таким обра зом, имеют место

8„ о; z, о.

а,ь

где Sf, - содержимое накапливающего

сзгмматора на нулевом такте; 2д - содержимое регистра сдвига

на нулевом такте.

Рассмотрим работу устройства на такте. Пусть (Х.. « 0. Тогда на выходе элемента И 6 имеет место сиг- кал уровня логического нуля, который и постуггает на синхровход-накапли- ванядего сумматора 5. Поэтому содержи- мое накапливающего сумматора 3 не изменяется, т.е вьтолняется

к(3)

где Sj - содержимое накапливающего сумматора на k-м такте. На выходе элемента 5 импликации имеет место сигнал логического нуля, который поступает на вход Разрешение распределителя 1. На всех выходах распределителя 1 устанавливаются сигналы логического нуля, которые поступают на вторые входы элементов ШШ регистра. 2. Поэтому информация баз искажения передается с выхода любого предыдущего D-триггера регистра сдвига на вход последующего. Тогда по переднему фронту синхроимпульса через время, определяемое элементом А задержки происходит сдвиг информации в регистре 2 вправо на один разряд, т.е.

ZK Z,.,/2,

(А)

0

5

0

5

5

г

где Z, - содержимое регистра сдви- на на k-M такте.

По заднему фронту синхроимпульса распределитель 1 переходит в следующее, (k+l)-e состояние.

Пусть oCj; I . Тогда синхровход накапливающего сумматора 3 через элемент И 6 поступает синхроимпульс, по переднему фронту которого изменяется содержимое накапливающего сумматора 3, а именно к содержимому накаплива- ющего сумматора прибавляется число, установленное на выходах регистра 2 , сдвига. Это число отличается от содержимого регистра 2 (Z,) на величину . Действительно, на вход Разрешение распределителя 1 поступает сигнал логической единицы с выхода элемента 5 импликации, на k-M вькоде распределителя 1 присутствует сигнал логической единицы, который попадает на вторые входы (2k-l)-ro и 2k-ro элементов ИЛИ, вследствие чего , 2k-й выход регистра сдвига принудительно устанавливается в единицу, что соответствует появлению на 2k-M входе накапливающего сумматора, сигнала с весом I Таким образом, на выходах регистра 2

устанавливается число Z., +

2(M-.k) +2 . Поэтому по переднему фронту

синхродатульса содержимое накапливающего сумматора становится равным

8ц Sk., - Zk., + . (5) Через Время, определяемое элементом 4 задержки, по переднему фронту

синхроимпульса в регистре 2 сдвига аналогично описанному происходит сдвиг вправо на один разряд, т.е. осуществляется операция Z., /2. При этом одновременно происходит принудительная установка в единицу выхода (2k-I)-ro элемента ИЛИ, подключенного к входу 2k-ro D-триггера. В результате к содержимому регистра сдвига добавляется т.е. имеет место

Z. /2 2 Дсжажем методом математической ин индукции, что для любого

А,. 2

м-к

А;

(12) (13)

-g ю

При k О согласно (П) А, О, ;а в силу (9) и (10) S 0; Z, О, т.е. в исходном состоянии соотношения (12) и (13) вьтолняются.

Пусть на некотором (k-l)-M такте имеют место

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Вычислительное устройство | 1986 |

|

SU1355974A1 |

| Автокоррелятор | 1989 |

|

SU1617447A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство параллельной обработки видеоинформации | 1989 |

|

SU1651299A1 |

| Устройство для возведения в степень | 1976 |

|

SU888106A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Устройство для выполнения матричных операций | 1986 |

|

SU1388897A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

Изобретение относится к вычислительной и информационной технике и может быть использовано в информационно-преобразовательных устройствах, в частности в аналого-цифровом преобразователе, с извлечением квадратного корня,реализующем принцип последовательных приближений. Цель изобретения - расширение функциональных возможностей за счет вычисления квадратов последовательных приближений исходного числа. Устройство содержит распределитель импульсов I, регистр сдвига 2, накапливающий сумматор 3, элемент задержки 4, элемент импликации 5, элемент И 6. Устройство имеет синхро- вход 7, информационный вход 8, вход Сброс 9, выходы 10; регистр сдвига 2 содержит D-триггеры, элементы ИЛИ, 1 з.п.ф-лы, 2 ил. (Л

По заднему фронту синхроимпульса распределитель I переходит в следующее, (k+l)-e состояние.

Объединив (3),(4) и (5),(6), можно записать в общем виде зависимости, 20 которые реализуют устройство для любого :

S, S,., +ot./Z,, + (7)

7 7 /О j.i о2()

Zj, ZK.,/2 .2

причем

So 0; Z, О

Пример. Пусть требуетвести в квадрат число 7 (111 ном коде).

Согласно (7) и (8) получим

S, О +1/0 и- Z, 0/2 + 1.

16 + 1/16 + 36; 16/2 + 1 -2 - 12; 36+.I/I2 + « 49;

Zj 12/2 + 1 2

г(-з)

что доказьшает справедливость соот- g ношения (13).

Формула изобретения

Итак, в этом примере в отличие от прототипа действительно на промежуточных этапах получены значения

S 16, S 36 - квадраты последова- 1.Устройство для возведения в тельных приближений исходного числа „ квадрат М-разрядных двоичных чисел. Проведем доказательство в общем ви- содержащее регистр сдвига, 2М-разряд- де. Обозначим через А, последователь- ные выходы которого соединены с ин- ное приближение исходного числа на формационными входами 2М-разродного k-M такте, его можно представить в накапливающего сумматора, выходы ко- видеgg торого являются выходами устройства,

о т л и ч а ю щ е вся тем, что, с целью расширения класса решаемых задач аа счет обеспечения возможности вычисления квадратов последовательM-tc

..oJ., ... 000...0-А., +eitt-2

(И)

всего М разрядов

k-i

k-i

А (. k-l J

k-l

(14) (15)

Тогда на следующем, k-M такте используя (.8), (11) и (14), получим

Z Z, ,/2 +W,2 - l(A

/2 +о, A,.,.к

)/

(А,.,..., ,. 2

JH-k

30

35

что доказывает справедливость соотношения (12), используя (7), (11) и (15) и учитывая, что oi. ° лучим

Su- Sk-.,.. -н « -А1.(А,, k-(

+ 2Afc., ()

40

у ч2 + (оги-г ) (А,,., )

Ч

что доказьшает справедливость соот- g ношения (13).

Формула изобретения

M-tc

51

НЙ1Х приближений исходного числа, в него введены М-разрядный распределитель импульсов, элемент задержки, эйементы И и импликации, причем вхо- дй Сброс распределителя импульсов, регистра сдвига и накапливающего сумматора объединены и являются вхо- Д0М сброса устройства, синхровход которого объединен с одноименным вхо- Д0М распределителя импульсов, с первыми входами элементов И и имплика- Ш|и и подключен через элемент задерж кй к синхровходу регистра сдвига, синхровход накапливающего сумматора с4(единен с выходом элемента И, вто- рфй вход которого соединен с инфор- мфционным входом устройства и вто- рмм входом элемента импликации, выход которого подключен к входу Раз- р« шение распределителя импульсов, В1рсоды которого соединены с информа- цйон ными входами регистра сдвига.

: 2. Устройство по п.1, о т л и- ю щ е е с я тем, что регистр

10

3997336

сдвига содержит по 2М D-триггеров и элементов ИЛИ, причем выход каждого D-триггера соединен с первым входом

(- соответствующего элемента ИЛИ, вторые входы (2k-l)-ro и 2k-ro элементов ИЛИ объединены и являются k-м ( ,2,... ,М) информационным входом регистра сдвига, информационный вход первого D-триггера подключен к входу логического нуля устройства, информационный вход ()-ro D-триггера регистра сдвига соединен с выходом I.

(2k-2)-ro D-триггера (,3,4,...,М), информационный вход 2k-ro D-триггера соединен с выходом (2k-l)-ro элемента

ИЛИ ( ,2,3,. . . ,М) , R-входы и синх- ровходы всех D-триггеров объединены и подключены соответственно к

входу Сброс .и синхровходу регист- I .

ра сдвига, выходы (2k-l)-ro D-триггера и 2k-ro элемента ИЛИ (,2,3,..., М) являются соответственно (2k-)-M 25 и 2k-M выходами регистра сдвига.

15

20

| Квадратор | 1973 |

|

SU475619A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО для ВОЗВЕДЕНИЯ ЧИСЕЛ В СТЕПЕНЬ ЧЕТЬ[РЕ | 0 |

|

SU290279A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-18—Подача