1128

Изобретение относится к вычислительной технике и может быть использовано для . аппаратной реап изации операции вычисления квадратной функции в универсальных и специализированных вычислителях.

Целью изобретения является повышение быстродействия устройства.

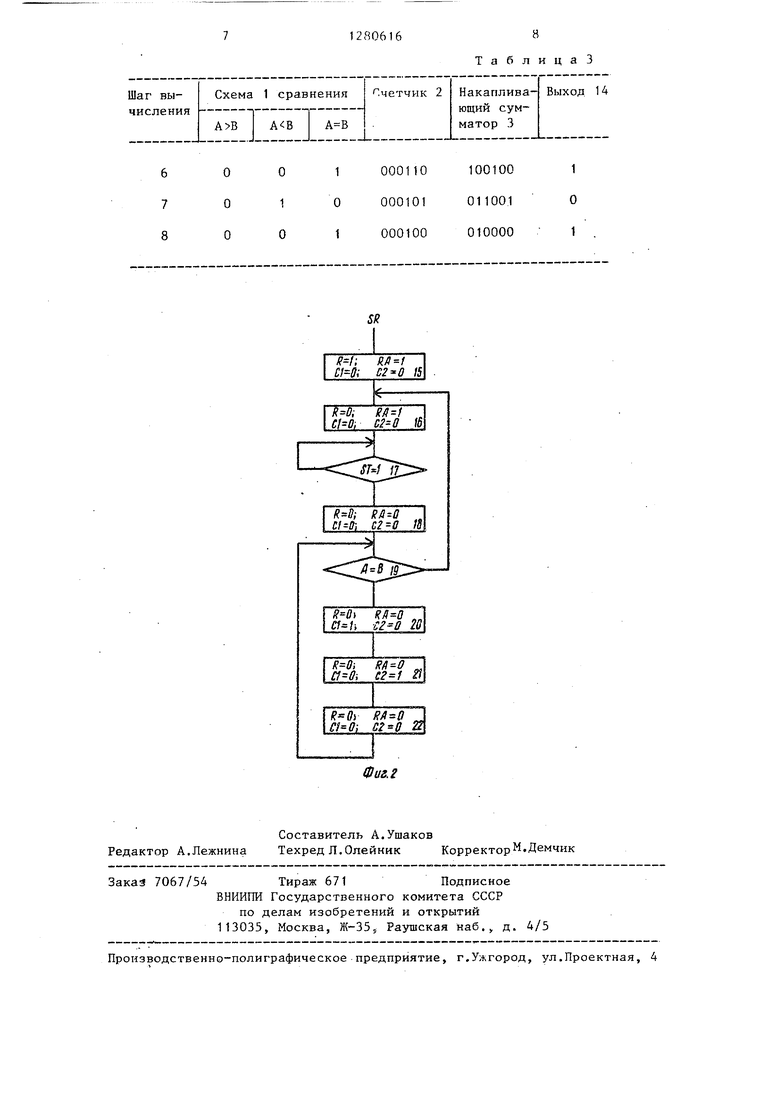

На фиг.1 показана функциональная схема предлагаемого устройства; на фиг.2 - граф-схема алгоритма работы блока управления (ГСА).

Устройство содержит схему 1 срав

нения, счетчик 2, мультиплексор 3, накапливающий сумматор 4, первый и второй элементы И 5 и 6, блок 7 управления, вход 8 аргумента, выход 9 результата и шины 10-12, причем схема 1 сравнения и мультиплексор 3 являются устройствами комбинационного типа, счетчик 2 и накапливающий сумматор 4 - синхронного типа, а блок управления 7 реализован в виде микропрограммного устройства.

Принцип работы устройства основан на вычислении квадратичной функции, представленной в виде следующих рекуррентных соотношений:

y(X+1)y(X)+h(x); (1) h(x+1)h(x)+2; (2) y(x)y(X+1)-h(x); (3) h(x)h(x+1)-2. (4) Начальные условия у(0)0; h(0)1, У(Х), yCX+D - значения функции на предыдущем и последующем шагах вычисления; h(x), h(x+1) - значения приращений функций на предыдущем и последующем шагах вычисления.

Очевидно, что выражения (3) и (4) являются следствием соответствующих выражений (1) и (2).

Условием окончания вычислительного процесса является равенство значений кода входного аргумента X и

При поступлении данных на вход 8 аргумента с входа 13 запуска устройства поступает единичный сигнал , по которому четвертый выход блока 7 управления переходит в нулевое состояние, сигнал готовности данных RA становится равным нулю (вершина 18 ГСА), а блок 7 управления переходит в режим проверки единичного сигнала равенства данных , поступающего с третьего выхода схемы 1 5 сравнения (вершина 19 ГСА). При выполнении этого условия, т.е. равенства входного кода аргумента X, поступающего с входа 8, со значением выходного кода счетчика 2, на четвертом

20

25

30

35

40

выходе схемы 7 управления, а следовательно, и на выходе 14 готовности результата устанавливается единичный сигнал (вершина 16 ГСА). В противном случае блок 7 управления вырабатывает на втором и третьем выходах последовательность импульсных сигналов С1 и С2 (вершины 20-22 ГСА), инициализирующих вычислительный процесс до выполнения условия (вершина 19 ГСА).

Вычислительный процесс происходит следующим образом.

Если значение входного кода аргумента X больше выходного кода счетчика 2, т.е. , то на выходе больше схемы 1 сравнения будет сформирован единичный сигнал, по которому прямые выходы счетчика 2 через первые информационные входы мультиплексора 3 подключатся к N-1 старшим разрядам информационного входа накапливающего сумматора 4, а элемент И 5 разрешит прохождение тактирующих импульсов С2 на суммирующий вход

кода с выхода реверсивного счетчика2, 45 счетчика 2. По тактирующему импульсу Устройство работает следующим об- С1 в накапливающем сумматоре 4 будет

сформирован результат следующего значения функции в соответствии с выраразом.

Исходное состояние устройства задается единичным сигналом , При этом блок 7 управления вырабатывает на первом выходе единичный импульсный сигнал сброса R (вершины 15 и 16 ГСА), по которому счетчик 2 и накапливающий сумматор 4 переходят в нулевое состояние, тактирующие импульсы С1 и С2 с второго и третьего выходов становятся равными нулю, а на выход готовности результата 14 с четвертого выхода поступает единич жением (1). По тактирующему импульсу 50 С2 в счетчик 2 запншестя единица, которая с учетом смещения разрядной сетки данных счетчика 2 относительно накапливающего сумматора 4 и единицы в его младшем информационном разряде 55 образует выражение (2), используемое на следующем шаге вычисления функции. Если значение входного кода аргумента X меньше выходного кода счетчика 2, т.е. , то нулевым сигнаньш сигнал готовности . Устройство переходит в режим ожидание сигнала пуска (вершина 17 ГСА).

При поступлении данных на вход 8 аргумента с входа 13 запуска устройства поступает единичный сигнал , по которому четвертый выход блока 7 управления переходит в нулевое состояние, сигнал готовности данных RA становится равным нулю (вершина 18 ГСА), а блок 7 управления переходит в режим проверки единичного сигнала равенства данных , поступающего с третьего выхода схемы 1 5 сравнения (вершина 19 ГСА). При выполнении этого условия, т.е. равенства входного кода аргумента X, поступающего с входа 8, со значением выходного кода счетчика 2, на четвертом

0

5

0

5

0

выходе схемы 7 управления, а следовательно, и на выходе 14 готовности результата устанавливается единичный сигнал (вершина 16 ГСА). В противном случае блок 7 управления вырабатывает на втором и третьем выходах последовательность импульсных сигналов С1 и С2 (вершины 20-22 ГСА), инициализирующих вычислительный процесс до выполнения условия (вершина 19 ГСА).

Вычислительный процесс происходит следующим образом.

Если значение входного кода аргумента X больше выходного кода счетчика 2, т.е. , то на выходе больше схемы 1 сравнения будет сформирован единичный сигнал, по которому прямые выходы счетчика 2 через первые информационные входы мультиплексора 3 подключатся к N-1 старшим разрядам информационного входа накапливающего сумматора 4, а элемент И 5 разрешит прохождение тактирующих импульсов С2 на суммирующий вход

жением (1). По тактирующему импульсу С2 в счетчик 2 запншестя единица, которая с учетом смещения разрядной сетки данных счетчика 2 относительно накапливающего сумматора 4 и единицы в его младшем информационном разряде образует выражение (2), используемое на следующем шаге вычисления функции. Если значение входного кода аргумента X меньше выходного кода счетчика 2, т.е. , то нулевым сигна3

лом с выхода больше схемы 1 сравнения инверсные выходы счетчика 2 через вторые информационные входы мультиплексора 3 нодключатся к N-1 старшим разрядам информационного вхда накапливающего сумматора 4, а на его вход переноса поступит единич- ньй сигнал, который образуется путе инвертирования нулевого логического сигнала с шины 11 информационного нуля в мультиплексоре 3. Этим осуществляется образование дополнительного кода отрицательного приращения функции h(x) при поступлении на вхо 8 аргумента X, значение которого меньше предыдущего.

Вычислительный пр.оцесс при этом происходит аналогично описанному за исключением того, что при этом единичным сигналом с выхода меньше схемы 1 сравнения разрешается проходение тактирующих сигналов С2 через элемент И 6 на вычитающий вход счетчика 2.

Таким образом, при вычислении ел дующего значения квадратичной функц используется предыдущее значение функции, что позволяет повысить бысродействие устройства при отработке малых приращений аргумента. Кроме этого, устройство имеет высокую помехоустойчивость к единичным сбоям входных данных, если они не приводя к изменению сигналов на выходах больше или меньше схемы 1 сравнения и не сказываются на конечном результате, В противном случае устройство выполнит обратное требуемом действие (например, вмес.то суммирования выполнит вычитание приращения функции), однако после восстановления значения аргумента процесс вычисления функции будет продолжен до момента получения истинного значени результата,

Пример 1 , Вычислительный про цесс возведения в квадрат числа 6 (000110,2) начинается после поступления сигнала начальной установки SR При этом состояние выходов ,I 1 сравнения, счетчика 2, накапливающего сумматора А и сигнала готовности RA на клемме 14 будет изменяться в соответствии с табл. 1.

П р и м е р 2, Предположим, что после четвертого вычисления произошел сбой, в результате которого на входе образовался нулевой код. Посл выполнения текущего шага вычисления

JQ5

20

25 о 5

5

0

0

5

данные на входе восстановились и стали равными 6 (000110), Вычислительный процесс в этом случае будет проходить в соответствии с табл,2.

Из табл,2 видно, что в отличие от примера 1 время вычисления увеличилось на два шага, однако конечный результат остался без изменения.

П р и м е р 3. Предположим, что значение аргумента по сравнению с примером 1 изменилось и стало равным . 4, Тогда вычислительный процесс будет протекат в соответствии с табл.3.

Таким образом, если для возведения в квадрат в примере 1 потребовалось 4 шага вычислений, то в примере 3 возведение в квадрат произошло за 2 шага.

Чем больше величина входного аргумента и меньше величина его приращения, тем значительнее повышается быстродействие устройства.

Формула изобретения

Устройство для возведения в квадрат, содержащее схему сравнения, счетчик, накапливающий сумматор, два элемента И и блок управления, первый , и второй информационные входы схемы сравнения соединены с входом аргумента устройства и с прямым выходом счетчика, вход сброса которого подключен к одноименному входу акапли- ва,ющего сумматора и к первому выходу блока управления, выход накапливающего сумматора является выходом ре- зультата устройства, второй и третий выходы блока управления подключены к входу синхронизации -накапливающего сумматора и к первым входам первого и второго элементов И, входы начальной установки и запуска блока управления являются одноименными входами устройства, выход больще схемы сравнения подключен к второму входу первого элемента И, выход которого подключен к суммирующему входу счет- .чика, отличающееся тем, что, с целью повышения быстродействия устройства, D него введен мультиплексор, а блок управления выпол-; нен микропрограммным, входы младших разрядов первого и второго информа- ционн1з1Х входов мультиплексора подключены к шине информационного нуля устройства, входы старших разрядов первого и второго информационных входов мультиплексора подключены к прямым и инверснь выходам счет1; ика,

51280616

младший разряд информационного входа и вход переноса накапливающего сумматора подключены к шине информационной единицы устройства и к высумматора соответственно, выходы меньше и равно схемы сравнения

подключены к второму входу второго элемента Инк входу признака равен ходу младшего разряда мультиплексора 5 ства блока управления, выход второго соответственно, вход управления и элемента И подключен к вычитающему выходы старших разрядов ьгультиплексо- входу счетчика, четвертый выход бло- ра подключены к выходу больше схе- ка .управления является выходом мы сравнения и к старшим разрядам готовности результата устройст - информационного входа накапливающего fO ва.

сумматора соответственно, выходы меньше и равно схемы сравнения

.

, С2 0 IS

ТаблицаЗ

16

) „„ 2S

112 О П

Редактор А.Лежнина

Составитель А.Ушаков

Техред Л.Олейник Корректор М-Демчик

Заказ 7067/54 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-ЗЗ, Раушская наб, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления степенной функции | 1986 |

|

SU1348831A1 |

| Вычислительное устройство | 1984 |

|

SU1236467A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Устройство для деления | 1985 |

|

SU1339553A1 |

| Устройство для умножения | 1986 |

|

SU1388852A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для извлечения квадратного корня | 1980 |

|

SU1099318A1 |

| Цифровой фильтр | 1987 |

|

SU1418756A1 |

Изобретение относится к вычислительной технике и может быть использовано для аппаратной реализации операции вычисления квадратной функции в универсальных и специализированных вычислителях. Изобретение позволяет выполнять итерационное возведение в квадрат аргумента с увеличением быстродействия устройства при уменьшении величины его приращения. Работа устройства основана на следующих рекурсивных выражениях: у(х+1)y(x)+h(x); h(x+1)h(x)+2; у(0)0, h(0)1, где у(х) и у(х+1), h(x) и h(x+1) - значения функции и приращения функции на предыдущем и последующем шагах вычисления соответственно. Устройство содержит схему сравнения 1, счетчик 2, мультиплексор 3, накапливающий сумматор 4, первый 5 и второй 6 элементы И и блок 7 управления, выполненный микропрограммно. Устройство имеет высокую помехоустойчивость к единичным сбоям входных данных. На вход 8 аргумента подается двоич- ньш код аргумента, результат формируется на выходе 9 результата. Признаком окончания вычисления является появление сигнала на выходе 14 готовности результата устройства, 2 ил., 3 табл. i с 1чэ 00 S у (Х

| Устройство для возведения в квадрат | 1979 |

|

SU894705A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР ,№ 1010620, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-02-28—Подача