(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадрата и квадратного корня | 1986 |

|

SU1386991A2 |

| Устройство для вычисления квадрата и квадратного корня | 1983 |

|

SU1120320A1 |

| Вычислительное устройство | 1983 |

|

SU1167605A1 |

| Устройство для вычисления степенной функции | 1986 |

|

SU1348831A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Арифметическое устройство | 1987 |

|

SU1476459A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Устройство для программного управления | 1983 |

|

SU1160367A1 |

| Коррелятор | 1983 |

|

SU1130874A1 |

| Устройство для вычисления эквивалентного уровня звуковой экспозиции | 1988 |

|

SU1640556A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах и цифровых измерительных приборах. Изобретение позволяет вести обработку информации, представленной как в виде число-импульсного кода, так и в виде двоичного кода. Устройство для вычисления квадрата и квадратного корня содержит реверсивный счетчик, элемент задержки, накапливающий сумматор, три элемента И, три элемента ИЛИ, два элемента 2 И-ИЛИ, три мультиплексора, схему сравнения, управляемый генератор прямоугольных импульсов с соответствующими связями. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах и цифровых измерительных приборах при обработке информации, представленной число-импульсным и двоичным параллельным кодома

Цель изобретения - расширение области применения за счет возможности вычисления как в число-импульсном, так и в двоичном параллельном коде.

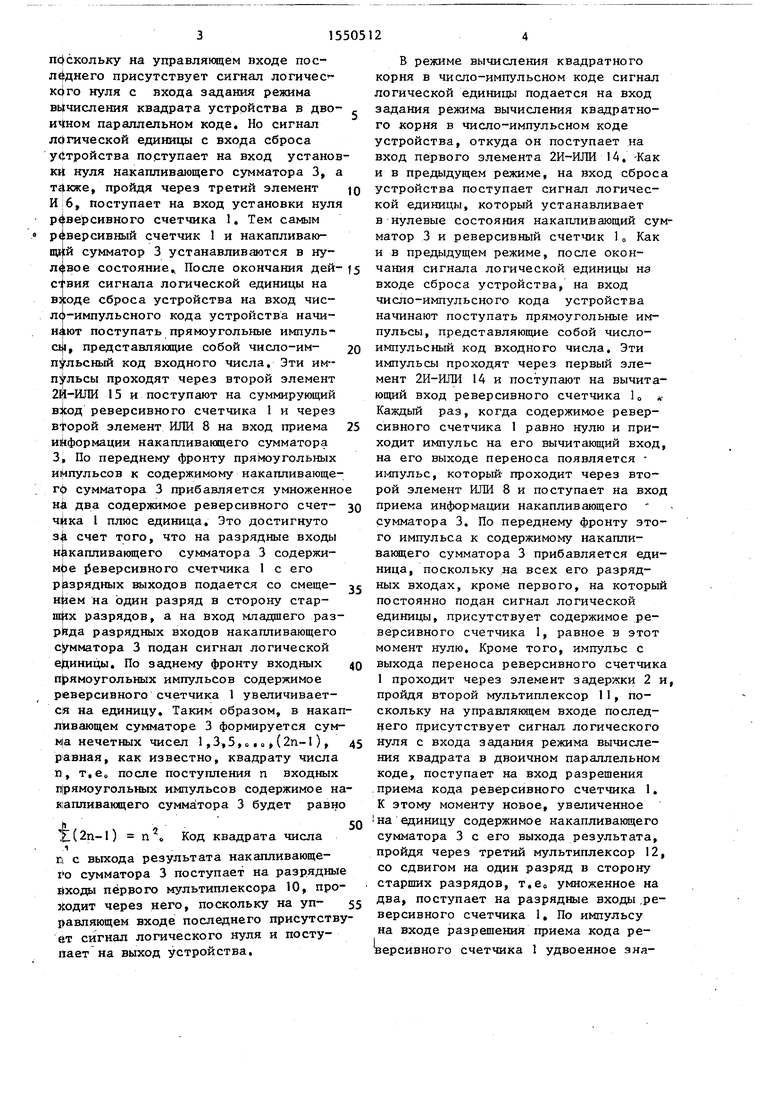

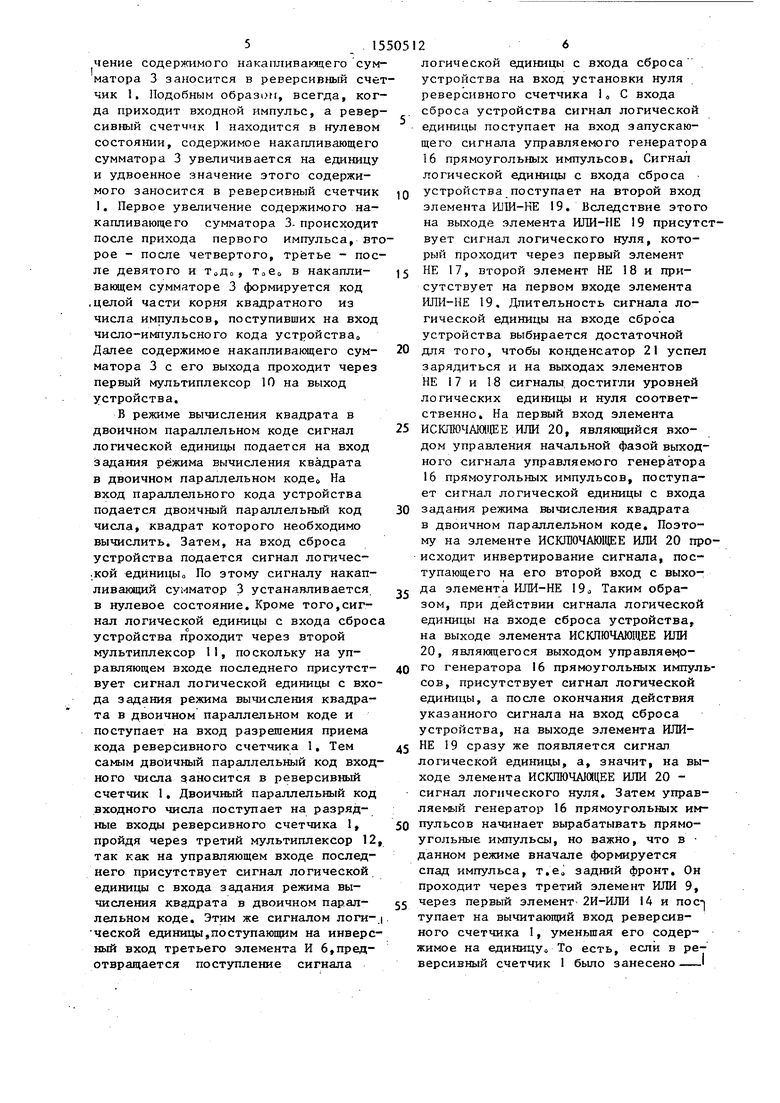

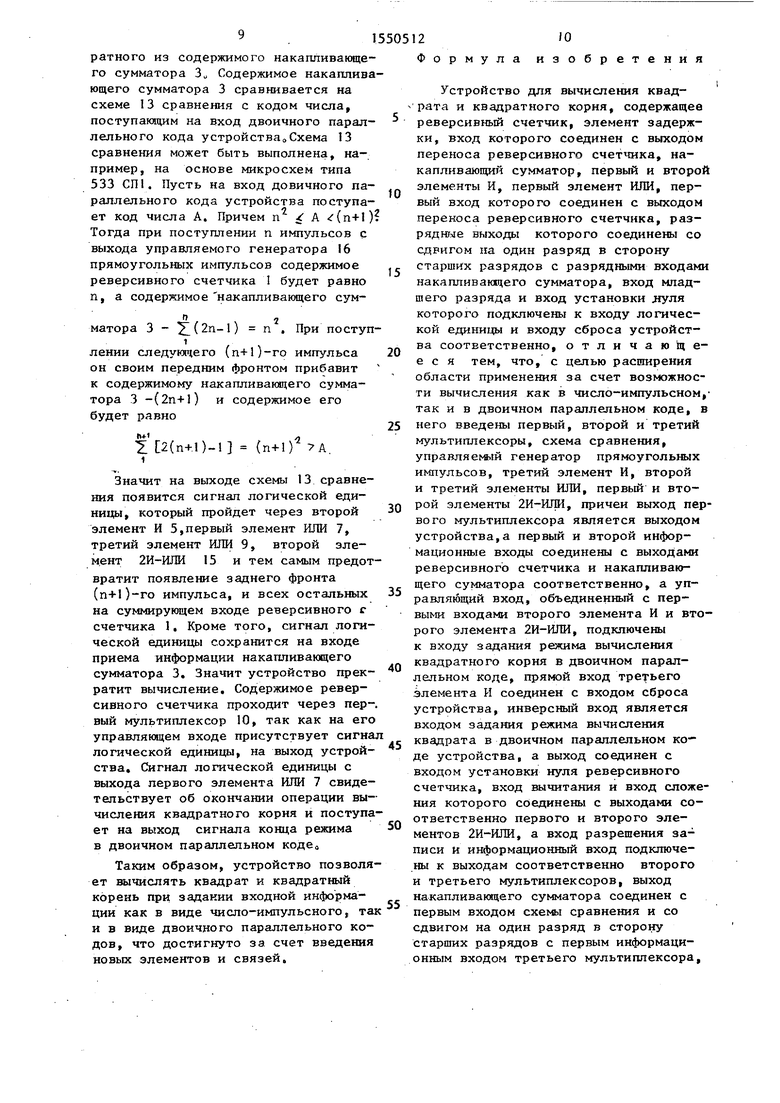

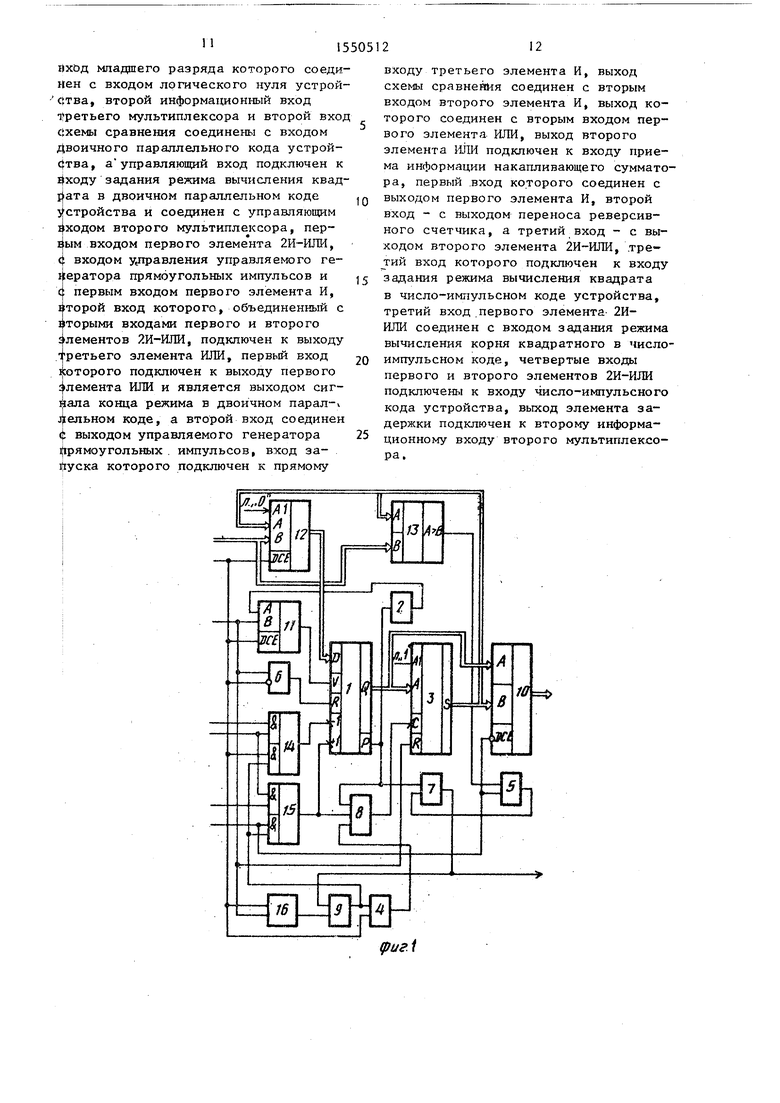

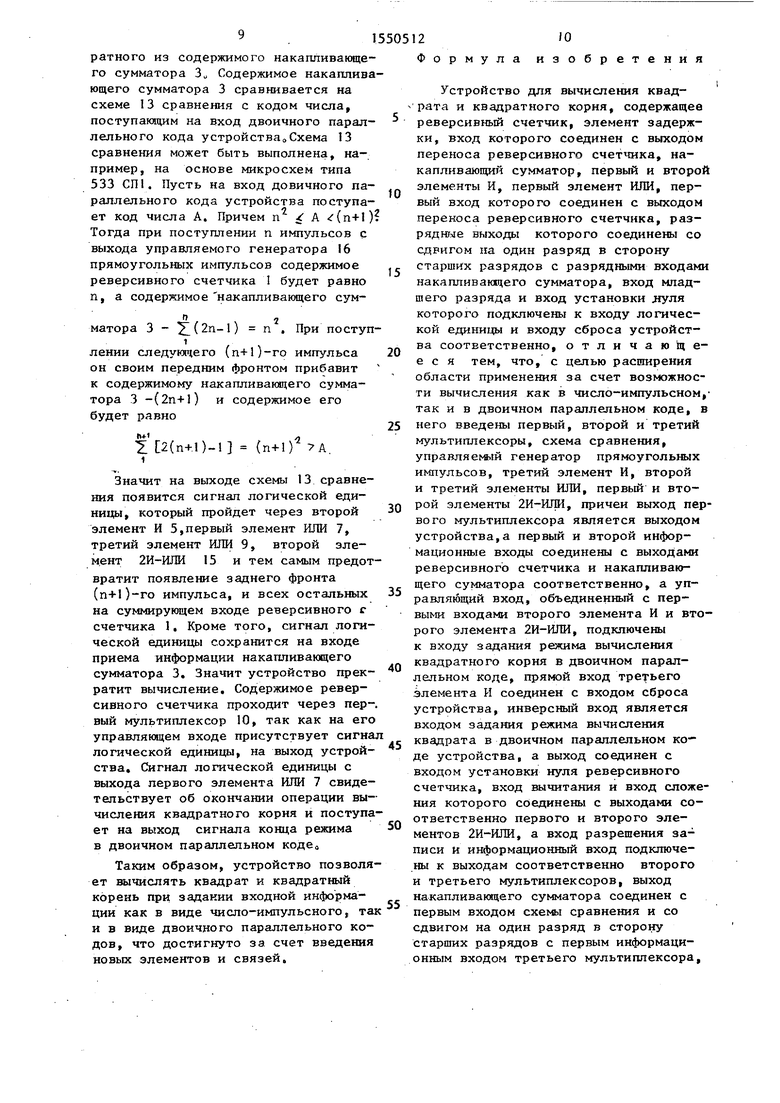

На фиг.1 представлена функциональная схема устройства; на фиг„2 - схема управляемого генератора прямоугольных импульсов0

Устройство содержит реверсивный счетчик I, элемент задержки 2, накапливающий сумматор 3, элементы И 4 - 6, элементы ИЛИ 7-9, мультиплексоры 10 - 12, схему 13 сравнения, элементы 2И-ИЛИ 14 и 15, управляемый генератор 16 прямоугольных импульсов, элементы НЕ 17 и 18, элемент ИЛИ-НЕ 19, элемент 20 ИСКЛЮЧАЮЩЕЕ ИЛИ и конденсатор 21.

Устройство работает следующим образом.

Сначала устанавливается режим работы устройства, для этого на вход задания нужного режима подается сигнал логической единицы, а на входы задания других режимов подаются сигналы логического нуля. Рассмотрим работу устройства в режиме вычисления квадрата в число-импульсном коде. На вход задания режима вычисления квадрата в число-импульсном коде элемента 2И-ИЛИ 15 подается сигнал логической единицы. Затем на вход сброса устройства подается сигнал логической единицы, который не проходит через второй мультиплексор 11,

20

поскольку на управляющем входе пос- лйднего присутствует сигнал логичес кого нуля с входа задания режима вычисления квадрата устройства в дво- ичном параллельном коде. Но сигнал логической единицы с входа сброса устройства поступает на вход установки нуля накапливающего сумматора 3, а т4кже, пройдя через третий элемент JQ И 6, поступает на вход установки нуля реверсивного счетчика 1. Тем самым реверсивный счетчик 1 и накапливающий сумматор 3 устанавливаются в нулевое состояние После окончания дей- 15 ствия сигнала логической единицы на сброса устройства на вход чис- л(| -импульсного кода устройства начи- поступать прямоугольные импуль- ciji, представляющие собой число-им- п льсный код входного числа. Эти им-- проходят через второй элемент 2Й-ИЛИ 15 и поступают на суммирующий вйод реверсивного счетчика 1 и через Bfopou элемент ИЛИ 8 на вход приема информации накапливающего сумматора 3, По переднему фронту прямоугольных импульсов к содержимому накапливающе- сумматора 3 прибавляется умноженное ни два содержимое реверсивного счет- 30 чйка i плюс единица. Это достигнуто зЈ счет того, что на разрядные входы накапливающего сумматора 3 содержи- реверсивного счетчика 1 с его разрядных выходов подается со смещением на один разряд в сторону стар- пфх разрядов, а на вход младшего разряда разрядных входов накапливающего сумматора 3 подан сигнал логической единицы. По заднему фронту входных прямоугольных импульсов содержимое реверсивного счетчика 1 увеличивается на единицу. Таким образом, в накапливающем сумматоре 3 формируется сумма нечетных чисел 1,3,5,0.„,(2п-1), Д5 равная, как известно, квадрату числа

25

35

40

п,

т,е„ после поступления п входных

Прямоугольных импульсов содержимое накапливающего сумматора 3 будет равно

Х(2п-1) п2„ Код квадрата числа 1

п с выхода результата накапливающего сумматора 3 поступает на разрядные Входы первого мультиплексора 10, про- гЮдит через него, поскольку на уп- 5 равляющем входе последнего присутствует сигнал логического нуля и поступает на выход устройства.

0

Q 5 0 5

5

5

0

5В режиме вычисления квадратного корня в число-импульсном коде сигнал логической единицы подается на вход задания режима вычисления квадратного корня в число-импульсном коде устройства, откуда он поступает на вход первого элемента 2И-ИЛИ 14. -Как и в предыдущем режиме, на вход сброса устройства поступает сигнал логической единицы, который устанавливает в нулевые состояния накапливающий сумматор 3 и реверсивный счетчик 10 Как и в предыдущем режиме, после окончания сигнала логической единицы на входе сброса устройства, на вход число-импульсного кода устройства начинают поступать прямоугольные импульсы, представляющие собой число- импульсный код входного числа. Эти импульсы проходят через первый элемент 2И-ИЛИ 14 и поступают на вычитающий вход реверсивного счетчика 10 Каждый раз, когда содержимое реверсивного счетчика 1 равно нулю и приходит импульс на его вычитающий вход, на его выходе переноса появляется импульс, который проходит через второй элемент ИЛИ 8 и поступает на вход приема информации накапливающего сумматора 3. По переднему фронту этого импульса к содержимому накапливающего сумматора 3 прибавляется единица, поскольку на всех его разрядных входах, кроме первого, на который постоянно подан сигнал логической единицы, присутствует содержимое реверсивного счетчика 1, равное в этот момент нулю, Кроме того, импульс с выхода переноса реверсивного счетчика 1 проходит через элемент задержки 2 и, пройдя второй мультиплексор 11, поскольку на управляющем входе последнего присутствует сигнал логического нуля с входа задания режима вычисления квадрата в двоичном параллельном коде, поступает на вход разрешения приема кода реверсивного счетчика 1. К этому моменту новое, увеличенное на единицу содержимое накапливающего сумматора 3 с его выхода результата, пройдя через третий мультиплексор 12, со сдвигом на один разряд в сторону старших разрядов, т,е0 умноженное на два, поступает на разрядные входы .реверсивного счетчика 1. По импульсу на входе разрешения приема кода реверсивного счетчика 1 удвоенное зла515

чение содержимого накапливающего сумматора 3 заносится в реверсивный счетчик 1. Подобным образом, всегда, кот- да приходит входной импульс, а реверсивный счетчик 1 находится в нулевом состоянии, содержимое накапливающего сумматора 3 увеличивается на единицу и удвоенное значение этого содержимого заносится в реверсивный счетчик I. Первое увеличение содержимого накапливающего сумматора 3 происходит после прихода первого импульса, второе - после четвертого, третье - после девятого и т0д0, т0ео в накапли- вающем сумматоре 3 формируется код .целой части корня квадратного из числа импульсов, поступивших на вход число-импульс но го кода устройства,, Далее содержимое накапливающего сум- матора 3 с его выхода проходит через первый мультиплексор 10 на выход устройства.

В режиме вычисления квадрата в двоичном параллельном коде сигнал логической единицы подается на вход задания режима вычисления квадрата в двоичном параллельном кодей На вход параллельного кода устройства подается двоичный параллельный код числа, квадрат которого необходимо вычислить. Затем, на вход сброса устройства подается сигнал логической единицы,, По этому сигналу накапливающий сумматор 3 устанавливается в нулевое состояние. Кроме того,сигнал логической единицы с входа сброса устройства проходит через второй мультиплексор 11, поскольку на управляющем входе последнего присутст- вует сигнал логической единицы с входа задания режима вычисления квадрата в двоичном параллельном коде и поступает на вход разрешения приема кода реверсивного счетчика 1, Тем самым двоичный параллельный код входного числа заносится в реверсивный счетчик 1. Двоичный параллельный код входного числа поступает на разрядные входы реверсивного счетчика 1, пройдя через третий мультиплексор 12, так как на управляющем входе последнего присутствует сигнал логической единицы с входа задания режима вычисления квадрата в двоичном парал- лельном коде. Этим же сигналом логи- | ческой единицы„поступающим на инверсный вход третьего элемента И 6,предотвращается поступление сигнала

126

логической единицы с входа сброса устройства на вход установки нуля реверсивного счетчика 1 , С входа сброса устройства сигнал логической единицы поступает на вход запускающего сигнала управляемого генератора 16 прямоугольных импульсов. Сигнал логической единицы с входа сброса устройства поступает на второй вход элемента ИЛИ-НЕ 19. Вследствие этого на выходе элемента ИЛИ-НЕ 19 присутсвует сигнал логического нуля, который проходит через первый элемент НЕ 17, второй элемент НЕ 18 и присутствует на первом входе элемента ИЛИ-НЕ 19. Длительность сигнала логической единицы на входе сброса устройства выбирается достаточной для того, чтобы конденсатор 21 успел зарядиться и на выходах элементов НЕ 17 и 18 сигналы достигли уровней логических единицы и нуля соответственно. На первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20, являющийся входом управления начальной фазой выходного сигнала управляемого генератора 16 прямоугольных импульсов, поступает сигнал логической единицы с входа задания режима вычисления квадрата в двоичном параллельном коде. Поэтому на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 20 происходит инвертирование сигнала, поступающего на его второй вход с выхода элемента ИЛИ-НЕ 19а Таким образом, при действии сигнала логической единицы на входе сброса устройства, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20, являющегося выходом управляемого генератора 16 прямоугольных импульсов, присутствует сигнал логической единицы, а после окончания действия указанного сигнала на вход сброса устройства, на выходе элемента ИЛИ- НЕ 19 сразу же появляется сигнал логической единицы, а, значит, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20 - сигнал логического нуля. Затем управляемый генератор 16 прямоугольных импульсов начинает вырабатывать прямоугольные импульсы, но важно, что в данном режиме вначале формируется спад импульса, т.е,, задний фронт. Он проходит через третий элемент ИЛИ 9, через первый элемент 2И-ИЛИ 14 и по с- тупает на вычитающий вход реверсивного счетчика 1, уменьшая его содержимое на единицу То есть, если в реверсивный счетчик 1 было занесено

значение п по сигналу логической единицы на входе сброса устройства, то теперь содержимое счетчика становятся равным п-1. Кроме того, импульсы с выхода управляемого генератора 16 j пройдя третий элемент ИЛИ 9, элемент И 4 и второй элемент 8, поступают на вход приема информации накапливающего сумматора 3 и по переднему фронту прибавляют к содержимому последнего удвоенное содержимое реверсивного счетчика 1 пхюс единица. То есть по первому им- пульсу содержимое накапливающего сумматора станет равным 2п-2+1 2п-1. Затем, по заднему фронту это10

15

ГС С

43

МА

импульса содержимое реверсивного етчика 1 уменьшится еще на едини20

25

30

и станет равным п-2. По передне- фронту второго импульса к содержимому накапливающего сумматора 3 прибавляется 2п-4+1 2п-3 и т0До , в накапливающем сумматоре 3 накапливается сумма нечетных чисел. происходит до тех порр пока содержимое реверсивного счетчика 1 не станет равным нулю. Тогда при поступлении на его вычитающий вход оче- р дного импульса на его выходе пере- появляется сигнал логической единицы, который проходит через первый элемент ИЛИ 7, третий элемент -ИЛИ 9 и поступает на первый первого элемента И 4 и на вход первого элемента 2И-ИЛИ 14 Тем са- MI(IM предотвращается снятие сигнала логической единицы с вычитающего входа реверсивного счетчика 1 и входа пЬиема информации накапливающего40

сумматора 3. Работа схемы прекращается. Сигнал логической единицы с выхода первого элемента ИЛИ 7 является - сигналом конца режима в двоичном параллельном коде. Передним фронтом 45 последнего n-го импульса, т.е. когда содержимое реверсивного счетчика равно нулю, к содержимому накапливающего сумматора прибавляется единица. Таким образом, в накапливающем сумма- JQ торе накоплена сумма

Х(2п-1) пг. 1

Содержимое накапливающего сумматора 3 с его выходов результата проходит через первый мультиплексор 10 на выход устройства.

15505128

В режиме вычисления квадратного корня в двоичном параллельном коде сигнал логической единицы подается на вход задания режима вычисления квадратного корня в двоичном параллельном коде, откуда поступает на соответствующий вход второго элемента 2И-ИЛИ 15, на вход второго элемента ИЛИ 8 и на управляющий вход первого мультиплексора 10. На вход двоичного параллельного кода устройства подается двоичный параллельный код, квадратный корень которого необходимо вычислить. Этот код должен стоять на входе параллельного кода устройства все время вычисления- квадратного ; корня0 Далее подается сигнал логической единицы на вход сброса устройства Этим сигналом останавливается управляемый генератор 16 прямоугольных импульсов и устанавливаются в нулевое состояние реверсивный чик 1 и накапливающий сумматор 30 После окончания действия сигнала логической единицы на входе сброса устройства управляемый генератор 16 прямоугольных импульсов начинает выдавать на своем выходе прямоугольные импульсы. Причем, поскольку на входе управления начальной фазой управляемого генератора 16 присутствует, в данном режиме, сигнал логического нуля, который поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20, то сразу после окончания сигнала логической единицы на входе сброса устройства на выходе управляемого генератора 16 возникает передний фронт импульса. Импульсы с выхода управляемого генератора 16 прямоугольных импульсов проходят через третий элемент ИЛИ 9, второй элемент 2И-ИЛИ 15 и поступают на суммирующий вход реверсивного счетчика 1 и через второй элемент ИЛИ 8 на вход приема информации накапливающего сумматора 3. По переднему фронту импульсов к г содержимому накапливающего сумматора 3 прибавляется удвоенное содержимое реверсивного счетчика 1 плюс единица, а по заднему фронту к содержимому реверсивного счетчика 1 добавляется единица,т.е.,в накапливающем сумматоре 3 копится сумма нечетных чисел, равная квадрату числа, , находящегося в реверсивном счетчике 1, Т(,е, содержимое реверсивного счетчика 1 - есть целая часть корня квад35

55

у15

ратного из содержимого накапливающего сумматора 30 Содержимое накапливающего сумматора 3 сравнивается на схеме 13 сравнения с кодом числа, поступающим на вход двоичного парал- лельного кода устройства Схема 13 сравнения может быть выполнена, например, на основе микросхем типа 533 СП1. Пусть на вход довичного параллельного кода устройства поступает код числа А. Причем n2 A г(п+1) Тогда при поступлении п импульсов с выхода управляемого генератора 16 прямоугольных импульсов содержимое реверсивного счетчика 1 будет равно п, а содержимое накапливающего сум

матора 3 - (2n-l) п . При поступ1

лении следующего (n+l)-ro импульса он своим передним фронтом прибавит к содержимому накапливающего сумматора 3 -(2n+l) и содержимое его будет равно

IW

Z 2(n+l)-l (n+l) 7 А 1

Значит на выходе схемы 13 сравнения появится сигнал логической единицы, который пройдет через второй элемент И 5,первый элемент ИЛИ 7, третий элемент ИЛИ 9, второй элемент 2И-ИЛИ 15 и тем самым предотвратит появление заднего фронта (п-И)-го импульса, и всех остальных на суммирующем входе реверсивного с счетчика 1, Кроме того, сигнал логической единицы сохранится на входе приема информации накапливающего сумматора 3. Значит устройство прек ратит вычисление. Содержимое реверсивного счетчика проходит через пер-, вый мультиплексор 10, так как на его управляющем входе присутствует сигнал логической единицы, на выход устройства. Сигнал логической единицы с выхода первого элемента ИЛИ 7 свидетельствует об окончании операции вычисления квадратного корня и поступает на выход сигнала конца режима в двоичном параллельном кодеа

Таким образом, устройство позволяет вычислять квадрат и квадратный корень при задании входной информации как в виде число-импульсного, так и в виде двоичного параллельного кодов, что достигнуто за счет введения новых элементов и связей.

0

5

0

5

0

0 5 0

12Ю

Формула изобретения

Устройство для вычисления квадрата и квадратного корня, содержащее реверсивный счетчик, элемент задержки, вход которого соединен с выходом переноса реверсивного счетчика, накапливающий сумматор, первый и второй элементы И, первый элемент ИЛИ, первый вход которого соединен с выходом перекоса реверсивного счетчика, разряд ные выходы которого соединены со сдвигом на один разряд в сторону старших разрядов с разрядными входами накапливающего сумматора, вход младшего разряда и вход установки .нуля которого подключены к входу логической единицы и входу сброса устройства соответственно, отличающееся тем, что, с целью расширения области применения за счет возможности вычисления как в число-импульсном, так и в двоичном параллельном коде, в него введены первый, второй и третий мультиплексоры, схема сравнения, управляемый генератор прямоугольных импульсов, третий элемент И, второй и третий элементы ИЛИ, первый и второй элементы 2И-ИЛИ, причеи выход первого мультиплексора является выходом устройства,а первый и второй информационные входы соединены с выходами реверсивного счетчика и накапливающего сумматора соответственно, а управляющий вход, объединенный с первыми входами второго элемента И и второго элемента 2И-ИЛИ, подключены к входу задания режима вычисления квадратного корня в двоичном параллельном коде, прямой вход третьего элемента И соединен с входом сброса устройства, инверсный вход является входом задания режима вычисления квадрата в двоичном параллельном коде устройства, а выход соединен с входом установки нуля реверсивного счетчика, вход вычитания и вход сложения которого соединены с выходами соответственно первого и второго элементов 2И-ИЛИ, а вход разрешения записи и информационный вход подключены к выходам соответственно второго и третьего мультиплексоров, выход накапливающего сумматора соединен с первым входом схемы сравнения и со сдвигом на один разряд в сторону старших разрядов с первым информационным входом третьего мультиплексора,

йхйд младшего разряда которого соединен с входом логического нуля устройства, второй информационный вход третьего мультиплексора и второй вход Схемы сравнения соединены с входом Двоичного параллельного кода устрой- 4тва, а управляющий вход подключен к задания режима вычисления квад- в двоичном параллельном коде устройства и соединен с управляющим иходом второго мультиплексора, первым входом первого элемента 2И-ИЛИ, с: входом убавления управляемого генератора прямоугольных импульсов и с: первым входом первого элемента И, иторой вход которого, объединенный с иторыми входами первого и второго элементов 2И-ИЛИ, подключен к выходу третьего элемента ИЛИ, первый вход которого подключен к выходу первого элемента ИЛИ и является выходом сигнала конца режима в двоичном парал-х Цельном коде, а второй вход соединен t выходом управляемого генератора Прямоугольных импульсов, вход запуска которого подключен к прямому

0

5

0

5

входу третьего элемента И, выход схемы сравнения соединен с вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход второго элемента ИЛИ подключен к входу приема информации накапливающего сумматора, первый вход которого соединен с выходом первого элемента И, второй вход - с выходом переноса реверсивного счетчика, а третий вход - с выходом второго элемента 2И-ИЛИ, тре- тий вход которого подключен к входу задания режима вычисления квадрата в число-импульсном коде устройства, третий вход первого элемента- 2И- ИЛИ соединен с входом задания режима вычисления корня квадратного в число- импульсном коде, четвертые входы первого и второго элементов 2И-ИЛИ подключены к входу число-импульсного кода устройства, выход элемента задержки подключен к второму информационному входу второго мультиплексора.

фигЛ

Составитель Н,Рябуха Редактор Л0Пчолинская Техред М.Дидык

Заказ 273

Тираж 561

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Корректор Т.Палий

Подписное

| Мельников А.А | |||

| и др | |||

| Обработка частотных и временных импульсных сигналов | |||

| М.: Энергия, 1976, с.,89, рис.740 Авторское свидетельство СССР № 1120320, кп | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-15—Публикация

1987-08-17—Подача