Hav.ycm J«

со

00

Изобретение относится к вычислительной технике и может быть использовано в специализированных процессорах для вычисления элементарных функций и их умножения с вектором отсчетов сигнала, например, при анализе спектров и фильтрации в задачах идентификации и диагностики в радиофизике, океанологии.

Целью изобретения является повышение быстродействия.

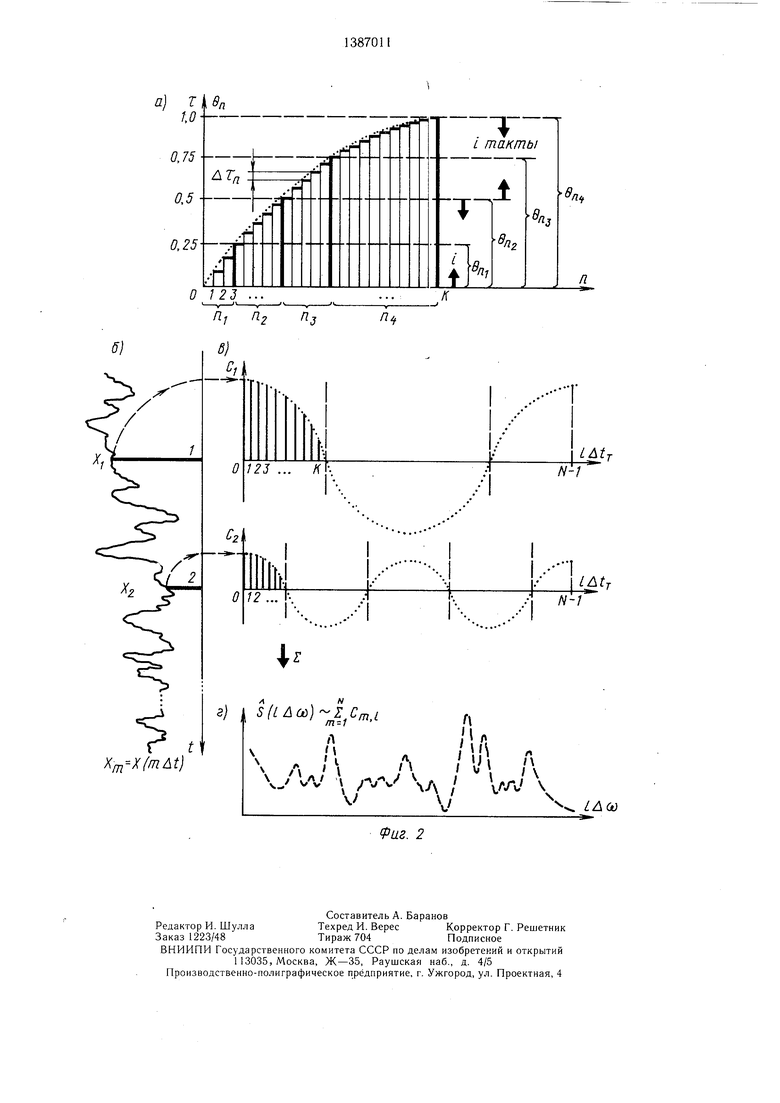

а синхроимпульсом на управляющем входе преобразователя 1 код-частота разрешается начало поступления на его выход потока импульсов частоты Fm, пропорциональной амплитуде входного отсчета Х Одновременно на вход устройства начинают поступать тактовые импульсы, осуществляющие сдвиг импульса с первого в последующие разряды регистра 6 сдвига. Поступая на выход одной из групп выхоИа фиг. 1 представлена функциональная Ш дов пь П2 Пз или П4 регистра 6 сдвига, схема предлагаемого арифметического уст- единичное состояние соответствующего раз- ройства; на фиг. 2а - иллюстрация вы числения произведений отсчета Х-сигнала на

четверть периода синусной функции, выпрлряда передается через соответствующий элемент ИЛИ 8-11 на второй вход одного из блоков элементов И 17-20, разрещая няемь1х одновременно на четырех участках j, считывание на определенный информацион- функции; на фиг. 26-г - временные диа- ный выход такого значения кода, которое к граммы реализации алгоритма анализа -через синтез ряда Фурье.

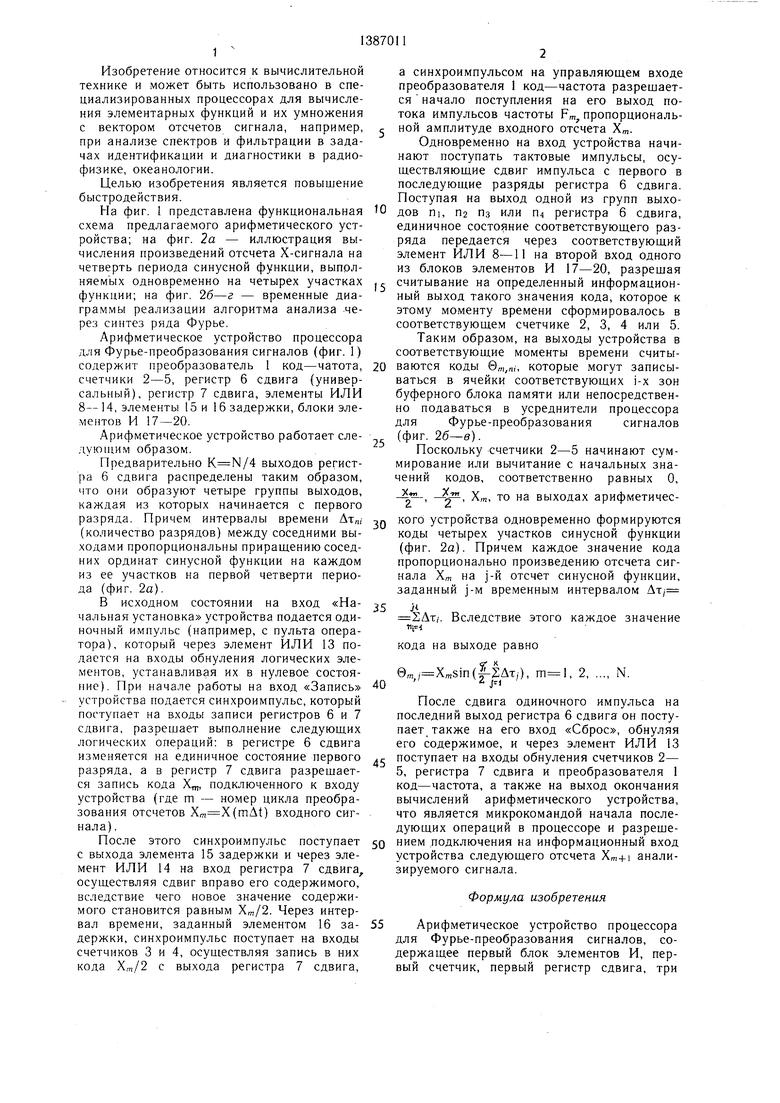

Арифметическое устройство процессора для Фурье-преобразования сигналов (фиг. 1)

содержит преобразователь 1 код-чатота, 20 ваются коды вт,., которые могут записы- счетчики 2-5, регистр б сдвига (универ- ваться в ячейки соответствующих i-x зон сальный), регистр 7 сдвига, элементы ИЛИ 8-14, элементы 15 и 16 задержки, блоки элементов И 17-20.

Арифметическое устройство работает сле- дуюпшм образом.

Предварительно выходов регистэтому моменту времени сформировалось в

соответствующем счетчике 2, 3, 4 или 5.

Таким образом, на выходы устройства в

соответствующие моменты времени считы25

ра 6 сдвига распределены таким образом, что они образуют четыре группы выходов, каждая из которых начинается с первого

буферного блока памяти или непосредственно подаваться в усреднители процессора для Фурье-преобразования сигналов (фиг, 26-а).

Поскольку счетчики 2-5 начинают суммирование или вычитание с начальных значений кодов, соответственно равных О,

, -, Хт, то на выходах арифметичес(количество разрядов) между соседними выходами пропорциональны приращению соседних ординат синусной функции на каждом из ее участков на первой четверти периода (фиг. 2а).

разряда. Причем интервалы времени Дтш -DQ устройства одновременно формируются ..коды четырех участков синусной функции

(фиг. 2а). Причем каждое значение кода пропорционально произведению отсчета сигнала Хт на j-й отсчет синусной функции, заданный j-м временным интервалом Дт/ В исходном состоянии на вход «На-

чальная установка устройства подается оди- 2Лт,-. Вследствие этого каждое значение

ночный импульс (например, с пульта оператора), который через элемент ИЛИ 13 подастся на входы обнуления логических элементов, устанавливая их в нулевое состоя- рше). При начале работы на вход «Запись 40 устройства подается синхроимпульс, который поступает на входы записи регистров 6 и 7

tip-i

кода на выходе равно 5f

в

,„,,Х„51п(|-|Дт/), , 2, ..., N.

После сдвига одиночного импульса на последний выход регистра б сдвига он поступает также на его вход «Сброс, обнуляя его содержимое, и через элемент ИЛИ 13

сдвига, разрешает выполнение следующих логических операций: в регистре б сдвига

После сдвига одиночного импульса на последний выход регистра б сдвига он поступает также на его вход «Сброс, обнуляя его содержимое, и через элемент ИЛИ 13

изменяется на единичное состояние первого . поступает на входы обнуления счетчиков 2- разряда, а в регистр 7 сдвига разрещает-,--.,,.

ся запись кода Х, подключенного к входу устройства (где m - номер цикла преобразования отсчетов (тД1) входного сигнала) .

После этого синхроимпульс поступает 50 нием подключения на информационный вход с выхода элемента 15 задержки и через эле-устройства следующего отсчета Xm-i-i аналимент ИЛИ 14 на вход регистра 7 сдвига, осуществляя сдвиг вправо его содержимого, вследствие чего новое значение содержимого становится равным Хт/2. Через интервал времени, заданный элементом 16 за- 55 держки, синхроимпульс поступает на входы

5, регистра 7 сдвига и преобразователя 1 код-частота, а также на выход окончания вычислений арифметического устройства, что является микрокомандой начала последующих операций в процессоре и разрещезируемого сигнала.

Формула изобретения

счетчиков 3 и 4, осуществляя запись в них кода Х„,/2 с выхода регистра 7 сдвига.

Арифметическое устройство процессора для Фурье-преобразования сигналов, содержащее первый блок элементов И, первый счетчик, первый регистр сдвига, три

а синхроимпульсом на управляющем входе преобразователя 1 код-частота разрешается начало поступления на его выход потока импульсов частоты Fm, пропорциональной амплитуде входного отсчета Х Одновременно на вход устройства начинают поступать тактовые импульсы, осуществляющие сдвиг импульса с первого в последующие разряды регистра 6 сдвига. Поступая на выход одной из групп выходов пь П2 Пз или П4 регистра 6 сдвига, единичное состояние соответствующего раз-

ряда передается через соответствующий элемент ИЛИ 8-11 на второй вход одного из блоков элементов И 17-20, разрещая считывание на определенный информацион- ный выход такого значения кода, которое к

ваются коды вт,., которые могут записы- ваться в ячейки соответствующих i-x зон

этому моменту времени сформировалось в

соответствующем счетчике 2, 3, 4 или 5.

Таким образом, на выходы устройства в

соответствующие моменты времени считываются коды вт,., которые могут записы- ваться в ячейки соответствующих i-x зон

буферного блока памяти или непосредственно подаваться в усреднители процессора для Фурье-преобразования сигналов (фиг, 26-а).

Поскольку счетчики 2-5 начинают суммирование или вычитание с начальных значений кодов, соответственно равных О,

, -, Хт, то на выходах арифметичес2Л

tip-i

кода на выходе равно 5f

в

,„,,Х„51п(|-|Дт/), , 2, ..., N.

После сдвига одиночного импульса на последний выход регистра б сдвига он поступает также на его вход «Сброс, обнуляя его содержимое, и через элемент ИЛИ 13

поступает на входы обнуления счетчиков 2- ,--.,,.

нием подключения на информационный вход устройства следующего отсчета Xm-i-i анали5, регистра 7 сдвига и преобразователя 1 код-частота, а также на выход окончания вычислений арифметического устройства, что является микрокомандой начала последующих операций в процессоре и разрещезируемого сигнала.

Формула изобретения

Арифметическое устройство процессора для Фурье-преобразования сигналов, содержащее первый блок элементов И, первый счетчик, первый регистр сдвига, три

элемента ИЛИ и преобразователь код-частота, выход которого подключен к счетному входу первого счетчика, информационный выход которого подключен к первому входу первого блока элементов И, выход ко- торого является первым информационным выходом устройства, информационным входом которого является информационный вход преобразователя код-частота, выход старшего разряда первого регистра сдвига является выходом окончания вычислений устройства и 0 подключен к входу обнуления первого регистра сдвига и первому входу первого элемента ИЛИ, второй вход которого является входом начальной установки устройства, входом синхронизации записи ко- 5 торого являются соединенные между собой первые входы второго и третьего элементов ИЛИ и вход разрешения записи первого регистра сдвига, тактовый вход которого подключен к выходу второго элемента

ответственно вторым и третьим информационными выходами устройства, четверт1 м информационным выходом которого является выход четвертого блока элементов И, пор вый вход которого подключен к информационному выходу четвертого счетчика, ипфор мационный вход которого подключен к информационному входу устройства, вход (ui i решения записи второго регистра сдвиг; . соединен с входом первого элемент; .; держки, входом разрешения запис и четио Ч(1- го счетчика и подключен к входу синхронизации записи устройства, Bhixdji шч/иого элемента задержки подк/тЮчеи к нходу шоро- го элемента задержки и второму H.(Xi третьего элемента ИЛИ, вычол кчюро; о подключен к тактовому вхолх птс.ркг- рр гистра сдвига, вход обнуления KOixiiVjiD n-jc динен с входами обнуления норного, игоро ч. третьего и четвертог о счетч1;кои npt oojia: .) вателя код-частота и подк/гючс и к iu.ixo iv

ИЛИ, второй вход которого является такто- 20 первого элемента ИЛИ, пыхол

вым входом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены второй, третий- и четвертый блоки элементов И, второй, треэлемента задержки подк,пючен к пхолам рмч-- решения записи второго и третьсч о г н тчи- ков и преобразвателя код-частота, иыхол которого подключен к счетным входам второтий и четвертый счетчики, четвертый, пя- с го, третьего и четвертого счетчиков, вторые

тый, шестой и седьмой элементы ИЛИ, первый и второй элементы задержки, второй регистр сдвига, выход которого подключен к информационным входам второго и третьего счетчиков, информационные выходы которых подключены к первым входам соответственно второго и третьего блоков элементов И, выходы которых являются совходы первого, второго, третьего и четвертого блоков элементов И подключены к выходам соответственно четвертого, пятого, шестого и седьмого элементов ИЛИ, первые, вторые и третьи входы которых под- 30 ключены к выходам соответствуюших разрядов соответственно первой, второй и третьей групп первого регистра сдвига.

ответственно вторым и третьим информационными выходами устройства, четверт1 м информационным выходом которого является выход четвертого блока элементов И, пор вый вход которого подключен к информационному выходу четвертого счетчика, ипфор мационный вход которого подключен к информационному входу устройства, вход (ui i решения записи второго регистра сдвиг; . соединен с входом первого элемент; .; держки, входом разрешения запис и четио Ч(1- го счетчика и подключен к входу синхронизации записи устройства, Bhixdji шч/иого элемента задержки подк/тЮчеи к нходу шоро- го элемента задержки и второму H.(Xi третьего элемента ИЛИ, вычол кчюро; о подключен к тактовому вхолх птс.ркг- рр гистра сдвига, вход обнуления KOixiiVjiD n-jc динен с входами обнуления норного, игоро ч. третьего и четвертог о счетч1;кои npt oojia: .) вателя код-частота и подк/гючс и к iu.ixo iv

элемента задержки подк,пючен к пхолам рмч-- решения записи второго и третьсч о г н тчи- ков и преобразвателя код-частота, иыхол которого подключен к счетным входам второвходы первого, второго, третьего и четвертого блоков элементов И подключены к выходам соответственно четвертого, пятого, шестого и седьмого элементов ИЛИ, первые, вторые и третьи входы которых под- 30 ключены к выходам соответствуюших разрядов соответственно первой, второй и третьей групп первого регистра сдвига.

В)

/j

С2

2)

Xfrj-X/ mAt)

Ф

S(LAOu),L

L lSi),Lf

Л/и .

/W,wV/ j

V MU;

LAt.

N4

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра Фурье | 1987 |

|

SU1387010A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Устройство для преобразования Хо изображения | 1990 |

|

SU1785004A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Цифровой измеритель длительности одиночных импульсов | 1984 |

|

SU1257600A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1991 |

|

RU2051413C1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1273944A1 |

| Функциональный преобразователь | 1986 |

|

SU1352476A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных процессорах для вычисления элементарных функций и их умножения с вектором отсчетов сигнала, например, при анализе спектров и фильтрации в задачах идентификации и диагностики в радиофизике, океанологии. Цель изобретения - повышение быстродействия. Поставленная цель достигается за счет то- го, что в состав устройства входят преобразователь 1 код-частота, счетчики 2-5, регистры 6, 7 сдвига, элементы ИЛИ 8-14, элементы 15, 16 задержки, блоки элементов И 17-20. 2 ил. (Л

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1983 |

|

SU1120347A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-07—Публикация

1986-10-20—Подача