А ясо 00

00 со 00 4

Изобретение относится к вычисли тельной и электроизмерительной техни ке и может быть использовано в каче- стве самостоятельного модуля или сос- тавной части различных устройств, в которых осуществляется преобразовав кие аналоговых сигналов в цифровые коды.

842

образователя Г/ в i-м такте. На вы ходе аналогового сумматора 2 образует- ся напряжение U-. + U;, а на

2; Cl 1

выходе аналогового сумматора 3 - напряжение и,; Ug| + 1,5U;. Эти на- пряже1шя подаются на соответствующие входы блоков 4, 5, 6 сравнения, на первые входы которых поступает вход

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1991 |

|

SU1797158A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297224A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1251326A1 |

| Устройство для определения текущей оценки среднего значения | 1984 |

|

SU1363251A1 |

| Анализатор спектра | 1977 |

|

SU732759A1 |

| Устройство контроля цифро-аналогового преобразователя | 1978 |

|

SU777816A1 |

| Функциональный преобразователь | 1977 |

|

SU744639A1 |

| АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2121712C1 |

Изобретение относится к вычислительной и электроизмерительной технике. Цель изобретения - повьшение точности и надежности. Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий тактовый генератор 8, первый, второй и третий блоки 4, 5, 6 сравнения, первый и второй аналоговые сумматоры 1, 2, первый цифроаналоговый преобразователь 16, регистр 15, распределитель 13 тактовых импульсов, дешифратор 7, введены второй цифроаналоговый преобразователь 17 и третий аналоговый сумматор 6, первый и второй элементы ИЛИ 9 и 10, элемент ШШ-НЕ 11, - элемент И 12 и счетчик 14 импульсов, благодаря которым контролируется работоспособность основных узлов устройства, а также уменьшается погрешность, обусловленная переходными процессами в разрядных ключах цифро- аналогового преобразователя. 1 ил., 1 табл. С S (Л

Целью изобретения является повыше- 10 ое напряжение U. По спаду первого

кие точности и надежности.

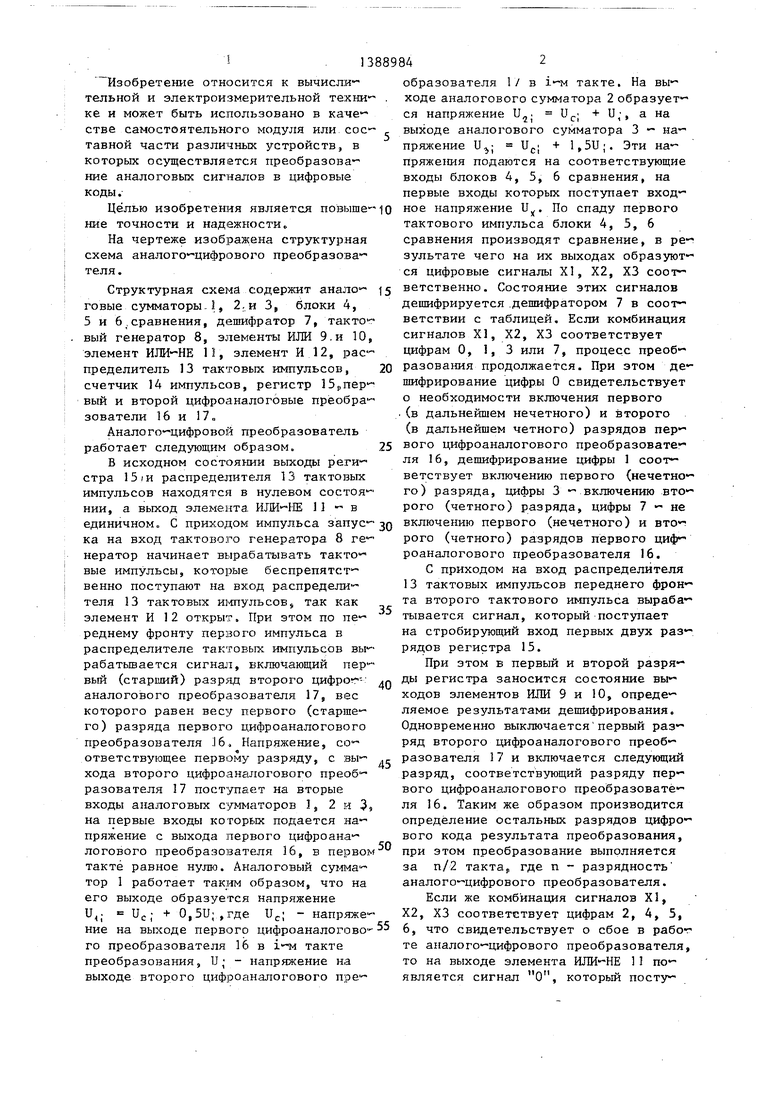

На чертеже изображена структурная схема аналого-цифрового преобразователя .

Структурная схема содержит анало- 15 го вые сумматоры-1, 2,. и 3, блоки 4, 5 и 6,сравнения, дешифратор 7, тактовый генератор 8, элементы ИЛИ 9.и 10, элемент ИЛИ-НЕ 11, элемент И 12, рас- пределитель 13 тактовых импульсов, 20 счетчик 14 импульсов, регистр 15„пер- вый и второй цифроаналоговые преобразователи 16 и 17 „

Аналого-цифровой преобразователь работает следующим образом. 25

В исходном состоянии выходы регистра 15/и распределителя 13 тактовых импульсов находятся в нулевом состоянии, а выход элемента ИЛИ-НЕ 11 - в

тактового импульса блоки 4, 5, 6 сравнения производят сравнение, в результате чего на их выходах образуются цифровые сигналы XI, Х2, ХЗ соответственно. Состояние этих сигналов дешифрируется .дешифратором 7 в соответствии с таблицей. Если комбинация сигналов X, Х2, ХЗ соответствует цифрам О, 1, 3 или 7, процесс преоб- разовагшя продолжается. При этом де- шифрирование цифры О свидетельствует о необходимости включения первого . (в дальнейшем нечетного) и второго (в дальнейшем четного) разрядов первого цифроаналогового преобразователя 16, дешифрирование цифры 1 соответствует включению первого (нечетного) разряда, цифры 3 - включению второго (четного) разряда, цифры 7 - не

единичном. С приходом импульса запус-зо включению первого (нечетного) и втока на вход тактового генератора 8 нератор начинает вырабатывать тактовые импульсы, которые беспрепятственно поступают на вход распределителя 13 тактовых игтульсов, так как элемент И 12 открыт. При этом по переднему фронту первого импульса в распределителе тактовых импульсов вы- рабатьшается сигнал, включающий пер- вый (старший) разред второго цифрог- аналогового преобразователя 17, нес которого равен весу первого (старшего) разряда первого цифроаналогового преобразователя 6. Напряжение, соответствующее первому разряду, с выхода второго цифроаналогового преобразователя 17 поступает на вторые входы аналоговых сумматоров 1, 2 и 3ii на первые входы которых подается напряжение с выхода первого цифроаналогового преобразователя 16, в первом такте равное нулю. Аналоговый cyiiMa- тор 1 работает таким образом, что на его выходе образуется напряжение Up; + 0,5и;,где Uj.; - напряже

35

40

45

50

рого (четного) разрядов первого циф- роаналогового преобразователя 16.

С приходом на вход распределителя 13 тактовых импульсов переднего фронта второго тактового импульса вырабатывается сигнал, который поступает на стробирующий вход первых двух разрядов регистра 15.

При этом в первый и второй разряды регистра заносится состояние выходов элементов ИЛИ 9 и 10, определяемое результатами дешифрирования. Одновременно выключается первый разряд второго цифроаналогового преобразователя 17 и включается следующий разряд, соответствующий разряду первого цифроаналогового преобразователя 16. Таким же образом производится определение остальных разрядов цифрового кода результата преобразования, при этом преобразование выполняется за п/2 такта где п - разрядность аналого-цифрового преобразователя.

Если же комбинация сигналов XI, Х2, ХЗ соответствует цифрам 2, 4, 5,

ние на выходе первого цифроаналогово-55 6, что свидетельствует о сбое в рабого преобразователя 16 в i-м такте преобразования, U , - напряжение на выходе второго цифроаналогового пре

ое напряжение U. По спаду первого

тактового импульса блоки 4, 5, 6 сравнения производят сравнение, в результате чего на их выходах образуются цифровые сигналы XI, Х2, ХЗ соответственно. Состояние этих сигналов дешифрируется .дешифратором 7 в соответствии с таблицей. Если комбинация сигналов X, Х2, ХЗ соответствует цифрам О, 1, 3 или 7, процесс преоб- разовагшя продолжается. При этом де- шифрирование цифры О свидетельствует о необходимости включения первого . (в дальнейшем нечетного) и второго (в дальнейшем четного) разрядов первого цифроаналогового преобразователя 16, дешифрирование цифры 1 соответствует включению первого (нечетного) разряда, цифры 3 - включению второго (четного) разряда, цифры 7 - не

включению первого (нечетного) и вто

рого (четного) разрядов первого циф- роаналогового преобразователя 16.

С приходом на вход распределителя 13 тактовых импульсов переднего фронта второго тактового импульса вырабатывается сигнал, который поступает на стробирующий вход первых двух разрядов регистра 15.

При этом в первый и второй разряды регистра заносится состояние выходов элементов ИЛИ 9 и 10, определяемое результатами дешифрирования. Одновременно выключается первый разряд второго цифроаналогового преобразователя 17 и включается следующий разряд, соответствующий разряду первого цифроаналогового преобразователя 16. Таким же образом производится определение остальных разрядов цифрового кода результата преобразования, при этом преобразование выполняется за п/2 такта где п - разрядность аналого-цифрового преобразователя.

Если же комбинация сигналов XI, Х2, ХЗ соответствует цифрам 2, 4, 5,

6, что свидетельствует о сбое в работе аналого-цифрового преобразователя, то на выходе элемента ИЛИ-НЕ 1I появляется сигнал О, который поступает на вход элемента И 12, блокируя тем самым прохождение тактовых им пульсов на вход распределителя 13 тактовых импульсов и установочный вход счетчика 14 импульсов. При этом счетчик 14 импульсов уже не сбрасывается с приходом каждого следующего тактового импульса, а начинает накап ливать число тактовых импульсов, по- ступающих в сбойной ситуации на стробирующие -входы блоков 4, 5 и 6 сравнения. Если сбой устранился на выходе блоков 4, 5 и 6 сравнения, запрещенных состояний не образуется, на выходе элемента ИЛИ-НЕ 11 вырабатывается зфовень 1, деблокирующий прохождение тактовых импульсов на вход распределителя 13 тактовых импульсов и на установочный вход счетчика 14 импульсов, тем самым обнуляя его. В противном случае, при превышении числа тактовых импульсов, подсчитанных счетчиком 14 импульсов, заданного числа на выходе счетчика вырабатыва- ется сигнал Авария и преобразование прекращается.

Предлагаемый аналого-цифровой преобразователь позволяет повысить точность преобразования за счет того, что поразрядное кодирование как тактовое осуществляется вторым цифроана- логовым преобразователем посредством включения и вык лючения за один такт соответствующих разрядов, причем . включение и выключение разрядов зависит от результатов сравнения преобразуемого напряжения с напряжением циф- роаналогового преобразователя. Первый же цифроаналоговый преобразователь используется для преобразования текущего цифрового кода в аналоговую форму, причем его разряды не переключаются, а либо включаются либо не включаются, что определяется результатом сравнения преобразуемого напряжения с напряжением цифроаналогового преобразователя. Тем самым устраняются погрешности, обусловленные переходными процессами при переключении разря- дов цифроаналогового преобразователя, особенно в критических точках диапазона преобразования.

Надежность функционирования предлагаемого преобразователя повышается за счет распознавания дешифратором запрещенных состояний на выходах блоков сравнения и блокировки процесса преобразования до устранения сбойной

ситуации. Известно, что при подаче на вторые входы блоков сравнения напряжений, равных

и,; и,; + 0,5KU;,

(1)

е и. - напряже1ше, подаваемое на вход К-го блока сравнения во время i-и иттерации; и - суммарное выходное напряжение первого цифроаналогово- го преобразователя во время i-и иттерации;

U; - выходное напряжение второго цифроаналогового преобразователя во время i-и ит- терации; К - номер блока сравнения, К

1, 2, 3;

i - номер иттерации, , 2, ... п/2 (п - число разрядов аналого-цифрового преобразователя),

при условии, что сигнал на выходе ока сравнения формируется в сооттствии с выражением

I, если и

О, если и,.

(2)

Uv

а суммарное выходное напряжение первого цифроаналогового преобразователя определяется, как

с; iL .t (3)

В-1

.

зо - .Q д ,

50

5

где ар, коэффициенты, характеризующие включение соответ-. нечетных и четных разрядов цифроаналогового преобразователя, 1 1,0, m 1,0;

и.,и - напряжение соответственно нечетных и четных разрядов первого цифроанало- i гового преобразователя; i - номер нечетного разряда,

i 21 - 1; га - номер четного разр5зда,

m 21,

комбинации состояний выходов блоков сравнения взаимно связаны со значениями преобразуемой величины, что классифицируется таблицей.

Таким образом, комбинации состояний выходов блоков сравнения, соответствующие десятичным цифрам 2, 4, 5, 6, свидетельствуют о сбое в работе цифроаналоговых преобразователей, аналоговых сумматоров или блоков

сравнения, так как не выполняется не- равенство

и.

- и...

2 I Ь

13889846

счетный вход объединен с третьими входами блоков сравнения, с первым входом элемента И и соединен с выходом тактового генератора, а установочный вход счетчика импульсов объе- динен с входом распределителя тактовых импульсов и подключен к выходу элемента И, второй вход которого сое- содержащий тактовый генератор, управ- Q динен с выходом элемента ИЛИ-НЕ, пер- л|яющий вход которого является шиной вый вход третьего аналогового сумма- Пуск, первый, второй и третий бло- тора объединен с первым входом второ- KiH сравнения, первые входы которых . го аналогового сумматора, а вторые объединены и являются входной шиной,, входы аналоговых сумматоров объеди-

15

Формула изобретения Аналого-цифровой преобразователь,,

в торые входы первого и второго бло

нены и подключены к выходу второго цифроаналогового преобразователя,входы которого подключены к соответст- вуюпщм выходам распределителя т акто- вых импульсов, выход третьего аналок|ов сравнения соединены с выходами

n l

нены и подключены к выходу второго цифроаналогового преобразователя,входы которого подключены к соответст- вуюпщм выходам распределителя т акто- вых импульсов, выход третьего аналоlepBoro и второго аналоговых суммато- р|ов соответственно, первые входы ко- объединены и подключены к вы-

х|оду первого цифроаналогового преоб- 20 гового сумматора соединен с вторым р|азователя, входы которого подключе- входом третьего блока сравнения, пер- н|ы к соответствующим выходам регист- вые входы элементов ИЛИ объединены и являются соответствующими выход- ь|ыми шинами, стробирукщие входы i-ro р|азряда, где i 1,3,5,. . . ,п-1 , и 25 вторым входом первого элемента ИЛИ, (li+l)-ro разряда регистра объединены третий выход -подключен к первому - 1 соединены с соответствующими выхода- Ми распределителя тактовых импульсов, ыходы блоков сравнения подключены к

и подключены к первому входу дешифратора, второй выход которого соединен

входу элемента ИЛИ-НЕ, четвертый вход соединен с вторым входом второго элемента ИЛИ, а пятый, шестой и седьмой

боответствующим входам дешифратора, о выходы соединешз соответственно с

отличающийся тем, что, с Целью повьшения точности и надежности, в него введены второй цифроана- J oгoвый преобразователь, третий ана- оговый сумматор, первый и второй Элементы ИЛИ, элемент ИЛИ-НЕ, элемент И и счетчик импульсов, выход ко-

вторым, третьим и чет элемента ИЛИ-НЕ, инфо ды нечетных разрядов нены и подключены к в элемента ИЛИ, а инфор четных разрядов регис и подключены к выходу та РШИ.

торого является шиной неисправности,,

Взаимосвязь состояний блоков сравнения и значений

входного напряжения

нены и подключены к выходу второго цифроаналогового преобразователя,входы которого подключены к соответст- вуюпщм выходам распределителя т акто- вых импульсов, выход третьего аналогового сумматора соединен с вторым входом третьего блока сравнения, пер- вые входы элементов ИЛИ объединены вторым входом первого элемента ИЛИ, третий выход -подключен к первому -

гового сумматора соединен с вторым входом третьего блока сравнения, пер- вые входы элементов ИЛИ объединены вторым входом первого элемента ИЛИ, третий выход -подключен к первому -

и подключены к первому входу дешифратора, второй выход которого соединен

гового сумматора соединен с вторым входом третьего блока сравнения, пер- вые входы элементов ИЛИ объединены вторым входом первого элемента ИЛИ, третий выход -подключен к первому -

входу элемента ИЛИ-НЕ, четвертый вход соединен с вторым входом второго элемента ИЛИ, а пятый, шестой и седьмой

вторым, третьим и четвертым входами элемента ИЛИ-НЕ, информационные,входы нечетных разрядов регистра объединены и подключены к выходу первого элемента ИЛИ, а информационные входы четных разрядов регистра объединены и подключены к выходу второго элемента РШИ.

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1977 |

|

SU705670A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 762166, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-04-15—Публикация

1986-11-18—Подача