(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С КОРРЕКЦИЕЙ ДИНАМИЧЕСКИХ ПОГРЕШНОСТЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в код | 1980 |

|

SU884126A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1972 |

|

SU439913A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1018227A1 |

| Преобразователь напряжения в десятичный код | 1982 |

|

SU1072260A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Аналого-цифровой преобразовательпОРАзРядНОгО уРАВНОВЕшиВАНия | 1979 |

|

SU818003A1 |

| Г. Г. ЖИВИЛОБ; ::-.:;B::^ji03MAfl'1!^'а:гни кя,;^^'^?-кАЯ'Ч.'г. | 1972 |

|

SU324705A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU843216A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU660240A1 |

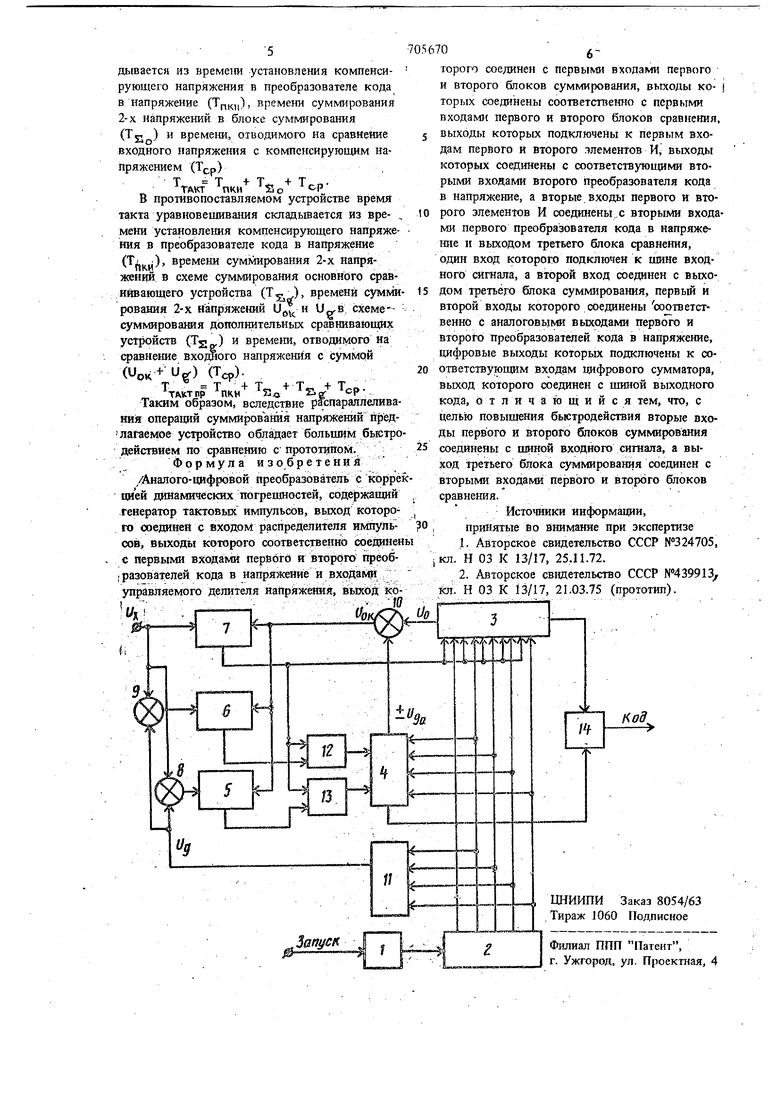

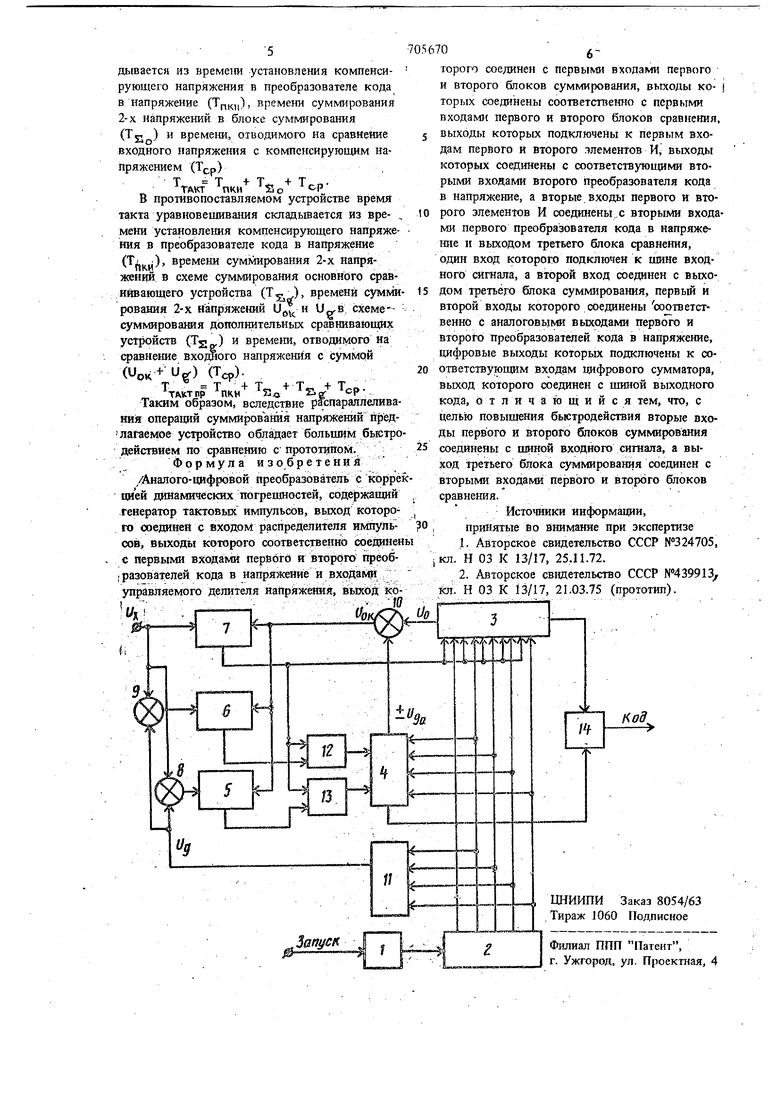

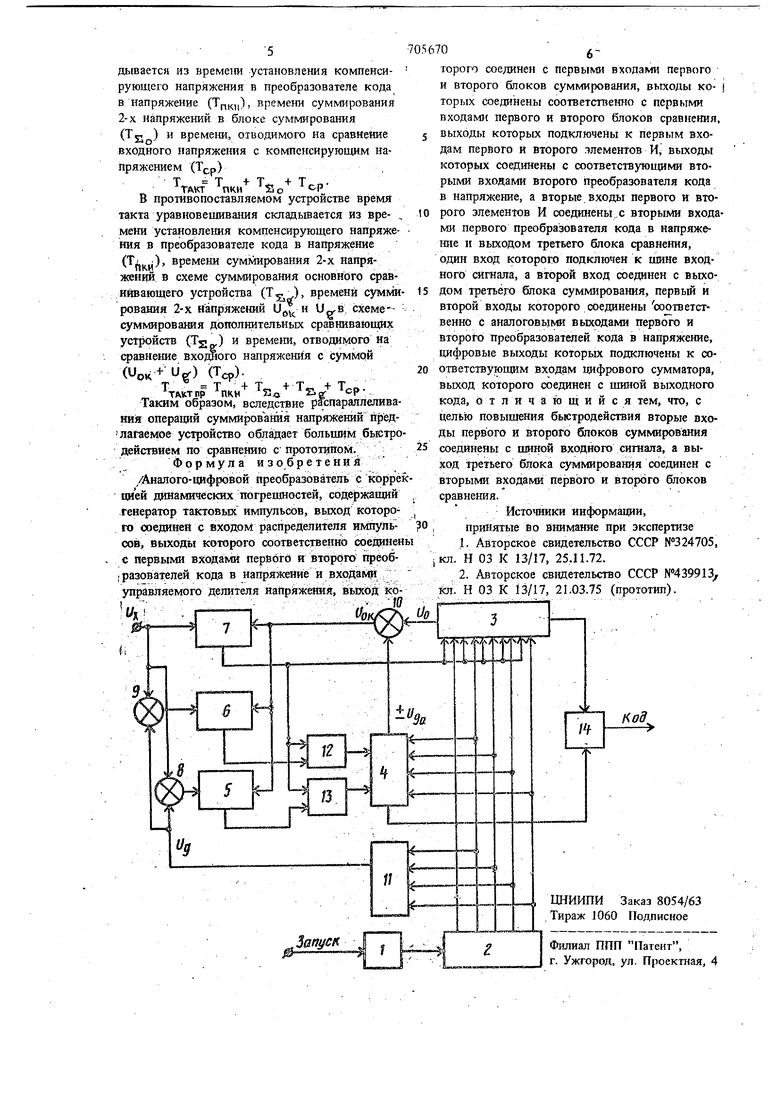

Изобретение касается измерительной и вычислительной техники и может быть использовано для преобразования быстроизменяющихся во времени сигналов в цифровой код. Известен аналого-цифровой преобра:зователь, содержащий сравнивающее устройство, блок суммирования, преобразователь кода в напряже ние, регистр триггеров, элементы И, тактовый генератор и распределитель тактовых импульсов 1. Однако в известном устройстве время суммирования компенсациошюго напряжения и напряжения управляемого делителя входит в такт уравн6вешива1шя, в результате чего увеличивается время преобразования. Наиболее близким по технической сущности к предлагаемому устройству является преобразователь, содержащий генератор тактовых импульсов, управляющий распределителем импуль сов, выход последнего присоединен к входам основного и дополнительного преобразователей кода в напряжение и входу управляемого делителя напряжения, основного и двух дополнительных сравнивающих устройств с блоками суммирования на одном из входов, двух элементов И и цифрового сумматора, причем входы блоков суммирования основного сравнивающего устройства присоединены к аналоговым вькодам основного и дополнительного преобразователей кода в напряжение, цифровые Выходы которых соединены с входом цифрового сумматора, а выход основного сравнивающего устройства присоединен к входам основного преобразователя кода в напряжение и к Первым входам элементов И, вторые входы которых присоединены к выходам дополнительных сравнивающих устройств, а . ыходы элементов И присоединены ко входу дополнительного преобразователя кода в напряжение, выход управляемого делителя напряжения присоединен к первым входам блоков сумми- i рования дополнительных срав1швающих устройств вторые входы которь1х соёДинень: с выходом блока суммировагая основного сравнивающего устройства, а вторые входы дополнительных сравнивающих устройств присоединены к входной клемме преобразователя 2}. Даиньш преобразователь обладает относительно низким быстродействием из-за значительного плияиия на время такта преобразования промеш операции cyMrviiipoBiiiin; Kor.r.icnсациогетого налряжешш с напряжением jTipasляемого делителя. Цель изобретения - повышение быстродейIствия преобразователя. Для этого в аналого-цифровом преобразивателе с коррекцией динамических norpeiimocтей, содержащем генератор тактовых импульсов, выход которого соединен с входом распределителя импульсов, выходы которого соответственно соединены с первыми входами первого ивторого преобразователей кода в напря жение и входами ртравляемого делителя напряжения, выход которого соединен с первыми входами первого и второго блоков суммирова ния, выходы которых соединены соответственно с первыми входами первого и второго блокбв срайненйя, выходы которых подключены к первым входам первого и второго элементов И, вькоды которых соединены с соответствуюпдами втЬрыми входами второго преобра - зователя кода в напряжение, а вторые входы первого и второго элементов И соединены с вторыми входами первого преобразователя кода в напряжение и выходом третьего блока сравнения, один вход которого подключен к шине второго сигнала, а второй вход соединен с выходом третьего блока суммирования, первый и второй входы которого соединены соответственно с аналоговыми, вьЬсодами перво . г о и второго преобразователей кода в напряже ние, цифровые выходь которых подключены к соответствуюцдам входам цифрового сумматора, выход которого соединен с шиной выхо ногб кода, вторые входы первого и второго блоков суммирования соединены с шиной входного сигнала, а выход третьего блока сум мирования соединен с вторыми в содами перво го и второго блоков сравнения. На чертеже приведена структурная электрическая схема предложе1шого устройства. Преобразователь содержит генератор 1, .тактовых импульсов, управляющий распределителем 2 импульсов, который подсоединен к входам первого и второго преобразователей 3 и 4 кода в .напряжение, блокй ср авнения 5, б и 7 с блоками суммирования 8, 9 и 10 соответственно на одном из входов, управлявмьш делитель напряжения 11, два элемента И 12, 13 и цифровой сумматор 14, причём входы блока суммирования 10 присоединены соответственно к аналоговым выходам преобразователей 3, 4, цифррвьге вь1хОды которых соединены с вхоДом цифрового сумматора 14 а выход блока 7 сравнения присоединен к 7 .4 вторым входам преобразо}зателя 3 и к вторым входам элементов И 12, 13, первые входы которых присоедитгеньт соответстпеино к выходам блоков б, 5 сравнения, а 81)1хо/г,ы элемептои И 12, 13 присоединены ко входам преобразователя 4, выход управляемого делителя напряжения 8 присоединен к первым.входам блоков 8, 9 суммирования, вторые входы которых соединены с шиной входного сигнала, а выход блока 10 суммирования подключен к вторым входам блоков 5, 6 сравнения.. ГТредлагаемьш преобразователь,осуществляет преобразование входных изменяюпдахся сигналов в двоичньш код. Преобразуемый сигаал подается на входы блока 7 сравнения и двух блоков суммирования 8 и 9. По сигналу запуска с генерат ора I тактовых импульсов начинают поступать импульсы на распределитель 2 тактовых импульсов, с шин которого управляющие ситалы последовательно поступают на входы преобразователей 3 и 4 кода в напряжение и управляемого делителя наиряжетшя 11. Происходит процесс анаЛого-Щ1фрового поразрядного уравновешивания измеряемого напряже1шя компенсирующим напряжением . равным сумме . выходных напряжений U и ид„ и преобразователей 3 и 4 у которое образуется на выходе блока 10 суммирования. При этом компенсирующее напрялсение 0 поступает одновременно и на входыблоков сравнения 5 и 6, причем в блоке 6 сравнения происходит сравнение этого иапряже1шя с суммой преобразуемого сигнала напряжения U, вырабатываемого управляемым делителем напряжеьшя 11 на каждом такте, равным весу данного разряда на данном такте уравновешивания (и + и«), а в блоке 5 сравне1Шя - сравнение этого напряжения с разностью Uv- и Up .. .. -, (и - DO). Сумма и разность образуются соответстве1шо на блоках сзммироваиия 9, 10. Если процесс уравновешиватшя идет прав1шьно, то всегда выполняются условия: Ug и и,- и и в случае, если эти условия нарушаются, то проргсходит коррекщ{я U, т. ё. преобразователькода в напряжегше 4 вырабат1зшает отрицательное напряжение (-U.) при срабатывании блока 6 сравнения/и положительное напряжение (+UAJ,) при срабатывании блока 5 сравнения, который срабатьшает при U);- (J UOK Т. е. при нарушении второго условия. Таким образом, возможна коррекция погрешности на каждом такте уравновешивания. Feзультитующий код формируется в цифровом сумматоре 14 в конце цикла преобразования. Такт уравновешивания преобразователя скла

Авторы

Даты

1979-12-25—Публикация

1977-04-25—Подача