Изобретение относится к вычислительной технике и предназначено для использования в полупроводниковых интегральных схемах с внутренним источником высокого напряжения в качестве статически непотребляющей мощность нагрузки высоковольтной схемы дешифрации.

Цель изобретения - расширение области применения устройства и повышение быстродействия.

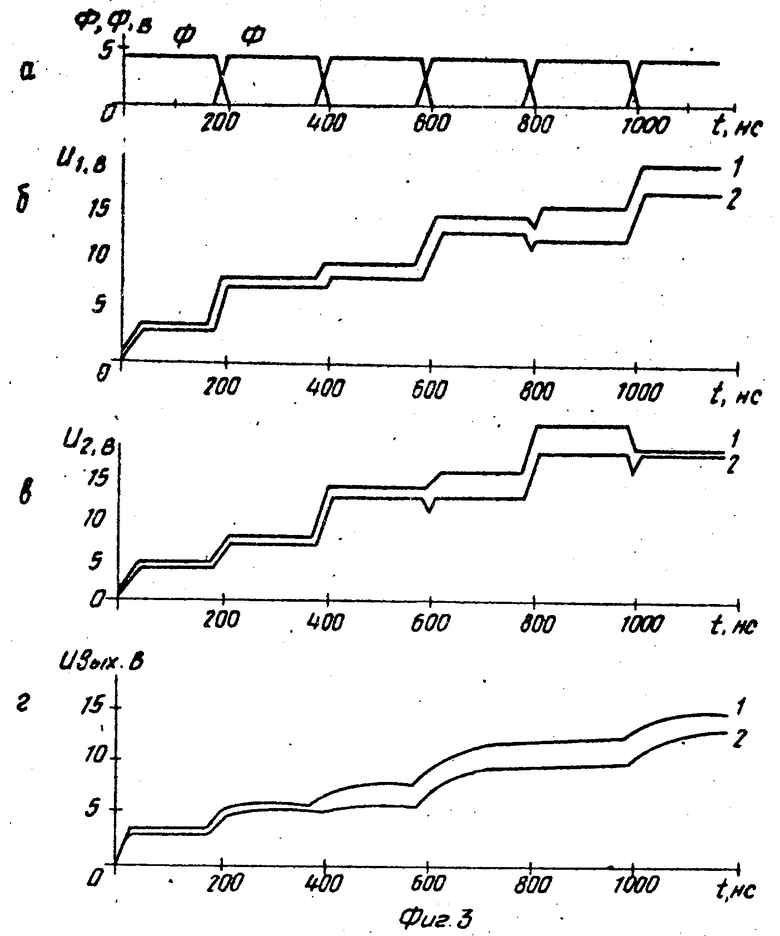

На фиг. 1 показана принципиальная электрическая схема устройства передачи высокого напряжения; на фиг. 2 - то же, вариант исполнения; на фиг. 3 показаны временные диаграммы напряжений устройства при включении: а) напряжения тактового сигнала (Ф) и инверсного тактового сигнала (Ф); б) напряжения на второй обкладке первого конденсатора; в) напряжения на второй обкладке второго конденсатора; г) выходного напряжения Uпор(0) = 0,2 В, η = 0,5 В1/2 (1); Uпор (0) = 0,5 В; η = 0,7 В1/2 (2); на фиг. 4 - временная диаграмма выходного напряжения устройства при включении Uпор (0) = 0,2 В; η = 0,5 В1/2 (1); Uпор (0) = 0,5 В, η = 0,7 В1/2 (2).

Устройство содержит конденсаторы 1 и 2, транзисторы 3-7, шину 8 высокого напряжения, выходную шину 9, шину 10 тактового сигнала, шину 11 инверсного тактового сигнала, шину 12 низковольтного сигнала, причем первая обкладка конденсатора 1 соединена с шиной 10 тактового сигнала, вторая обкладка конденсатора 1 - с затворами транзисторов 5 и 6, истоками транзисторов 3 и 4, сток транзистора 5 соединен с шиной 8 высокого напряжения и стоками транзисторов 3 и 6, исток транзистора 5 - с выходной шиной 9 и стоками транзисторов 4 и 7. Затвор транзистора 4 соединен с шиной 12 низковольтного сигнала и затвором транзистора 7, первая обкладка конденсатора 2 соединена с шиной 11 инверсного тактового сигнала, а вторая обкладка конденсатора 2 - с затвором транзистора 3, истоками транзисторов 6 и 7. Таким образом, устройство передачи высокого напряжения является двухтактным.

Устройство начинает работать при подаче низковольтного сигнала (2,5-5 В) от схемы дешифрации на выходную шину 9. Это напряжение через транзисторы 4 и 7 передается на вторые обкладки конденсаторов 1 и 2, так как затворы транзисторов 4 и 7 подключены к шине низковольтного сигнала (4,5-5,5 В).

U11 = U21 = Uвых.1, (1) где U11 - напряжение на второй обкладке конденсатора 1;

U21 - напряжение на второй обкладке конденсатора 2;

Uвых.1 - напряжение на выходной шине 9.

При приходе положительного фронта тактового сигнала Ф на шину 10 и первую обкладку конденсатора 1 напряжение на второй обкладке конденсатора 1 увеличивается за счет "бутстрепного" эффекта на нем на величину амплитуды тактовых сигналов и становится равным

U12 = U11 + Uф, (2) где U12 - напряжение на второй обкладке конденсатора 1 после прихода положительного фронта тактового сигнала на шину 10.

Транзистор 4 закрывается при этом по истоку, исключая тем самым влияние выходной емкости Свых на работу схемы. Это напряжение подается на затворы транзисторов 5 и 6, обеспечивая тем самым заряд выходной шины 9 через транзистор 5 и второй обкладки конденсатора 2 через транзистор 6 до уровней

Uвых = U12 - Uпор.5 = U11 + Uф - Uпор.5. (3)

U22 = U12 - Uпор.6 = U11 + Uф - Uпор.6, (4)

где Uвых - напряжение на выходной шине 9 после прихода положительного фронта тактового сигнала на шину 10;

Uпор.5 - пороговое напряжение транзистора 5 с учетом коэффициента влияния подложки;

U22 - напряжение на второй обкладке конденсатора 2 после прихода положительного фронта тактового сигнала на шину 10;

Uпор.6 - пороговое напряжение транзистора 6 с учетом коэффициента влияния подложки.

Транзистор 7 закрывается при этом по истоку. Поскольку транзисторы 5 и 6 находятся в одинаковых условиях (их стоки и затворы соединены)

Uпор.5 = Uпор.6, (5)

Напряжение Uвых.2 на выходной шине становится

Uвых.2 = U11 + Uф - Uпор.6 , (6)

При приходе отрицательного фронта тактового сигнала Ф на шину 10 и первую обкладку конденсатора 1 напряжение на второй его обкладке стремится уменьшиться за счет "бутстрепного" эффекта на нем до напряжения, которое способен поддержать транзистор 3. Но в этот момент приходит положительный фронт инверсного тактового сигнала Ф на шину 11 и первую обкладку конденсатора 2. Напряжение U23 на второй обкладке конденсатора 2 увеличивается за счет "бутстрепного" эффекта на нем на величину амплитуды тактовых сигналов и становится

U23 = U22 + Uф = U11 + 2Uф - Uпор.6, (7) где U23 - напряжение на второй обкладке конденсатора 2 после прихода положительного фронта инверсного тактового сигнала на шину 11 и отрицательного фронта тактового сигнала на шину 10.

Это напряжение подается на затвор транзистора 3, и через него на второй обкладке конденсатора 1 поддерживается потенциал, равный

U13 = U23 - Uпор.3 = U12 + Uф - Uпор.3 - -Uпор.6 = U11 + 2Uф - Uпор.3 - Uпор.6, (8) где U13 - напряжение на второй обкладке конденсатора 1 после прихода отрицательного фронта тактового сигнала на шину 10;

Uпор.3 - пороговое напряжение транзистора 3 с учетом коэффициента влияния подложки.

Таким образом, несмотря на отрицательный фронт тактового сигнала на шине 10, напряжение на второй обкладке конденсатора 1 получает приращение по отношению к предыдущему состоянию

U13 - U12 = Uϕ -Uпор.3- Uпор.6, (9) вследствие роста напряжения на затворе транзистора 3 и второй обкладке конденсатора 2 за счет "бутстрепного" эффекта на нем, вызванное приходом положительного фронта инверсного тактового сигнала на шине 11.

Рассмотрим i-тый момент времени. Допустим, что напряжение на второй обкладке конденсатора 1 U1i. При приходе положительного фронта тактового сигнала на шину 10 и первую обкладку конденсатора 1 напряжение на второй обкладке конденсатора 1 увеличивается за счет "бутстрепного" эффекта на нем на величину амплитуды тактовых сигналов и становится

U1(i+1) = U1i + Uф, (10) где Uвых(i+1) - напряжение на второй обкладке конденсатора 1 после прихода положительного фронта тактового сигнала на шину 10.

Это напряжение подается на затворы транзисторов 5 и 6, обеспечивая тем самым заряд выходной шины 9 через транзистор 5 и второй обкладки конденсатора 2 через транзистор 6 до уровней

Uвых(i+1) = U1(i+1) - Uпор.5, (11)

U2(i+1) = U1(i+1) - Uпор.6, (12) где Uвых(i+1) - напряжение на выходной шине 9 после прихода положительного фронта тактового сигнала на шину 10;

U2(i+1) - напряжение на второй обкладке конденсатора 2 после прихода положительного фронта тактового сигнала на шину 10.

Поскольку транзисторы 5 и 6 находятся в одинаковых условиях (их стоки и затворы соединены), Uпор.5 = Uпор.6.

Из формулы (9) получаем

Uвых(i+1) = U1(i+1) - Uпор.6, (13)

При приходе отрицательного фронта тактового сигнала на шину 10 и первую обкладку конденсатора 1 напряжение на второй его обкладке стремится уменьшиться за счет "бутстрепного" эффекта на нем до напряжения, которое способен поддержать транзистор 3. Но в этот момент приходит положительный фронт инверсного тактового сигнала на шину 11.

Напряжение U2(i+2) на второй обкладке конденсатора 2 увеличивается за счет "бутстрепного" эффекта на нем на величину амплитуды тактовых сигналов и становится

U2(i+2) = U2(i+1) + Uф = U1(i+1) + Uф - Uпор.6 (14) где U2(i+2) - напряжение на второй обкладке конденсатора 2 после прихода положительного фронта инверсного тактового сигнала на шину 11 и отрицательного фронта тактового сигнала на шину 10.

Это напряжение подается на затвор транзистора 3, и через него на второй обкладке конденсатора 1 устанавливается и поддерживается потенциал

U1(i+2) = U2(i+2) - Uпор.3 = U1(i+1) +

+ Uф - Uпор.3 - Uпор.6, (15) где U1(i+2) - напряжение на второй обкладке конденсатора 1 после прихода отрицательного фронта прямого тактового сигнала на шину 10.

При приходе второго импульса тактового сигнала на шину 10 и первую обкладку конденсатора 1 напряжение U1(i+3) на второй обкладке конденсатора 1 увеличивается за счет "бутстрепного" эффекта на нем на величину амплитуды тактовых сигналов и становится

U1(i+3) = U1(i+2) + Uф = U1(i+1) + 2Uф -

- Uпор.3 - Uпор.6, (16) где U1(i+3) - напряжение на второй обкладке конденсатора 1 после прихода положительного фронта второго импульса тактового сигнала на шину 10. И с учетом формулы (13) получаем

U1(i+3) = Uвых(i+1) + 2Uф - Uпор.3. (17)

Это напряжение подается на затвор транзистора 5 и через него выходная шина 9 заряжается до уровня

Uвых(i+3) = U1(i+3) - Uпор.5 =

= Uвых(i+1) + 2Uф - Uпор.3 - Uпор.5, (18) где Uвых(i+3) - напряжение на выходной шине 9 после прихода положительного фронта импульса тактового сигнала на шину 10.

Таким образом, напряжение на выходной шине 9 за период увеличивается на величину Uвых(i+3) - Uвых(i+1) = 2Uф - Uпор.3 - Uпор.5 (19)

Условие работоспособности схемы. Чтобы напряжение на выходной шине 9 получило приращение, необходимо

2Uф - Uпор.3 - Uпор.5 > 0 (20) или

2Uф > Uпор.3 + Uпор.5.

Для работоспособности устройства необходимо, чтобы удвоенная величина амплитуды тактовых сигналов была больше суммы пороговых напряжений транзисторов 5 и 3.

Выключение устройства производится следующим образом. На выходную шину 9 подается напряжение ноль вольт. Это напряжение через транзисторы 4 и 7 поступает на затворы транзисторов 5, 3 и 6 и вторые обкладки конденсаторов 1 и 2. Транзисторы 5, 3 и 6 закрываются, а так как в данный момент времени напряжение между вторыми и первыми обкладками конденсаторов 1 и 2 становится меньше порогового напряжения, конденсаторы 1 и 2 перестают существовать как емкости. Схема перестает работать.

Принципиальная электрическая схема устройства изображенная на фиг.2, отличается от схемы устройства, изображенной на фиг.1, тем что в качестве низковольтного сигнала применены тактовый и инверсный тактовый сигналы, затвор транзистора 4 соединен с шиной тактового сигнала, а затвор транзистора 7 - с шиной инверсного тактового сигнала.

Принцип работы устройства, показанного на фиг.2, аналогичен работе устройства, показанного на фиг. 1, но в момент включения и выключения заряд и разряд вторых обкладок конденсаторов 1 и 2 и затворов транзисторов 5, 3 и 6 через транзисторы 4 и 7 соответственно происходит при приходе тактового и инверсного тактовых сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2542913C1 |

| Устройство для записи информации в блоки памяти с произвольной выборкой | 1984 |

|

SU1156136A1 |

| Формирователь импульсов | 1982 |

|

SU1091327A1 |

| БУФЕРНОЕ УСТРОЙСТВО | 1987 |

|

SU1507180A1 |

| Формирователь импульсов | 1985 |

|

SU1374416A1 |

| Формирователь импульсов | 1985 |

|

SU1374417A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2050600C1 |

Изобретение предназначено для использования в полупроводниковых интегральных схемах с внутренним источником высокого напряжения в качестве статически непотребляющей мощности нагрузки высоковольтной схемы дешифрации. Устройство передачи высокого напряжения содержит конденсаторы 1 и 2, транзисторы 3 - 7, шину 8 высокого напряжения, выходную шину 9, шину 10 тактового сигнала, шину 11 инверсного тактового сигнала, шину 12 низковольтного сигнала. Устройство имеет расширенную область применения и повышенное быстродействие. 4 ил.

УСТРОЙСТВО ПЕРЕДАЧИ ВЫСОКОГО НАПРЯЖЕНИЯ, содержащее первый конденсатор, первый, второй, третий транзисторы, шину высокого напряжения, выходную шину, шину тактового сигнала, первый вывод первого конденсатора соединен с шиной тактового сигнала, второй вывод первого конденсатора - с затвором первого транзистора, истоками второго и третьего транзисторов, сток первого транзистора соединен с шиной высокого напряжения и стоком второго транзистора, исток первого транзистора - с выходной шиной и стоком третьего транзистора, отличающееся тем, что, с целью расширения области применения устройства и повышения быстродействия, дополнительно введен второй конденсатор, четвертый и пятый транзисторы, шина инверсного тактового сигнала и шина низковольтного сигнала, причем затвор третьего транзистора соединен с затвором пятого транзистора и шиной низковольтного сигнала, первый вывод второго конденсатора соединен с шиной инверсного тактового сигнала, второй вывод второго конденсатора - с затвором второго транзистора и истоками четвертого и пятого транзисторов, сток четвертого транзистора соединен с шиной высокого напряжения, а затвор четвертого транзистора - с затвором первого транзистора, сток пятого транзистора соединен с выходной шиной.

| Electronic Design, August 18, 1983, p.189-196. |

Авторы

Даты

1994-12-30—Публикация

1986-10-29—Подача