Изобретение относится к вычислительной технике и предназначено для использования в полупроводниковых интегральных схемах в качестве формирователя импульсов и буферных каскадов дешифраторов.

Целью изобретения является упрощение устройства.

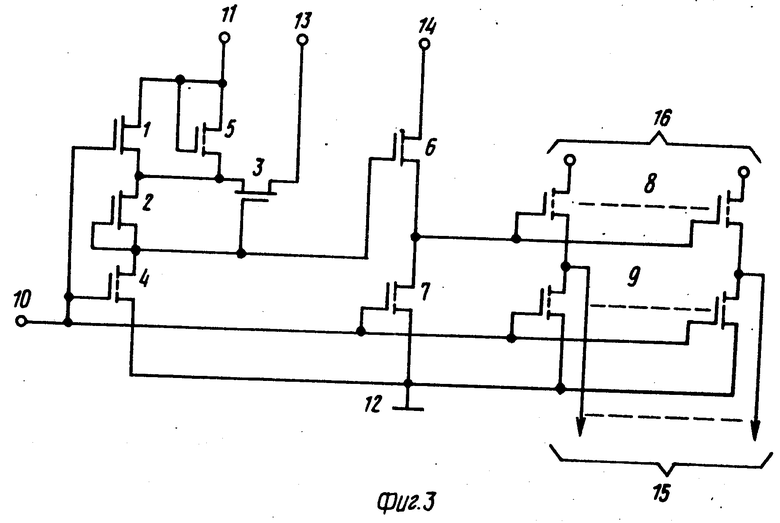

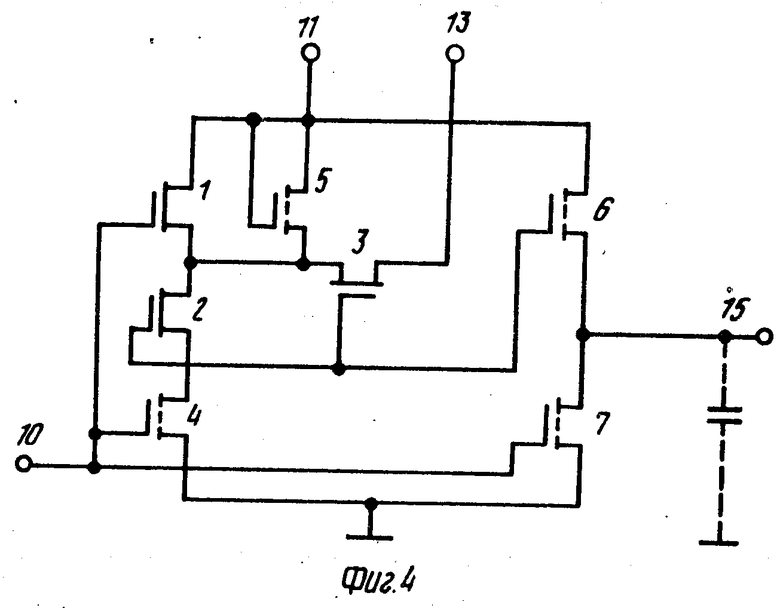

На фиг.1 показана схема буферного устройства; на фиг.2 - вариант схемы буферного устройства; на фиг. 3 - вариант схемы буферного устройства при использовании его в качестве дешифратора; на фиг.4 - вариант схемы буферного устройства при использовании его в качестве формирователя импульсов.

Буферное устройство включает транзисторы 1, 2 и 3 обедненного типа, транзисторы 4-9 обогащенного типа, входную шину 10, первую шину питания 11 (5 В), шину нулевого потенциала 12, вторую 13 и третью 14 шины питания. Причем сток транзистора 1 соединен со стоками транзисторов 5 и 8, затвором транзистора 5 и первой шиной питания 11 (5 В), затвор транзистора 1 - с затворами транзисторов 4, 7 и 9 и входной шиной 10, исток транзистора 1 - со стоком транзистора 2 и истоками транзисторов 3 и 5, затвор и исток транзистора 2 объединены и соединены со стоком транзистора 4 и затворами транзисторов 3 и 6, сток транзистора 3 соединен с второй шиной питания 13, сток транзистора 6 - с третьей шиной питания 14, исток транзистора 6 - со штоком транзистора 7 и затвором транзистора 8, исток транзистора 8 - со стоком транзистора 9 и выходной шиной 15, истоки транзисторов 4, 7 и 9 соединены с шиной нулевого потенциала 12.

Буферное устройство (см. фиг.1) работает следующим образом.

В схеме необходимо, чтобы

uпв1>Uu+uпор6+uпор8;

uпв2>Uu+uпор6, (1)

uпв1- потенциалы второй шины питания;

uпв2 - потенциал третье шины питания;

uпор6, uпор8 - пороговое напряжение транзисторов 6 и 8 с учетом коэффициента влияния подложки;

Uu - напряжение первой шины питания (обычно 5 В).

Примерные значения

uпв1 ≈ 12-15 В;

uпв2 ≈ 8-10 В. (2)

Когда на входную шину 10 поступает напряжение уровня логической единицы (обычно 5 В), транзисторы 1, 4, 7 и 9 открываются. Транзистор 4 разряжает затвор транзисторов 3 и 6 до уровня логического нуля (примерно 0,1-0,2 В). Затвор транзисторов 8 и выходная шина 15 разряжаются через транзисторы 7 и 9 до уровня 0 (ноль) вольт.

В этой схеме размеры транзисторов 1 и 2 имеют следующие соотношения:

W1/L1W2/L2, (3) где W1 - ширина канала транзистора 1;

W2 - ширина канала транзистора 2;

L1 - длина канала транзистора 1;

L2 - длина канала транзистора 2.

Транзистор 2, кроме того, включен как источник постоянного тока. И в связи с тем, что на затворе транзистора 1 - уровень логической единицы (обычно 5 В), на источниках транзисторов 1 и 3 устанавливается потенциал, близкий к напряжению источника низковольтного питания (5 В). Так как затвор транзистора 3 разряжен, а на его источнике имеется потенциал, близкий к напряжению источника низковольтного питания (5 В), транзистор 3 закрывается по истоку. Так как транзисторы 3 и 6 закрыты, то потребление по шинам повышенного напряжения 13 и 14 отсутствует.

При переключении сигнала на входной шине 10 из уровня логической единицы в уровень логического нуля транзисторы 1, 4, 7 и 9 закрываются, причем транзистор 1 закрывается по истоку.

В связи с падением напряжения на затворе транзистора 1 потенциал на его истоке стремится уменьшиться, но одновременно включаются транзисторы 3 и 5, причем транзистор 5 не дает напряжению упасть ниже уровня

u1 ≈ Uu-Uпор5, (4) где u1 - потенциал, который способен поддержать транзистор 5;

uпор5 - пороговое напряжение транзистора 5 с учетом коэффициента влияния подложки.

Одновременно с этим начинается заряд затвора транзистора 6 через транзисторы 2, 3 и 5. По мере нарастания напряжения транзистор 5 закрывается по истоку, а затвор транзистора 6 через транзисторы 2 и 3 заряжается до уровня потенциала второй шины питания 13 (uпв1 ).

Буферное устройство может работать и без транзистора 5, но с несколько худшим быстродействием, так как заряд затвора транзистора 6 проходит только через транзисторы 2 и 3.

Транзистор 6 открывается и на затвор транзистора 8 согласно формуле (1) передается напряжение

u2> Uu+ uпор8, (5) где u2 - напряжение на затворе транзистора 8.

В связи с этим транзистор 8 заряжает выходную шину 15 до уровня Uu, несмотря на величину порогового напряжения транзистора 8. Причем, так как транзисторы 4 и 7 закрываются, статическое потребление по шинам повышенных напряжений отсутствует. Напряжение uпв1 заряжает лишь затвор транзистора 6, а uпв2 заряжает затвор транзистора 8. Вследствие этого буферное устройство может работать от внутреннего источника повышенных напряжений (умножителя).

В варианте выполнения буферного устройства (см.фиг.2) вторая 13 и третья 14 шины питания объединены в одну шину повышенного напряжения 13. Схема, изображенная, на фиг. 2, работает аналогично схеме на фиг.1. Для работы схемы необходимо обеспечить

uпв> Uu+uпор6+uпор8, (6) где uпв - потенциал повышенного напряжения.

Примерное значение

uпв ≈ 12-15 В. (7)

При использовании буферного устройства в качестве дешифратора к устройству подводятся шины предварительной дешифрации 16 (от предварительного дешифратора или стокового декодера), а транзисторы 8 и 9 разделены на ряд параллельно включенных транзисторов, причем стоки транзисторов 8 соединены с шинами предварительной дешифрации 16, а истоки транзисторов 8 соединены со стоками транзисторов 9 и выходными шинами 15.

Схема, изображенная на фиг.3, работает аналогично схемам на фиг.1 и 2. Необходимо отметить, что при приходе сигнала логической единицы на входной шине 10 выходные шины 15 заземляются, а при приходе сигнала логического нуля на входную шину 10 выходные шины подключаются к шинам предварительной дешифрации 16. Для работы схемы необходимо обеспечить интегральные по времени токи (при переключении дешифратора с частотой 1 МГц)

I1≥3-5 мА для uпв1 ;

I2≥20-25 мА для uпв2 . (8)

Схема буферного устройства, изображенная на фиг.4, отличается от схемы на фиг. 2 тем, что при использовании устройства в качестве формирователя импульсов при небольшой величине выходной емкости в схеме отсутствуют транзисторы 8 и 9, причем сток транзистора 6 соединен с шиной источника низковольтного питания 11, а исток транзистора 6 соединен с выходной шиной 15.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

| Дешифратор для запоминающего устройства | 1981 |

|

SU980160A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ НА МДП-ТРАНЗИСТОРАХ | 1991 |

|

RU2088979C1 |

| Адресный формирователь | 1981 |

|

SU1007133A1 |

| ДЕШИФРАТОР | 2005 |

|

RU2307405C2 |

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| Формирователь импульсов | 1984 |

|

SU1226527A1 |

| Дешифратор адреса | 1981 |

|

SU966905A1 |

Изобретение относится к вычислительной технике и предназначено для использования в полупроводниковых интегральных схемах в качестве формирователя импульсов и буферных каскадов дешифраторов. Цель изобретения - упрощение устройства. Буферное устройство включает первый 1, второй 2, третий 3 транзисторы обедненного типа, четвертый 4, пятый 5, шестой 6, седьмой 7, восьмой 8 и девятый 9 транзисторы обогащенного типа, входную шину 10, первую шину питания 11, шину нулевого потенциала 12, выходную шину 15, а также вторую 13 и третью 14 шины питания. Введение второй 13 и третьей 14 шин питания, имеющих повышенное напряжение по сравнению с первой шиной питания 11, позволяет исключить из устройства "бутстрепные" конденсаторы, а также уменьшить зависимость от величины порогового напряжения транзисторов. 4 ил.

БУФЕРНОЕ УСТРОЙСТВО, включающее первый, второй и третий транзисторы обедненного типа, четвертый, пятый, шестой, седьмой, восьмой и девятый транзисторы обогащенного типа, входную шину, первую шину питания, шину нулевого потенциала, выходную шину, при этом сток первого транзистора соединен со стоком пятого и восьмого транзисторов и первой шиной питания, затвор первого транзистора - с затворами четвертого, седьмого и девятого транзисторов и входной шиной, исток первого транзистора - со стоком второго транзистора, затвор и исток второго транзистора соединены со стоком четвертого транзистора и затвором шестого транзистора, исток шестого транзистора соединен со стоком седьмого транзистора и затвором восьмого транзистора, исток восьмого транзистора - со стоком девятого транзистора и выходной шиной, истоки четвертого, седьмого и девятого транзисторов соединены с шиной нулевого потенциала, отличающееся тем, что, с целью упрощения устройства, в него введены вторая и третья шины питания, причем сток третьего транзистора соединен с второй шиной питания, затвор третьего транзистора - с истоком второго транзистора, исток третьего транзистора - с истоками первого и пятого транзисторов, затвор пятого транзистора - с первой шиной питания, сток шестого транзистора - с третьей шиной питания.

| Патент США N 4176289, кл.H 03K 17/60, 1979. |

Авторы

Даты

1994-12-30—Публикация

1987-10-26—Подача