113

Изобретение относится к импульсной технике и может быть использовано в интегральных схемах динамического типа на МДП-транзисторах.

Цель изобретения - повышение быстродействия и расширение области применения.

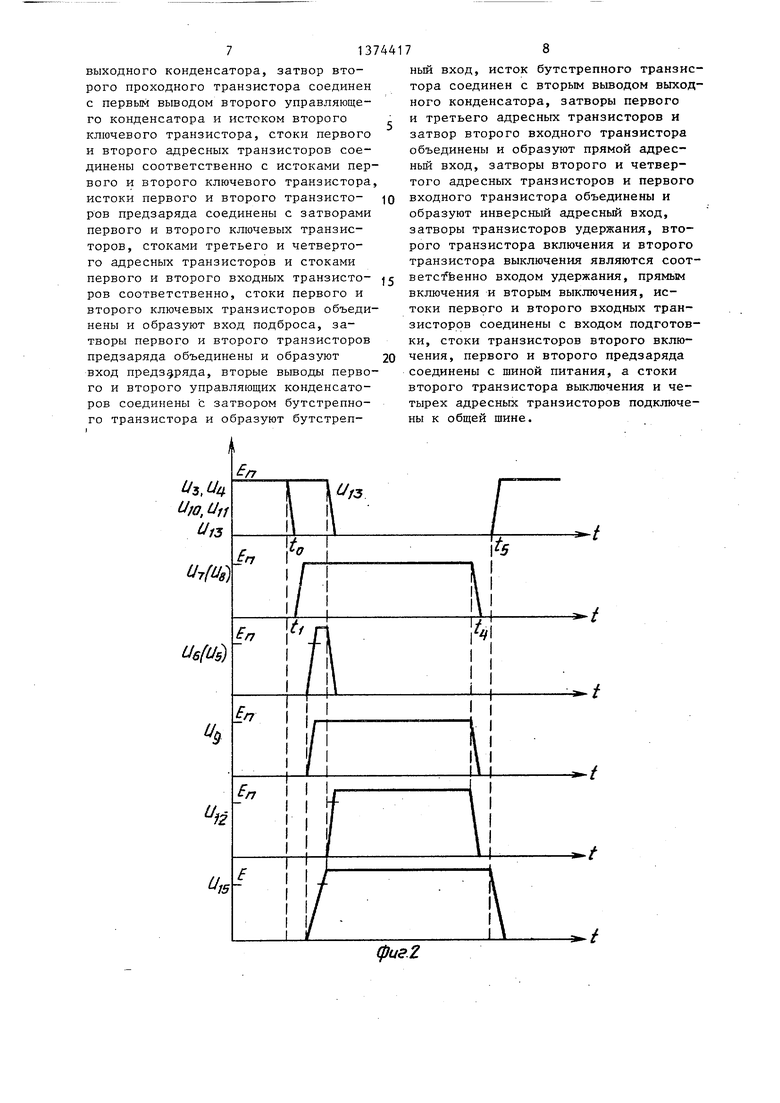

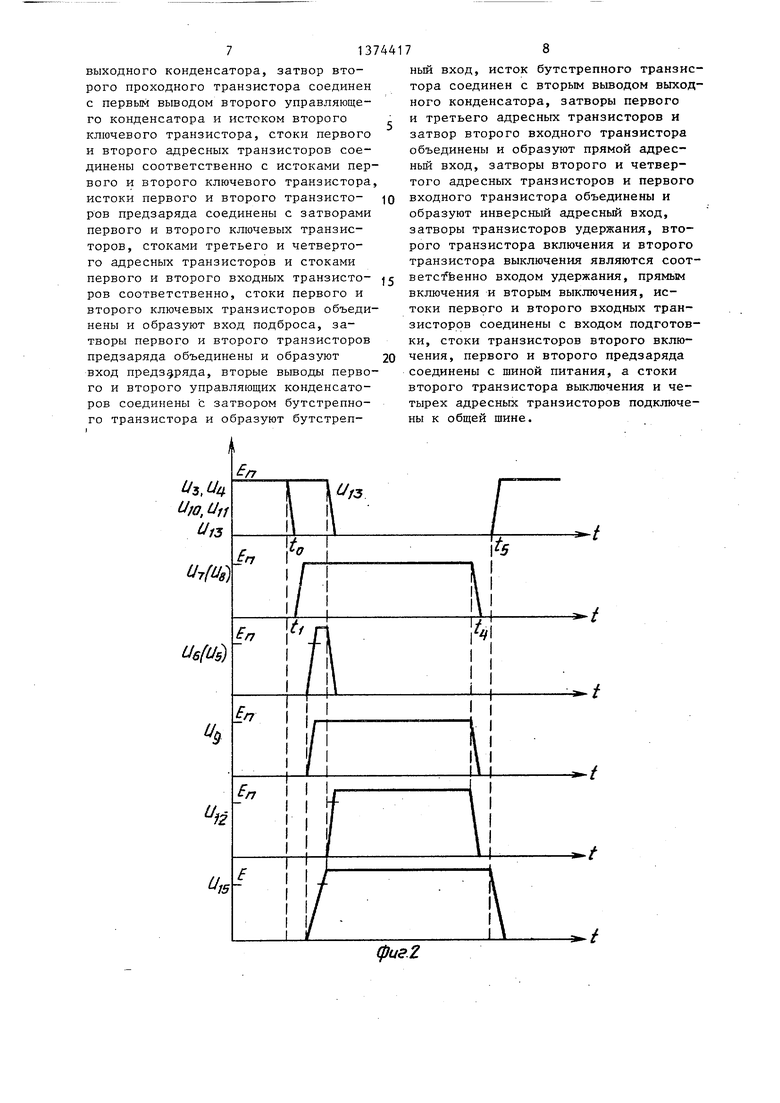

На фиг. 1 изображена схема устройства; на фиг. 2 - временные диаграм- мы сигналов на входах и выходных шинах устройства.

Формирователь импульсов содержит шину питания 1, общую шину 2, входы первый выключения 3, второй выключе- ния 4, инверсный включения 5, прямой включения 6, прямой адресный 7, инверсный адресный 8, подброса 9, предзаряда 10, удержания Г, бут- стрепный 12, подготовки 13, первую 14 и вторую 15 выходные шины, транзисторы первый выключения 16, первый включения 17, первьш проходной 18, первый клочевой 19, первый адресный 20,.первьш предзаряда 21, второй адресный 22, первый входной 23, второй выключения 24, второй включения 25, второй проходной 26, второй ключевой 27, третий адресный 28, второй предзаряда 29, четвертый адресный 30 второй входной 31, удержания 32, подготовки 33, бутстрепньш 34, конденсаторы первый управляюш;ий 35, второй управляющий 36, выходной 37.

Сток первого транзистора выключения 16 соединен с истоком первого транзистора включения 17, первой выходной шиной 14 и истоком первого проходного транзистора 18, затвор которого подключен к истоку первого ключевого транзистора 19, стоку первого адре.сного транзистора 20, первому выводу первого управляющего конденсатора 35, затвор первого ключевого .транзистора 19 соединен с исто- ком первого транзистора предзаряда 21, стоком третьего адресного транзистора 22 и стоком первого входного транзистора 23, сток второго транзистора выключения 24 соединен с истоком второго транзистора включения 25 второй выходной шиной 15 и истоком второго проходного транзистора 26, затвор которого подключен к истоку второго ключевого транзистора 27,

стоку второго адресного транзистора 22 и первому -выводу второго управляющего конденсатора 36, затвор второго ключевого транзистора 27 соединен с

O

0 5 0

Q с

5

0

5

истоком второго транзистора предза- ряда 29, стоком четвертого адресного транзистора 30 и стоком второго входного транзистора 31, стоки первого проходного 18 и второго проходного 26 транзисторов подключены к истоку транзистора удержания 32 и первому выводу выходного конденсатора 37, второй вывод которого соединен со стоком транзистора подготовки 33 и истоком бутстрепного транзистора 34, затвор которого подключен ко вторым выводам первого управляющего 35 и второго управляющего 36 конденсаторов, стоки первого 17 и второго 25 транзисторов включения, первого 21 и второго 29 транзисторов предзаряда, транзистора: удержания 32 и бутстрепного транзистора 34 соединены С шиной питания 1, истоки первого 16 и второго 24 транзисторов выключения, транзистора подготовки 33, первого 20, второго 22, третьего 28 и четвертого 30 адресных транзисторов соединены с общей шиной 2, затворы первого 16 и второго 24 транзисторов выключения образуют соответственно первый 3 и второй 4 входы выключения, затвора первого 17 и второго 25 транзисторов включения образуют соответственно инверсный 5 и .прямой 6 входы включения, затворы первого 20 и третьего 28, второго 22 и четвертого 30 адресных транзисторов попарно объединены и образуют соответственно прямой 7 и инверсный 8 адресные входы, стоки первого 19 и второго 27 ключевых транзисторов объединены и образуют вход подброса 9, затворы первого 21 и второго 29 транзисторов предзаряда объединены и образуют вход предзаряда 10, затворы транзисторов удержания 32, бутсрепного 34 и подготовки 33 являются соответственно входами удержания 11, бутстрепньш 12 и подготовки 13, истоки первого 23 и второго 31 входных транзисторов соединены с входом подготовки 13.

Формирователь импульсов работает следующим образом.

В исходном состоянии на входах первом 3 и втором 4 выключения, удержания 11, подготовки 13 и предзаряда 10 установлен высокий уровень напряжения Е, равный напряжению на шине питания 1. При зтом, первый 16 и второй 24 транзисторы выключения

313

открыты и первая 14 и вторая 15 выходные шины подключены к общей шине 2, на выходных шинах 14 и 15 установлены низкие уровни напряжения Транзистор подготовки 33 открыт и на втором выводе выходного конденсатора 37 установлен низкий уровень напряжения, а через открытый транзистор удержания 32 первый вывод вы- ходного конденсатора 37 заряжен до высокого уровня напряжения.

Первый 21 и второй 29 транзисторы предзаряда открыты и на затворах первого 19 и второго 27 ключевых транзисторов установлены высокие уровни напряжения. На входах включения прямом 6 и инверсном 5, адресных входах прямом 7 и инверсном 8, входах подброса 9 и бутстрепном 12 установлены низкие уровни напряжения Формирователь приведен в исходное состояние.

Поскольку сигналы на прямом 6 и инверсном 5 входах включения, а так- же на прямом 7 и инверсном 8 адресных входах являются взаимно допол- няюш;ими, т.е. при подаче высокого уровня напряжения на прямой вход включения 6 (прямой адерсный вход 7) инверсный вход включения 5 (инверсный адресный вход 8) остается в низком состоянии, рассмотрим работу формирователя в одном случае, когда сигналы высокого уровня подаются на прямой вход включения 6 и прямой адресный вход 7.

В момент времени t (фиг. 2) на входах первом 3 и втором 4 выключения, удержания 11 и предзаряда 10 ус- танавливается низкий уровень напряжения и транзисторы первый 16 и второй 24 выключения, удержания 32, первый 21 и второй 29 предзаряда переходят в закрытое состояние.

В момент времени t (фиг. 2) на прямом адресном входе 7 устанавливается высокий уровень напряжения, при этом первый 20 и третий 28 адресные транзисторы открываются и через тре- тий 28 адресный транзистор низкий уровень передается на затвор первого 19 ключевого транзистора и он запирается.

В момент времени t (фиг. 2) на прямой вход включения 6 подается бут- стрепный уровень напряжения И Е,+И-,, где И,. - пороговое напряжение, а на вход подброса 9 - высокий уровень на

5 0

5 0

0

5

17

пряжения . При этом, второй транзистор включения 25 открывается и вторая выходная шина 15 заряжается до высокого уровня напряжения Е. В то же время через открытый второй ключевой транзистор 27 заряжается первый вывод второго управляющего конденсатора 36 до уровня напряжения Е . В то же время через открытый второй ключевой транзистор 27 заряжается первый вывод второго управляющего конденсатора 36 до уровня напряжения ЕГ,. Затвор и исток второго 26 проходного транзистора заряжаются одновременно до уровня Ер, поэтому он закрыт и выходной конденсатор 37 изолирован от емкости нагрузки второй выходной шины 15, что позволяет полностью сохранить заряд выходного конденсатора 37.

В момент времени tj (фиг. 2) на прямой вход включения 6 и вход подготовки 13 подается низкий уровень напряжения, второй транзистор включения 25 закрывается и вторая выходная шина 15 отключается от шины питания 1, транзистор подготовки 33 закрывается, второй входной транзистор 31, на затворе которого установлен высокий уровень напряжения, открывается по цепи истока и на затворе второго ключевого транзистора 27 устанавливается низкое напряжение, он закрьшается. В этот же момент времени на бутстрепный вход 12 подается уровень напряжения U, который переда ется через второй управляющий конденсатор 36 на затвор второго проходного транзистора 26 и повышает его напряжение до уровня , а также открывает бутстрепный транзистор 34, и уровень напряжения на втором выводе выходного конденсатора 37 становится равным Е. Уровень напряжения на первом выводе выходного конденсатора 37 повышается до величины Uj и через открытый второй проходной транзистор 26, на затворе которого установлено напряжение И Еп+2Иг, передается на вторую выходную шину 15. Нагрузка, подключенная к второй выходной шине 15, заряжается до напряжения %.

Затвор первого проходного транзистора 18 соединен с общей шиной 2 через открытый первый адресный транзистор 20, поэтому первый проходной транзистор 18 все это время закрыт.

В момент времени t (фиг. ) на

бутстрепном входе 12, прямом адресном входе 7 и входе подброса 9 устанавливается низкий уровень напряжения, транзисторы бутстрепный 34, первый 20, и третий 28 адресные, второй входной 31 и второй проходной 26 закрываются, В момент времени t

(фиг. 2) на входы предзаряда 10, под-ю меньше, чем емкость на выходе извествая и вторая выходные шины полностью независимы по управлению.

При формировании сигнала выборки строки и/или столбца емкость нагрузки разделяется поровну на две группы, которые подключаются к первой и второй выходным шинам, поэтому емкость нагрузки на каждой выходной шине

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1985 |

|

SU1374416A1 |

| Формирователь импульсов | 1982 |

|

SU1091327A1 |

| Дешифратор | 1989 |

|

SU1644222A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Адресный формирователь | 1988 |

|

SU1624521A1 |

| Устройство для записи информации в МДП динамический-матричный накопитель | 1982 |

|

SU1091222A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

Изобретение может быть использовано в интегральных схемах динамического типа на ЬЩП - транзисторах. Целью изобретения является повышение быстродействия формирователя и расширение области его применения. Формирователь содержит шину 1 питания, общую шину 2, входы: выключения 3 и 4, инверсный включения 5, прямой включения 6, прямой адресный 7, инверсный адресный 8, подброса 9, перезаряда 10, удержания 11, бутстреп- ный 12, подготовки 13; выходные шины: первую 14, вторую 15; транзисторы: включения 16 и 24, включения 17 и 25, проходной 18, ключевые 19 и 27, адресные 20, 22, 28 и 30, перезаряда 21 и 29, входные 23 и 31, проходной 26, удержания 32, подготовки 33, бутстрепный 34; конденсаторы: управляющие 35 и 36, выходной 37. Расширение области применения достигается за счет введения второй выходной шины 15, что позволяет использовать формирователь без дополнительного блока селекции сигнала при получении сигнала по двум шинам. Формирователь предпочтительно использовать для формирования сигнала выборки строки и/или столбца, поскольку первая и вторая выходные шины полностью независимы по управлению. Снижение емкости на каждой выходной шине по сравнению с прототипом повышает быстродействие предложенного формирователя импульсов. 2 ил. (Л со ч 4 4

готовки 13, удержания 11, первый 3 и второй 4 выкл очения подаются высокие уровни напряжения. Через открытый второй транзистор выключения 24 вторая выходная шина 15 разряжается. На первом выводе выходного конденсатора 37 через открытый транзистор удержания 32 устанавливается высокий уровень напряжения, на второй его вьшоде через открытый транзистор под готовки 33 - низкий, на затворах ключевых транзисторов 19 и 27 через открытые транзисторы предзаряда 21 и 29 - высокий уровень напряжения, а на затворах проходных транзисторов 18 и 26 через открытые ключевые транзисторы 19 и 27 - низкий уровень напряжения. Формирователь вернулся в исходное состояние и готов к новому циклу работы.

Для получения выходного сигнала первой выходной шине 14 необходимо подать сигналы на инверсный вход включения 5 и инверсный адресный вход 8, при этом на прямой вход, включения 6 и на прямой адресный вход 7 должны быть поданы низкие уровни напряжения.

Для упрощения схем управления и топологии формирователя импульсов возможно объединение входов первого 3 и второго 4 выключения, предзаряда 10 и удержания 11, поскольку сиг- налы, подаваемые на эти входы совпадают (фиг. 2), при этом транзисторы удержания 32, первый 21 и второй 29 предзаряда могут быть со встроенными каналами.

Расширение области применения достигается введением второй выходной шины, что позволяет использовать формирователь без дополнительного блока селекции сигнала в случае необходимости получения сигнала по двум выходным шинам.

Данный формирователь импульсов предпочтительнее использовать- в качестве формирователя сигнала выборки строки и/или столбца, поскольку пер

5

25

30

20

35

40

45

50

55

ного устройства, что повышает быстродействие предложенного формирователя импульсов.

Формула изобретения Формирователь импульсов, содержащий первьш транзистор выключения, блок которого соединен с первой выходной шиной, с истоками первого транзистора включения и первого проходного транзистора, сток которого подключен к истоку транзистора удержания и первому выводу выходного конденсатора, затвор первого проходного транзистора соединен с первьш выводом первого управляющего конденсатора и истоком первого ключевого транзистора, транзистор подготовки, сток которого соединен с истоком бут- стрепного транзистора, стоки первого транзистора включения, транзистора удержания и бутстрепного транзистора подключены к шине питания, истоки первого транзистора выключения и транзистора подготовки подключен к общей шине, затворы первого транзистора включения, первого транзистора выключения, транзистора подготовки образуют соответственно входы инверсный включения, первый выключения и подготовки, отличающийся тем, что, с целыб повьш1ения быстродействия и области применения, в него введены вторая выходная шина, второй транзистор включения, второй транзистор выключения, второй проходной транзистор, второй ключевой транзистор, первый и второй транзисторы предзаряда, с первого по четвертый адресные транзисторы, первый и второй входные транзисторы и второй, управляющий конденсатор, причем сток второго транзистора выключения соеди- нен с второй выходной шиной, с истоками второго транзистора включения и второго проходного транзистора, сток которого подключен к первому выводу выходного конденсатора, сток которого подключен к первому выводу

и,-/

1

(риг.2

| СПОСОБ ПОЛУЧЕНИЯ НЕКУРИТЕЛЬНОГО ИЗДЕЛИЯ ИЗ МАХОРКИ | 2010 |

|

RU2432799C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-15—Публикация

1985-01-31—Подача