со

со

со

00

Изобретение относится к вычислительной технике и может быть использовано для преобразования и цифровой обработки сигналов с высокой разрешающей способностью.

Цель изобретения - повьшение быстродействия устройства.

Сущность изобретения заключается в том, что для повьщ1рния скорости цифрового преобразов ания дискретных отсчетов входного сигнала при расчете параметров каждой.частотной составляющей многократно используются только короткие операции - сло длинная

жение и вычитание, а длинная операция - деление - выполняется только один раз для коррекции результатов вычислений. Алгоритм выполнения такого преобразования определяется еле дующими соотношениями: г 1, п 1,

F(K,t) х1-(51ао.,розыЛ+ 2п ;.о ° tro

, sin );()

j

5

(Ji ii (

-((

г N1 где ,1,..., я - порядковьй

гармоники;

число отсчетов входного сигнала Объем выборки ; 35 ,Х ц, - значения отсчетов сигнала;

N у- 1

2 (I круговая частота К-й

составляющей;

F, - частота дискретизации входного сигнала;

N 1 I - -К - шаг дискретизации для

К-й составляющей;

40

45

N ЗН °

полных периодов К-й

0

5

0

5

0

5 0

5

реса 1 и 2, блок 3 синхронизации, вычислительный блок А, аналого-цифровой преобразователь (АЦП) 5, блок 6 памяти операндов и три блока 7-9 памяти результатов, информационный вход 10 устройства, вход 11 задания щага дискретизации, три информационных выхода 12-14 устройства и выход 15 окончания вычислений устройства.

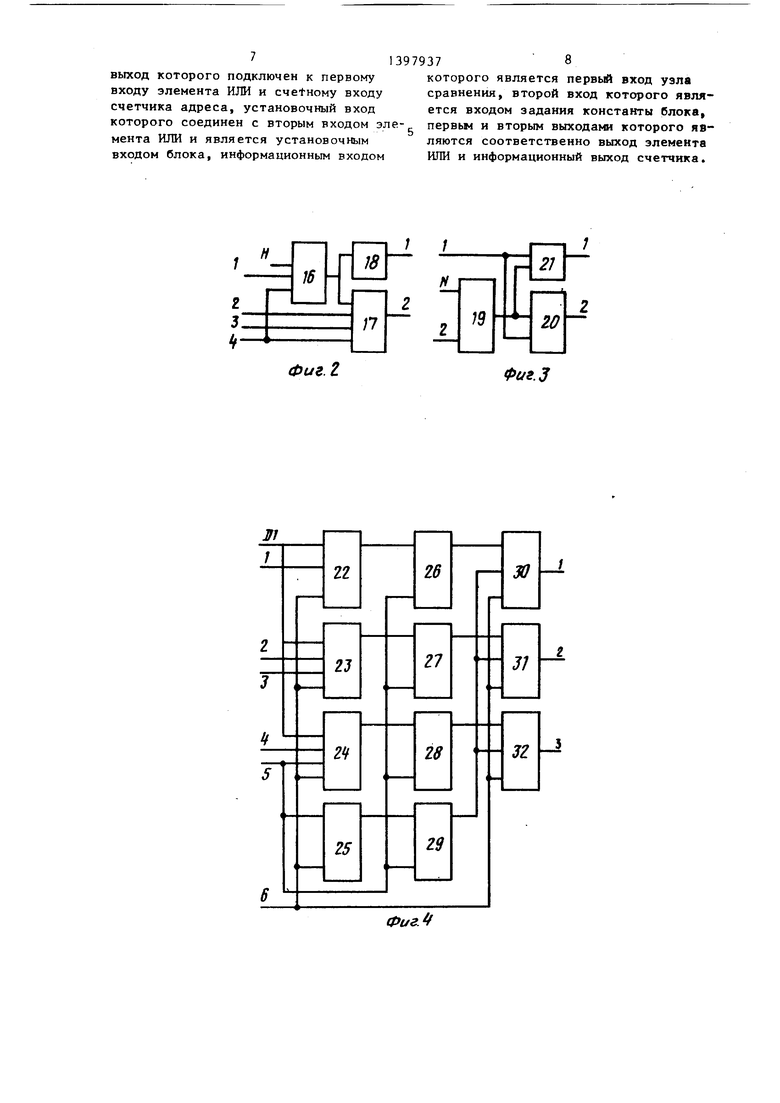

Первый блок 1 вычисления адреса (фиг. 2) содержит вычитающий счетчик 16, накапливающий сумматор 17 и элемент ИЛИ 18.

Второй блок 2 вычисления адреса (фиг. 3) содержит узел 19 сравнения, счетчик 20 адреса и элемент ИЛИ 21.

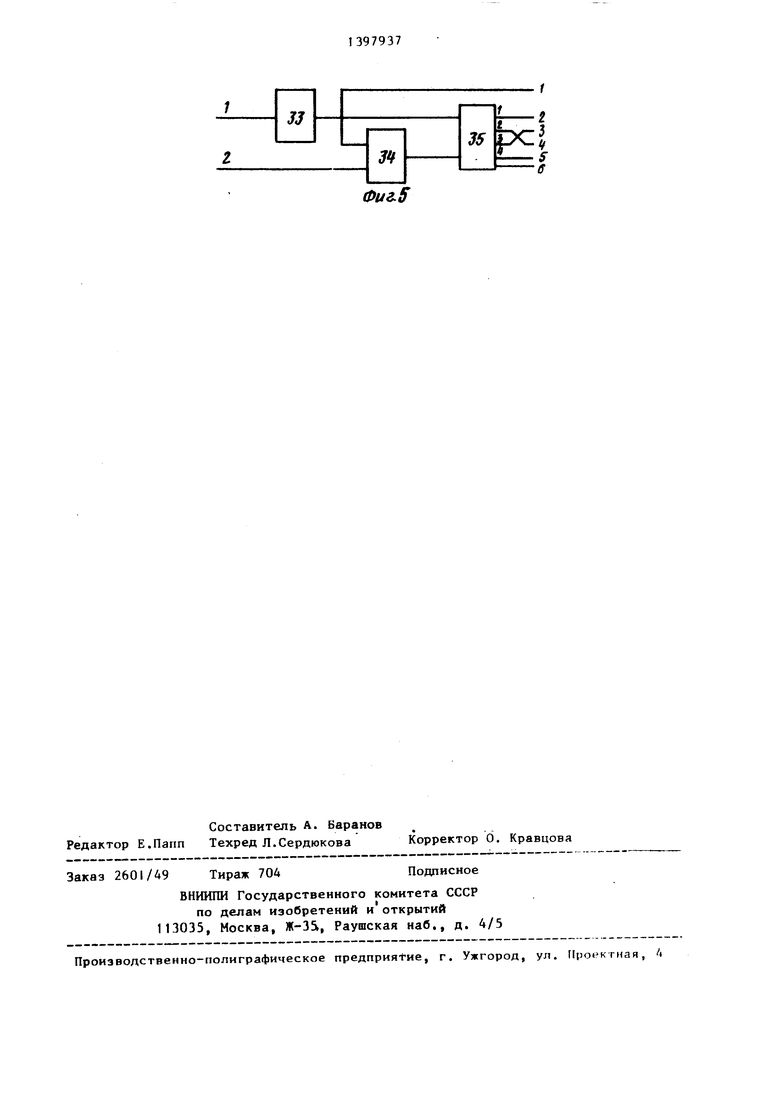

Вычислительный блок 4 (фиг. 4) содержит накапливающий сумматор 22, два накапливающих сумматора-вычита- теля 23 и 24, счетчик (периодов) 25, четыре (буферных) регистра 26-29 и три делителя 30-32.

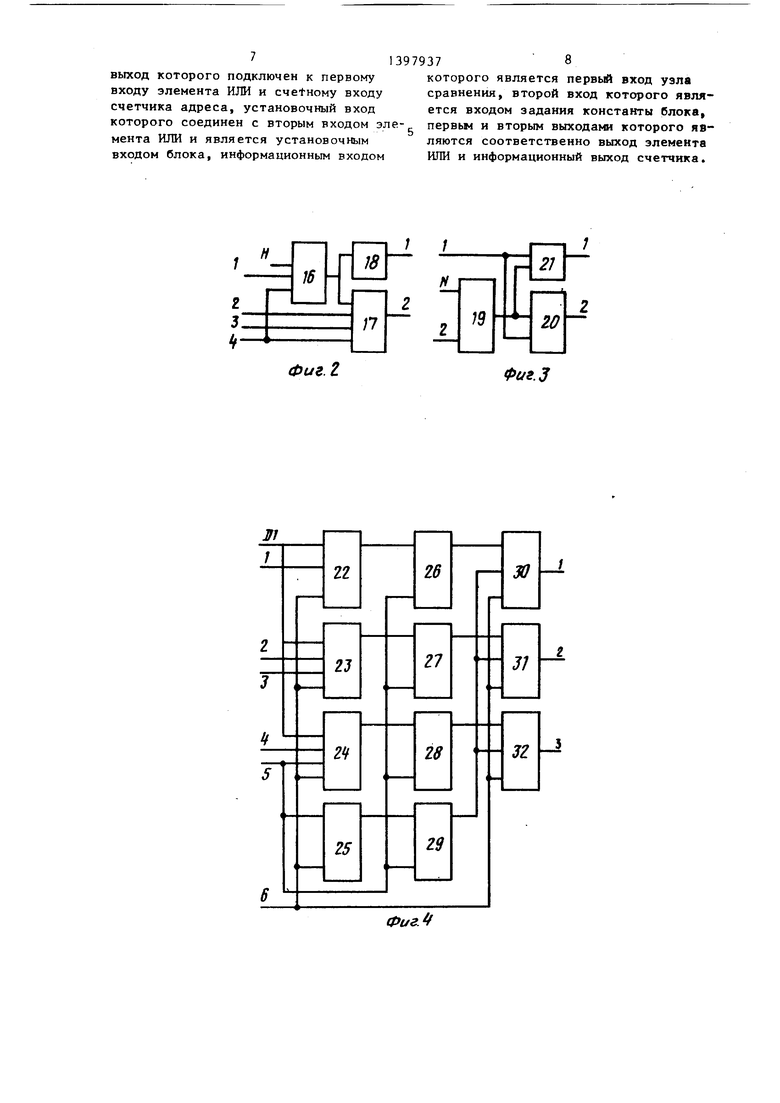

Блок 3 синхронизации (фиг. 5) содержит генератор 33 тактовых импульсов счетчик (суммирующий)34 и дешифратор 35.

Устройство работает следующим образом.

В состоянии Останов (низкий - уровень сигнала на выходе 15 устройства, связанном с выходом элемента ИЛИ 18) в блок 6 памяти операндов с выхода 5 загружается выборка из N дискретных отсчетов входного сигНа- ла, поступающего на информационный вход 10 устройства. При этом накапливак1щие сумматоры 17 и 22, сумматоры-вычитатели 23 и 24 и счетчики - вычитающий 16, адреса 20 и суммирующий 34 - нахЬдятся в сброшенном состоянии ,

Процесс вычисления начинается с занесения в вычитающий счетчик 16 начального значения шага дискретиза11 1И

-11

по внешнему сигналу, по

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Генератор нормально распределенных случайных чисел | 1984 |

|

SU1226450A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Цифровой функциональный генератор | 1985 |

|

SU1282104A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Фурье-Чебышеву | 1983 |

|

SU1136181A1 |

| Генератор функций Уолша | 1985 |

|

SU1262470A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1312611A1 |

составляющей.

На фиг. 1 приведена структурная схема устройства, реализующего алгоритм (l); на фиг. 2 и 3 - структурные схемы соответственно первого и второго блоков формирования адреса; на фиг. 4 - структурная схема вычислительного блока; на фиг.5 - структурная схема блока синхронизации.

Устройство (фиг. 1) содержит первый и второй блоки формирования ад

ступающему на вход 11 устройства. При зтом на вьжоде элемента ИЛИ 18 появляется высокий уровень сигнала, к оторый фиксирует переход устройства в состояние Работа и разрешает работу генератора 33 тактовых импульсов и счетчика 20 адреса.

По первому импульсу ТИ с выхода генератора 33 тактовых и myльcoв из блока 6 памяти операндов по адресу А(Й, сформированному в накапливающем сумматоре 17, считыряется значение

отсчета Х и складывается с нулевым содержимым накапливающих сумматора 22 и сумматора-вычнтателя 23, так как импульс ТИ поступает на суммирующий вход последнего с первого выхода дешифратора 35.

По срезу импульса ТИ в накапливающем сумматоре 17 формируется адрес следующего отсчета А,Ао+Н, а в сум- ю мирующем счетчике 34 - адрес второго выхода дешифратора 35.

По второму импульсу ТИ происходит приращение содержимого накапливающих сумматора 22 и сумматора-вычитателя 15 24 на величину Хц, адрес следующего отсчета на выходе накапливающего сумматора 17 становится равным 2Н, а содержимое суммирующего счетчика 34 - трем.20

По третьему импульсу ТИ значение отсчета Х2нСкладывается с накопленной суммой в накапливающем сумматоре 22, а в накапливающем сумматоре-вычита- теле 23 формируется разность ,, 5 так как импульс ТИ поступает на вьгчи- тающий вход последнего с третьего выхода дешифратора 35.

По четвертому импульсу ТИ происходит приращение содержимого накаплива- 30 ющего сумматора 22 на величину X,, а в накапливающем сумматоре-вычитате- е 24 формируется разность . При этом импульс ТИ с четвертого выхода дешифратора 35 запрещает прира- 35 щение адрес.а в накапливающем сумматоре 17, по его фронту происходит приращение счетчика 25 периодов, а по срезу - загрузка даиных с выходов накапливающих сумматора 22, сумматоров-вы- 40 читателей 23 и 24 и счетчика 25 периодов в буферные регистры 26-29 соответственно.

Далее цикл работы устройства повторяется, пока значение адреса на ыходе накапливающего сумматора 17 е окажется больше, либо равным N. огда по сигналу с выхода элемента ЛИ 21, вход которого связан с выхоом узла 19 сравнения, значения веичин с выходов делителей 30-32 заносятся в ячейки блоков 7-9 памяти езультатов по адресу, сформированому в счетчике 20 адреса, и производится сброс сумматоров 17, 22-24 и суммирующего счетчика 34 и счетчика 25 периодов. После этого на выходе узла 19 сравнения восстанавливается прежний уровень сигнала, по срезу которого

45

50

55

5

0 5 0

5

0

5

производится вычитание единицы из счетчика 16, хранящего текущее значение шага дискретизации с входа II, приращение счетчика 20 адреса и загрузка содержимого буферных регистров 26-29 в делители 30-32, На этом первая из Н итераций завершается. Каждая следующая итерация выполняется аналогично рассмотренной

Во время выполнения каждой i-й итерации на делителях 30-32 формируются значения соответственно постоянной, синусной и косинусной составляющих (i-1)-и,гармоники как частное от деления кодов чисел с выходов буферных регистров 26-29 на код числа периодов с выхода буферного регистра 29, занесенных в делители в конце предыдущей итерации.

После загрузки указанных значений в соответствующие ячейки блоков 7-9 памяти результатов они могут быть считаны оттуда соответ ственно на выходы 12-14 устройства.

Когда текущее значение шага дискретизации Н становится равным нулю, низкий уровень сигнала, поступающего с выхода элемента ИЛИ 18 на выход 15 устройства, фиксирует переход устройства в состояние Останов и запрещает работу генератора 33 тактовых импульсов.

Формула изобретения

делителей, вторые входы которых подключены к выходу четвертого регистра, информационный вход которого подключен к информационному выходу счетчика, информационные входы накапливающего сумматора, первого и второго накапливающих сумматоров-вычитателей соединены между собой и являются информационным входом блока, вход синхронизации накагшивающего сумматора, входы синхронизации суммы и разности первого накапливающего сумматора-вы- читателя и вход синхронизации суммы второго накапливающего сумматора-вычи тателя являются соответственно первым вторым, третьим и четвертым тактовыми входами блока, пятым тактовым входом которого являются соединенные между собой вход синхронизации разности второго накапливающего сумматора-вы- читателя, счетный вход счетчика и тактовые входы первого, второго, третьего и четвертого регистров, входы синхронизации первого, второго и третьего делителей соединены с установочными входами счетчика, накапливающего сумматора, первого, второго накапливающих сумматоров-вычитателей и являются шестым тактовым входом блока, первым, вторым и третьим информационными выходами которого являются выходы соответственно первого, второго и третьего делителей,

„4. Устройство по п. 1, отличающееся тем, что второй блок формирования адреса содержит элемент ИЛИ, счетчик адреса и утрл сравнения,

71397937 8

выход которого подключен к nepBONfy которого является первый вход узла входу элемента ИЛИ и CMetHOMy входу сравнения, второй вход которого явля счетчика адреса, установочный вход которого соединен с вторым входом элемента ИЛИ и является установочным входом блока, информационным входом

ется входом задания константы блока, первым и вторым выходами которого яв

ляются соответственно выход элемента ИЛИ и информационный выход счетчика.

Фиг.2

которого является первый вход узла сравнения, второй вход которого явля

ется входом задания константы блока, первым и вторым выходами которого явкоторого является первый вход узла сравнения, второй вход которого явля

ляются соответственно выход элемента ИЛИ и информационный выход счетчика.

Фиг.З

Фиг

Составитель А. Баранов Редактор Е.Пагш Техред Л.СердюковаКорректор О. Кравцова

Заказ 2601/49

Тираж 704

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Фиг.$

Подписное

| Макаревич О.Б., Спиридонов Б.Г | |||

| Цифровые процессоры обработки сигналов на основе БИС | |||

| - Зарубежная электронная техника, 1983, № 1 (259) | |||

| Устройство для изменения величины хода плунжера насоса | 1960 |

|

SU136181A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-23—Публикация

1986-10-27—Подача