Изобретение относится к вьгчислн- ; тельной технике и может быть использовано в многомашинных вычислительных системах, работающих в реальном мае- штабе времени.

Цель изобретения - повьш1ение быстродействия устройства за счет разрешения одновременного доступа обеих ЦВМ к общей памяти,

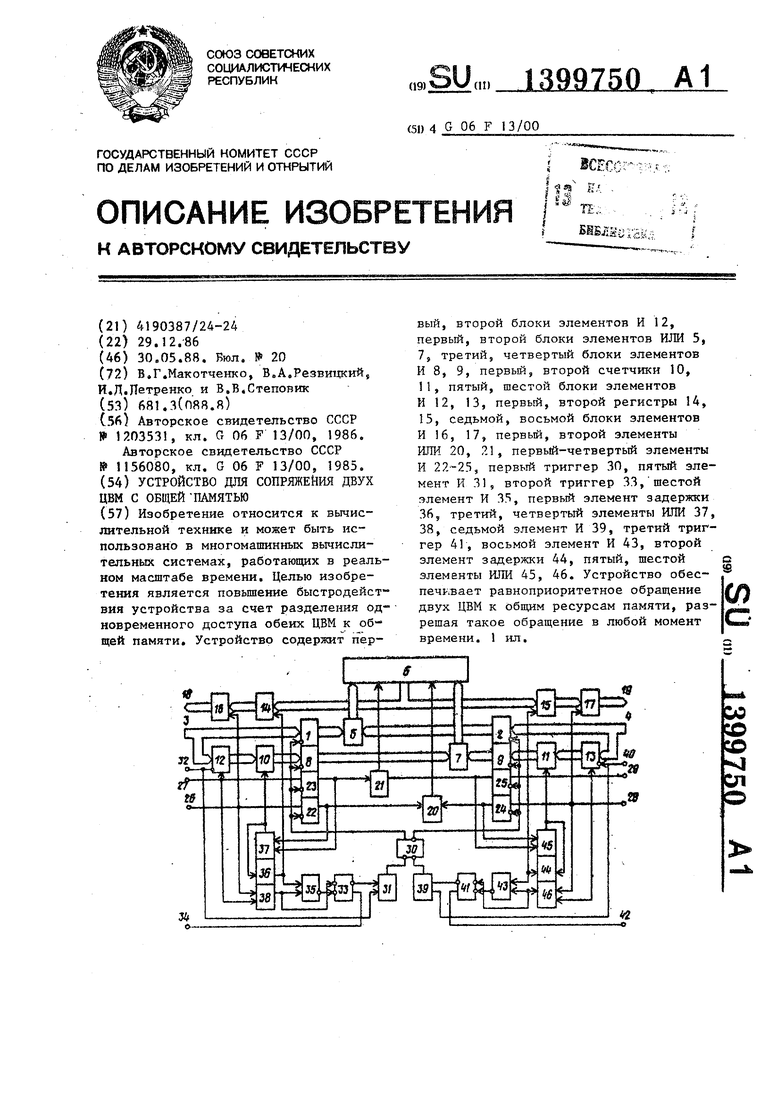

На чертеже представлена блок-схема устройства.

Устройство содержит первый 1 и второй 2 блоки элементов И входы 3 и 4 устройства для подключения информационных выходов первой,второй ЦВМ, первый блок 5 элементов ИЛИ, На чертеже изображена общая память 6, Кроме того, устройство содержит второй блок 7 элементов ИЖ, третий 8 и четвертый 9 блоки элементов И, первьй 10 и второй П счетчики, пятый 1.2 и шестой 13 блоки элементов И, первый J4 и второй 15 регистры, седьмой 16 и восьмой 17 блоки элементов И, выходы 18 и 19 устройства для подключения соответственно информационных входов первой и второй ЦВМ, первый 20 и второй 21 элементы ИЛИ, первый - четвертый элементы И 22-25 входы 26 и 27 |УСтройства для подключения соответственно выходов чтения и записи первой ЦВМ, входы 28 и 29 устройства для подключения соответственно выходов чтения и записи второй ЦВМ, первый триггер 30, пятый элемент И 31, вход 32 устройства для подключения вькода запроса первой ЦВМ, второй триггер 33, выход 34 устройства дпя подключения входа ответа первой ЦВМ, шестой элемент И 35, первый элемент 36 задержки, третий 37 и четвертый 38 элементы ИЛИ, седьмой элемент И 39, вход 40 устройства для подключения выхода запроси второй ЦВМ, тре тий триггер 41, выход 42 устройства для-подключения входа ответа второй IIBM, восьмой элемент И 43, второй элемент 44 задержки, а также пятый 45 и шестой 46 элементы ИЛИ,

Устройство работает следующим образом.

1Ьобая операция обращения ЦВМ начинается с сщресной части выборки общей памяти. После завершения адресной части цикла ЦВМ выполняет прием или передачу данных. Для выполнения операции Чте1ше или Запись в память

0 5 0 5 0

5

6 ЦВМ необходимо выполнить два такта обращения. В зависимости от обращений ЦВМ устройство имеет несколько режимов работы.

Режим обращения одной ЦВМ,

Этот режим характеризуется обращением к устройству одной ЦВМ на отрезке времени, равном времени выполнения операции ввода-вывода процессором.

Триггеры 33 и 41 находятся в нулевом состоянии, а триггер 30 - в. неопределенном (на обоих выходах единих ы), В первом такте процессор ЦВМ после aдpecarJJIИ устройства в адресной части помещает на вход 3 данные, представляюшле собой адрес ячйй- ки памяти 6, к которой необходимо обратиться, после чего на входе 27 устанавливается сигнал Вывод, означающий, что на входе 3 помещены данные. При -этом на входе 32 Запрос сигнал отсутствует. Данные через блок 12 элементов И записьшаготся в счетчик 10, Этим завершается первый такт обращения, при этом в счетчике 10 содержится адрес ячейки памяти 6, к которой необходимо обратиться.

Во втором такте обращения после адресной части на входе 32 появляется сигнал, блокирующий по инверсному входу блок 12 элементов И и занесение данных в счетчик 10, Этот же сигнал устанавливает выход элемента И 31 в единицу, что приводит к установке триггера 30 в нулевое состояние и . разрешает прохождение сигналов через блоки 1 и 8 элементов И и элементы и 22 к 23, Далее ЦВМ производит обращение к памяти 6 по адресу, содержащемуся в счетчике 10, выходы которого через блоки 8 и 7 элементов И и ИЖ подключаются к адресным-входам памя- ; ти 6,

В случае операции Чтение сигнал ввода с входа 26 через элементы И 22 и 20 подается на вход чтения памяти 6, на вьпсоде которой спустя время срабатьюания памяти 6 выставляется информация, хранящаяся в ячейке, адрес которой установлен-на адресных входах памяти 6, Сигнал ввода с выхода элемента И 22 подается на вход элемента ИЛИ 37, с выхода которого подается на вход элемента 36 задержки, время задержки которого равно времени срабатывания памяти 6, С выхода

элемента 36 задержки сигнал подается на вход записи регистра 14, фронтом этого сигнала производится запись в регистр 14 информации с входов данных на которые подана информация с выходов памяти 6. Информация с выходов регистра 14 подается на первые входы блока 16 элементов И,на вторые входы которого подается сигнал ввода с входа 26, разрешающий трансляцию данных на выход 18. Сигнал с входа 26 подается также на первый вход элемента ИЛИ 38, с выхода которого подается на нулевой вход триггера 33, разрешая переключение триггера в едини- 1, а также на второй вход элемента И 35, на первый вход которого с выхода элемента 36 задержки подается сигнал, по приходу которого на выходе элемента И 35 появляется нуль, устанавливающий триггер 33 в единицу что приводит к установке на выходе 34 ответного сигнала, информирующего первую ЦВМ о завершении устройством цикла обмена, а также к установке триггера 30 в исходное, неопределенное состояние (на обоих выходах триггера единицы), что снимает с выходов блока 8 элементов И и элемента И 22 сигналы. ЦВМ снимает сигнал с входа 26, что приводит к снятию сигнала с выхода элемента ИЛИ 38 и к установке триггера 33 в исходное, нулевое состояние. Далее ЦВМ снимает сигнал с входа 32, что является признаком завершения обмена с устройством,

В случае операции Запись сигнал вьшода с входа 27 (сигнал запроса на входе 32 уже установлен, триггер 30 установлен в нулевое состояние) через элементы И 23 и ИЛИ 21 подается на вход управления записью памяти 6, на адресных входах которого установлен адрес ячейки с вькодов. счетчика 10, а на входах данных - данные, которые необходимо записать (подаются с входа 3 через блоки 1 и 5 элементо И и или), В остальном работа устройства аналогична описанной для операции Чтение, т.е. сигнал Вьшод с входа 27 через элементы И 23 и ИЛИ 3 подается на вход элемента 36 задержки, задерживающего его сигнал на время срабатывания памяти 6. Сигнал с выхода элемента 36 задержки производит запись в регистр 14 ложной в этом случае информации, но так как

блок 16 элементов И не транслирует данные в шину 18, это несущественно. Режим последовательного обращения

двух ЦВМ.

Этот режим характеризуется последовательным обращением к устройству двух ЦВМ на отрезке времени, равном времени выполнения операции вводавывода процессором. Например, одна ЦВМ производит операцию ввода-вьгоода с устройства, а в это время вторая ЦВМ также обратилась к устройству. В этом случае устройство работает

следующим обраяом. Работа элементов устройства происходит аналогично описанной в режиме обращения одной ЦВМ.

Первый, адресный, такт происходит

аналогично описанному. При этом в

счетчик 11 записьюается адрес, по которому требуется обращение к памяти 6. Во втором такте сигнал с входа 40 приведет в появлению на выходе элемента И 39 единицы. Далее вторая ЦВМ выставляет управляющий сигнал (на входе 28 или 29). При завершении обмена с устройством первой ЦВМ триггер 33 устанавливается в единичное состояние, что приводит к появлению на единичном входе триггера 30 нуля и к перебросу триггера 30 в единичное состояние. Нулевой сигнал с нулевого выхода триггера 30 подается на вторые

входы блоков 2 и 9 элементов И и элементов И 24 и 25, разрешая прохождение данных, адреса и управляющих сигналов,

В случае одновременного обращения

к устройству двух ЦВМ первые такты обращения - занесение адресов в счетчики - происходит одновременно и независимо. Во вторьк тактах обе ЦрМ выставляют сигнал на входах 32 и 40.

При этГом триггер 30 в силу физических свойств устанавливается в одно из двух состояний, нулевое или единичное, что разрешает работу с устрой

ством первой или второй ЦВМ соответственно. Работа с другой ЦВМ будет разрешена после выставления ответного сигнала первой. Таким образом, задержка на обслуживание обращения другой ЦВМ определяется временем сра- батьюания устройства, которое при исользовании элементов ОЗУ с высоким быстродействием весьма мало, и другой ЭВМ эта задержка практически не ощущается.

Снятие сигнала с выхода элемента ИЛИ 37 или 45 приводит .-. увеличению числа, хранимого в счетчике 10 или 11 соответственно, на единицу, что позволяет при занесении или считывании массивов информации заносить в начальный адрес массива и в дальнейшем, не снимая запросного сигнала, производить запись/чтение, не повторяя первого, адресного, такта.

Формула изоёретения

Устройство для сопряжения двух ЦВМ с общей памятью, содержащее с первого по шестой блоки элементов И, первый, второй блоки элементов ИЛИ, первый, второй счетчики, с первого по четвертый элементы И и с первого по четвертый элементы ИЛИ, отличающееся тем, что, с целью повышения быстродействия, в него введены первый, второй элементы задержки, седьмой, восьмой блоки элементов И, первый, второй регистры, пятый, шестой элементы ИЛИ, с пятого по восьмой элементы И и с первого по тре ,тий триггеры, причем первьм, второй входы и выход первого блока элемен- тов ИЛИ соединены соответственно-с выходами первого, второго блоков элементов И и с вькодом устройства для подключения информационного -входа общей памяти, первый, второй входы и выход второго блока элементов ИЛИ соединены соответственно с выходами третьего, четвертого блоков элементов И и с выходом устройства ддтя подключения адресного входа общей памяти, пер вые входы первого и пятого блоков элементов И являются входом устройства ,1ЩЯ подключения информационного выхода первой ЦВМ, первые входы второго и шестого блоков элементов И являются входом устройства для подключения информационного выхода второй ЦВМ, информационные входы первого, второго рёгулятйров являются входом устройства для подключения информационного выхода общей памяти, выходы первого, второго регистров соединены с первыми входами соответственно седьмого, восьмого блоков элементов И, выходы седьмого, восьмого блоков элементов И соединены соответственно с выходами устройства для подключения инфор- маи;ионных входов первой, второй ЦВМ, выходы пятого, тестОго блоков элемен

g О

5

0 30 35 404550 55

тов И соединены с информационными входами соответственно первого, второго счетчиковр выходы первого, второго счетчиков соединены с первьми входами соответственно третьего, четвертого блоков элементов И, первые входа первого, второго элементов И являются соответственно входами устройства для подключения выходов записи и чтения первой ЦВМ, первые входы третьего, четвертого элементов И являются соответственно входами устройства для подключения выходов записи и чтения второй ЦВМ, выходы первого,второго элементов ИЛИ являются 1зыходами устройства для подключения входов чтения и записи общей памяти соответственно, выход первого элемента И соединен с первыми входами первого и третьего элементов ИЛИ, выход второго элемента И соединен .с первым входом второго элемента ИЛИ и с вторым входом третьего элемента . ИЛИ, выход третьего элемента И соединен с вторым входом первого элемента Т-ШИ, второй вход седьмого блока элементов И и первый вход четвертого элемента ИЛИ являются входом устройства для подключения выхода чтения первой ЦВМ, второй вход пятого блока элементов И и первый вход пятого элемента И являются входом устройства для подключения выхода запроса первой ЦВМ, третий вход пятого блока элементов И и второй вход четвертого элемента ИЛИ являются входом устройства для подключения выхода записи первой ЦВМ, выход третьего элемента ИЛИ соединен со счетным входом первого счет чика и через первый элемент задержки с первым входом шестого элемента И и с входом синхронизации первого регистра, выходы пятого и седьмого элементов И соединены соответственно с единичным и нулевым входами первого триггера, единичный выход которого соединен с вторыми входами первого, второго элементов И и пе рвого, третьего блоков элементов И, нулевой выход первого триггера.соединен с вторьми входами третьего, четвертого элемен тов И и второго, четвертого блоков элементов И, выход третьего элемента И соединен с первым входом пятого элемента ИЛИ, второй вход которого и второй вход второго элемента ИЛИ соединены с выходом четвертого элемента И, второй вход восьмого блока

элементов И и первый вход шестого элемента ИЛИ являются входом устройства для подключения выхода чтения второй ЦВМ, второй вход шестого элемента ИЛИ и второй вход шестого блока элементов И являются входом устройства для подключения выхода записи второй ЦВМ, третий вход шестого блока элементов И и первьй вход седьмого ю го элемента ИЛИ соединен с вторым

гаестого элемента И и с единичным входом второго триггера, нулевые вход и выход которого соединены соответственно с выходом шестого элемента И и с вторым входом пятого элемента И, единичный выход второго триггера является выходом устройства для подключения входа ответа первой ЦВМ, выход шесто

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух ЦВМ с общей памятью | 1989 |

|

SU1661778A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1621038A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1221666A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1986 |

|

SU1348844A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1705832A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1982 |

|

SU1053119A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к вычислительной технике и может быть использовано в многомапганных вычислительных системах, работающих в реальном масштабе времени. Целью изобретения является повышение быстродейст ВИЯ устройства за счет разделения одновременного доступа обеих ЦВМ к общей памяти. Устройство содержит первый, второй блоки элементов И 12, первый, второй блоки элементов ИЛИ 5, 7, третий, четвертый блоки элементов И 8, 9, первый, второй счетчики 10, 11, пятый, шестой блоки элементов И 12, 13, первый, второй регистры 14, 15, седьмой, восьмой блоки элементов И 16, 17, первый, второй элементы ИЛИ 20, .1, первый-четвертый элементы И 22-23, первый триггер 30, пятый элемент И 31, второй триггер 33, шестой элемент И 35, первый элемент задержки 36, третий, четвертый элементы ИЛИ 37, 38, седьмой элемент И 39, третий триггер 41, восьмой элемент И 43, второй элемент задержки 44, пятый, шестой элементы ИЛИ 45, 46. Устройство обес- печ};вает равноприоритетное обращение двух ЦВМ к общим ресурсам памяти, разрешая такое обращение в любой момент времени. 1 ил. с $ (Л с

Элемента И являются входом устройства для подключения выхода запроса второй ЦВМ, выход пятого элемента ИЛИ соединен со счетным входом второго счетчика и через второй элемент задержки с первым входом восьмого элемента И и с входом синхронизации второго регистра, выход четвертого элемента ИЛИ соединен с вторым входом

входом восьмого элемента И и с единичным входом третьего триггера,нулевые вход и выход которого соединены соответственно с выходом восьмого элемен- та И и с вторым входом седьмого элемента И, единичный выход третьего триггера соединен с выходом устройства для подключения входа ответа второй ЦВМ.

Авторы

Даты

1988-05-30—Публикация

1986-12-29—Подача