Изобретение относится к вычислительной технике и может быть использовано при построении многомашинных систем, работающих в реальном масштабе времени.

Целью изобретения является повышение быстродействия устройства.

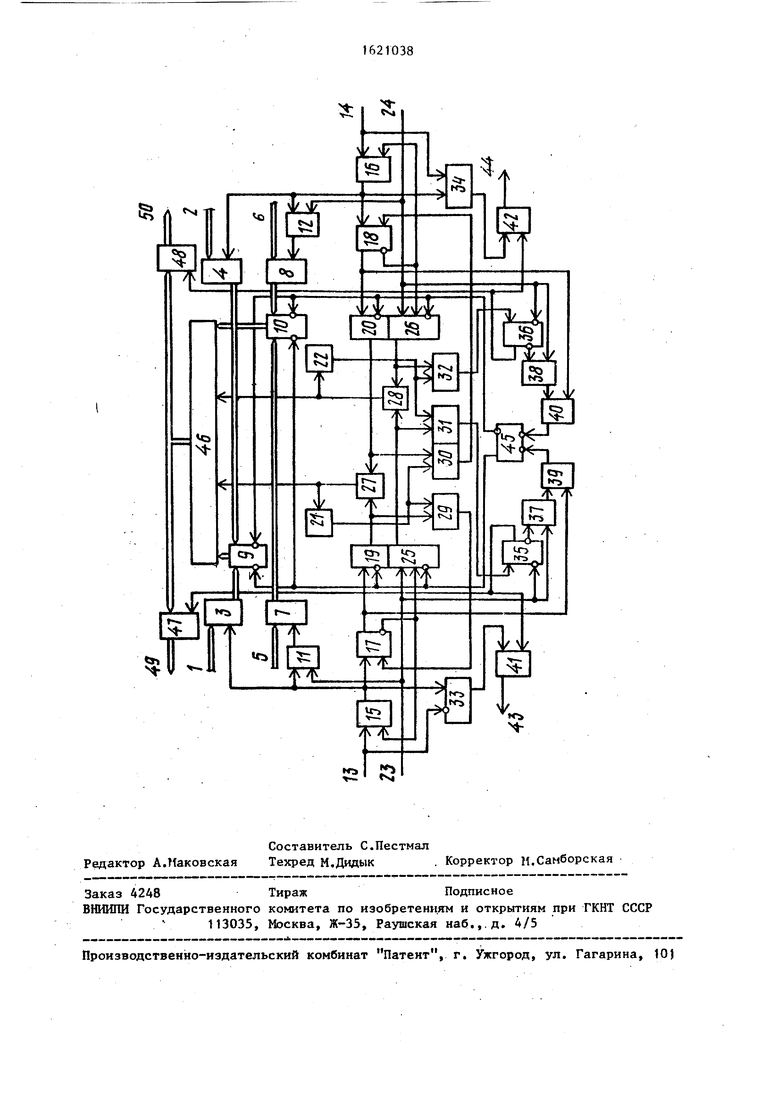

На чертеже представлена схема устройства.

Устройство содержит информационные входы 1, 2, регистры 3,4 входных данных, адресные входы 5, 6, регистры 7, 8 адреса, коммутаторы 9, 10, элементы ИЛИ 11, 12, входы 13, 14 записи, элементы И 15, 16, триггеры 17, 18, элементы И 19, 20, элементы 21, 22 задержки входы 23, 24. чтения, элементы И 25, 26, элементы ИЛИ 27, 28, элементы И 29-32, триггеры 33-36, элементы II 37, 38, элементы ИЛИ 39-42, выходы 43, 44 ответа, триггер 45, блок 46 памяти,- регистры 47, 48 выходных данных, информационные выходы 49f 50.

Устройство работает следующим образом.

В зависимости от обращений ЭВМ устройство имеет несколько режимов работы.

Режим обращения одной ЭВМ.

В начальный момент времени триггеры 17, 18, 33-36 находятся в нулевом состоянии, на единичный и нулевой входы триггера 45 поданы логические О, а на обоих его выходах присутствуют 1. Эти сигналы запрещают обмен информацией как с первой, так и со второй ЭВМ.

Предположим, осуществляется операция Запись со стороны первой ЭВМ. При этом на вход 1 помещаются данные , а на вход 5 - адрес, сигнал Запись на входе 13 взводит триггеры 17 и 33 и подается в регистры 3 и 7, в которых фиксируются данные и адрес соответственно. Сигнал с выхода триггера 33 через элемент ИЛИ 41 поступает на выход 43 Ответ. При его по-

(Л

с

с& оэ

со

0&

явлении ЭВМ снимает сигналы данных, адреса и записи, при этом триггер 33 сбрасывается и снимает сигнал Ответ с выхода 43. На этом участие ЭВМ в операции записи заканчивается. Дальнейшая передача информации в блок 46 памяти осуществляется под управлением данного устройства следующим образом,

Сигнал с нулевого выхода триггера 17 запрещает повторную запись и чтение до того момента, пока данные, зафиксированные в регистре 3, не будут записаны в блок 46 памяти. Сиг- нал с единичного выхода триггера 17 через элемент ИЛИ 39 поступает на нулевой вход триггера 45.При этом триггер 45 сбрасывается и на его единичном выходе устанавливается сиг- нал разрешения передачи данных, адреса и сигнала Запись в блок 46 па- мяти. При появлении сигнала записи 1на выходе элемента ИЛИ 27 элемент 21 задержки через время, достаточное для окончания процессов установления в блоке 46 памяти, формирует импульс, который передается на выход элемента И 29 и сбрасывает триггер 17. При этом на выходе элемента ИЛИ.39 появ- ляется низкий уровень и триггер 45 устанавливает на своих выходах высокие уровни, запрещая передачу информации.

При операции чтения сигнал Чте- ние поступает на вход 23 и через элемент ИЛИ 11 фиксирует в регистре 7 адрес , подаваемый на вход 5. Сигнал Чтение проходит через элемент II 37, на другом входе которого присутству- ет высокий уровень, и через элемент ИЛИ 39 поступает на нулевой вход триггера 45, который при этом сбрасывается. На его единичном выходе устанавливается низкий уровень, которым разрешается передача адреса и .сигнала чтения. При появлении сигнала чтения на выходе элемента ИЛИ 28 эле- мент 22 задержки через время, достаточное для окончания процессов уста- новления в блоке 46 памяти, формирует импульс, который передается на выход элемента И 31 и устанавливает триггер 35, при этом в регистре 47 фиксируются данные с выхода

блока 46 памяти и на выходе 43 появ ляется сигнал,Ответ. Кроме того, низкий логический уровень с нулевого выхода триггера 35 через элемент

jg

15 2Q 25 0

с Q

55

И 37 и элемент ИЛИ 39 поступает на нулевой вход триггера 45. Устройство готово к следующему циклу обмена с второй ЭВМ.

После появления сигнала Ответ на выходе 43 ЭВМ снимает сигнал Чтение с входа 23 и триггер 35 сбрасывается. После этого устройство готово к следующему циклу обмена как с первой, так и с второй ЭВМ.

Анапогично осуществляются операции Чтение, Запись при обращении второй ЭВМ.

Режим одновременного обращения двух ЭВМ.

В начальный момент времени на выходах триггера 45 присутствуют высокие уровни и ни от одной ЭВМ не может быть о.бращения к блоку 46 памяти. При одновременном обращении на единичном и нулевом входах триггера 45 появляются высокие уровни, но триггер в силу своих свойств переключается в одно из двух возможных состояний.Допустим для определенности, что на нулевом выходе триггера 45 присутствует низкий логический уровень. При этом коммутаторы 9 и 10 открываются со стороны второй ЭВМ, которая производит цикл обмена информацией.

Если первая ЭВМ при этом пытается записать информацию, то она устанавливает данные на входе 1, адрес - на входе 5, подает сигнал Запись на вход 13. Поскольку триггер 17 сброшен, то на втором входе элемента И 15 присутствует высокий логический уровень, и поэтому на его выходе появится сигнал Запись, которым записываются данные и адрес в регистры 3 и 7, а также взводятся триггеры 17 и 33, с выхода последнего через элемент ИЛИ 41 на выход 43 устройства поступает сигнал Ответ. При его появлении первая ЭВМ снимает сигналы данных, адреса и записи, при этом триггер 33 сбрасывается и снимает сигнал Ответ с выхода 43. Цикл записи закончен. На выходе элемента ИЛИ 39 присутствует высокий логический уровень, что свидетельствует о запросе со стороны первой ЭВМ.

Koi да вторая ЭВМ закончит цикл обмена и сбросит триггер 18 или 36, на выходе элемента ИЛИ 40 появится низкий уровень. При этом на единичном выходе триггера 45 появится низкий логический уровень, который от51

кроет коммутаторы 9 и 10 со стороны первой ЭВМ, а также элемент И 19, на выходе которого появится сигнап записи, которым по адресу в регистре 7 запишутся данные из регистра 3 в блок 46 памяти. Сигналом записи элемент 21 задержки через время, достаточное для записи в блок 46 памяти, через открыты элемент И 29 подает сигнал сброса на триггер 17. После этого на выходе элемента ИЛИ 39 появится низкий логический уровень. Устройство возвращается в исходное состояние.

Теперь рассмотрим операцию Чтение первой ЭВМ при одновременном обращении.

Первая ЭВМ устанавливает адрес на входе 5 н сигнал Чтение на вход 23, при этом в регистр 7 адреса записывается адрес, на выходе элемента И 37 устанавливается высокий логический уровень, который через элемент ИЛИ 39 поступает на нулевой вход триггера 45.

Когда вторая ЭВМ закончит цикл обмена, на выходе элемента ИЛИ 40 по - явится низкий уровень. При этом на единичном выходе триггера 45 появится низкий уровень, который откроет коммутаторы 9 и 10 со стороны первой ЭВМ, а также элемент И 25, если закончен цикл записи. lid выходе элемента И 25 возникает сигнал, которым по адресу, записанному в регистр 7, извлекаются данные из блока 46 памяти. Сигналом чтения элемент 22 та- держки через время установления данных на выходе блока 46 памяти формирует импульс на выходе открытого элемента И 31, которым взводится тригге 35. Сигналом с единичного выхода тригера 35 данные из блока 46 памяти фиксируются в регистра 47. Этот же сигнал через элемент ИЛИ 41 поступает на выход устройства 43 Ответ. Сигнал с нулевого выхода триггера 35 устанавливает на выходе элемента Н 37 низкий логический уровень, который через элемент ИЛИ 39 поступает на нулевой вход триггера 45. После этого устройство доступно со стороны второй ЭБМ.

По сигналу Ответ с выхода 43 первая ЭВМ снимает сигнал Чтение, после этого сбрасывается триггер 35 и снимается сигнал Ответ. Теперь

386

возможен следующий щп:п обмена информацией с любой из ЭВМ.

Формула изобретения

-Устройство для сопряжения двух ЭВМ, содержащее два регистра выход - ных данных, три триггера, восемь элеQ ментов И, шесть элементов ИЛИ, два элемента задержки, причем информационные выходы первого и второго регистров выходных данных являются выходами устройства для подключения соот«J ветственио к информационным входам первой и второй ЭВМ, отличающееся тем, что, с целью повышения быстродействия, в устройство введены блок памяти, два регистра

0 входных данных, два регистра адреса, четыре триггера, два коммутатора,четыре элемента И, два элемента ИЛИ, причем информационные входы первого и второго регистров входных данных

5 являются входами устройства для подключения соответственно к информационным выходам первой и второй ЭВМ, информационные входы первого и второго регистров адреса являются входа0 ми устройства для подключения соответственно к адресным ьыходам первой н второй ВМ, первый вход первого элемента И, соединенный с нулевым входом первого триггера, является входом устройства дггя. подключения к выходу записи первой ЭВМ, первый вход первого элемента ИЛИ, соединенный с первыми входами второго, третьего элементов Н, с нулевым входом

Q второго триггера, является входом устройства .ryin подлкючения к выходу чтения нерпой ЭВМ, первый вход четвертого элемента Н, соединенный с нулевым входом третьего триггера, яве ляетгя входом устройства для подключения к выходу тяписи второй ЭВМ, первый вход второго элемента ИЛИ, соединенный с перинми входами пятого, шестого элементов И, с нулевым ихо0 Д°м отпертого триггера, является входом устройства для подключения к выходу чтения второй ЭВМ, выходы третьего и четвертого -пементоп ИЛИ являются выходами устройства для подключения соответственно к входам ответа первой и в горой ЭВМ, при этом информационные входы первого и второго регистров выходных данных: соединены с информационном выходом блока па5

5

F

мяти, информационный и адресный входы которого соединены соответственно с выходами первого и второго коммутаторов,перцые и вторые информационные входы которых соединены соответственно с информационными выходами первого и второго регистров вход- jiibix данных и первого и второго реги- |стрсв адреса, выход первого элемен- а И соединен с входом записи первого регистра входных данных, с вторым входом первого элемента ГОШ, с единичным входом пятого триггера, с единичным входом первого триггера, единичный выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с входом записи первого регистра выходных ДаННЫХ И С еДИНИЧНЫМ ВЫХОДОМ ВТО

рого триггера, нулевой выход которого соединен с вторым входом третьего элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, выход которого соединен с нуле- вым входом шестого триггера, единичный выход которого соединен с первыми управляющими входами первого,второго коммутаторов, с первым входом седьмого элемен 1 а И и с вторым входо второго элемента И, третий вход которого соединен с вторым входом первого элемента И и с нулевым выходом пятого триггера, нулевой вход которого соединен с выходом восьмого элемента И, первый вход которого соединен с первым входом шестого элемента ИЛИ и с выходом седьмого элемента И, второй вход которого соединен с единичным выходом пятого триггера и с вторым входом птяого элемента ИЛИ, выход первого элемента ИЛИ соединен с входом записи первого регистра адреса, выход второго элемента И соединен с первым входом седьмого элемента ИЛИ и с первым входом девятого элемента II, второй вход которого соединен с первым входом десятого элемента И и с выходом первого элемента задержки,вход которого соединен с

п

5 о

выходом седьмого элемента ИЛИ и с входом чтения блока памяти, вход записи которого соединен с выходом шестого элемента ИЛИ и с входом второго элемента задержки, выход которого соединен с вторым входом восьмого элемента И и с первым входом одиннадцатого элемента И, второй вход которого соединен с вторым входом шестого элемента ИЛИ и с выходом двенадцатого элемента И, первый вход которого соединен с вторыми управляющими входами первого, второго ком- мутаторов, с нулевым выходом шестого триггера и с вторым входом пятого элемента И, третий вход которого соединен с нулевым выходом седьмого триггера и с вторым входом четвертого элемента И, выход которого соединен с входом записи второго регистра входных данных, с вторым входом второго элемента ИЛИ, с единичным входом третьего триггера, с единичным входом седьмого триггера, единичный выход которого соединен с вторым входом двенадцатого элемента И и с первым входом восьмого элемента ИЛИ, выход которого соединен с единичным входом шестого триггера, второй вход восьмого элемента ИЛИ соединен с выходом шестого элемента И, второй вход которого соединен с нулевым выходом четвертого триггера, единичный выход которого соединен с входом записи второго регистра выходных данных и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с единичным выходом третьего триггера, выходы девятого, десятого и одиннадцатого элементов И соединены соответственно с единичными входами второго, четвертого триггеров и с нулевым входом седьмого триггера, выход пятого элемента И соединен с вторыми входами седьмого элемента ИЛИ и десятого элемента И, выход второго элемента ИЛИ соединен с входом записи второго регистра адреса.

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух ЦВМ с общей памятью | 1986 |

|

SU1399750A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для управления обменом информацией | 1987 |

|

SU1513460A1 |

| Устройство для сопряжения интерфейсов ЭВМ и внешней памяти | 1984 |

|

SU1262509A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении многомашинных систем, работающих в реальном масш- табе времени. Целью изобретения является повышение быстродействия. Устройство содержит блок памяти, два коммутатора, два регистра входных данных, два регистра выходных данных, два регистра адреса, семь триггеров, два элемента задержки, двенадцать элементов И, восемь элементов ИЛИ. 1 ил.

| Двухпортовое устройство сопряжения в вычислительной системе | 1982 |

|

SU1156080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух ЦВМ с общей памятью | 1986 |

|

SU1399750A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-15—Публикация

1989-01-04—Подача