4 О5 О1

Изобретение относится к вычислительной технике и может быть использовано в аппаратных и гибридных мониторах для регистрации хода программ.

Целью изобретения является повышение быстродействия.

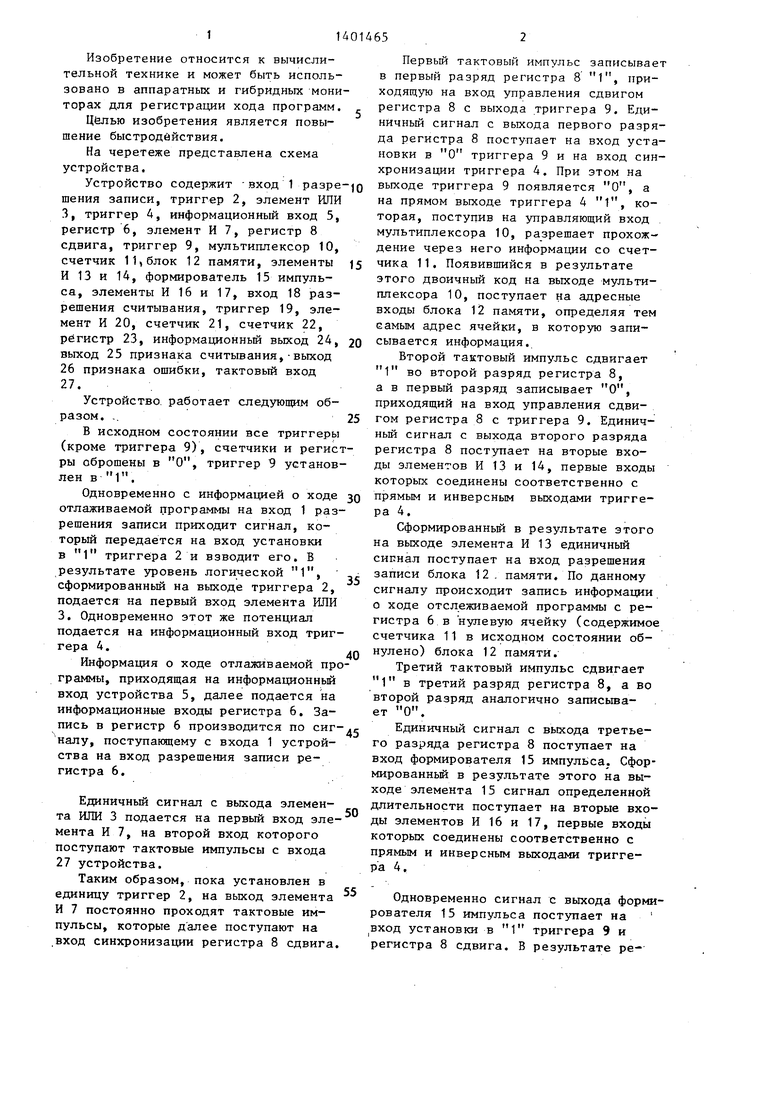

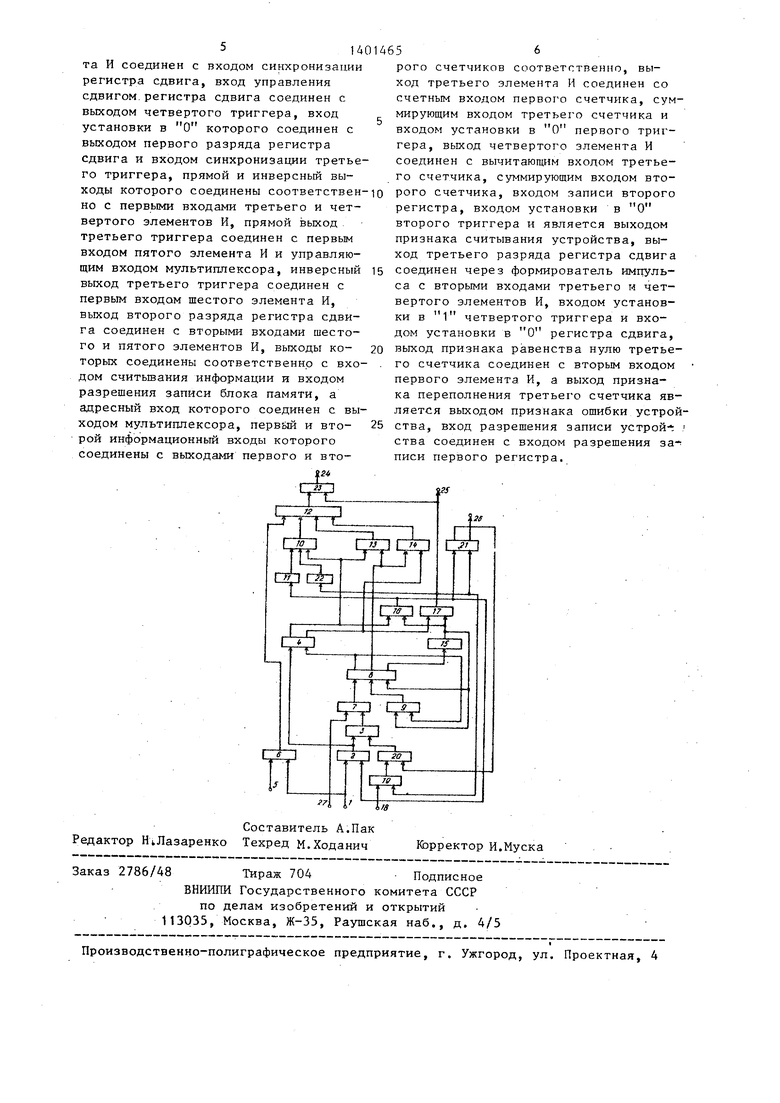

На черетеже представлена схема устройства.

Устройство содержит -вход 1 paspe шения записи, триггер 2, элемент ИЛИ 3, триггер 4, информационный вход 5, регистр 6, элемент И 7, регистр 8 сдвига, триггер 9, мультиплексор 10, счетчик 11,блок 12 памяти, элементы И 13 и 14, формирователь 15 импульса, элементы И 16 и 17, вход 18 разрешения считывания, триггер 19, элемент И 20, счетчик 21, счетчик 22, регистр 23, информационный выход 24, выход 25 признака считывания,-выход

26признака ошибки, тактовый вход 27.

Устройство, работает следующим образом. -.

В исходном состоянии все триггеры (кроме триггера 9), счетчики и регисры сброшены в О, триггер 9 установлен в 1.

Одновременно с информацией о ходе отлаживаемой программы на вход 1 разрешения записи приходит сигнал, который передается на вход установки в 1 триггера 2 и взводит его. В результате уровень логической 1, сформированный на выходе триггера 2, подается на первый вход элемента ИЛИ 3. Одновременно этот же потенциал подается на информационный вход триггера 4.

Информация о ходе отлаживаемой прграммы, приходящая на информационньй вход устройства 5, далее подается на информационные входы регистра 6, Запись в регистр 6 производится по сиг налу, поступаклцему с входа 1 устройства на вход разрешения записи регистра 6.

Единичньй сигнал с выхода элемента ИЛИ 3 подается на первый вход эле мента И 7, на второй вход которого поступают тактовые импульсы с входа

27устройства.

Таким образом, пока установлен в единицу триггер 2, на выход элемента И 7 постоянно проходят тактовые импульсы, которые далее поступают на .вход синхронизации регистра 8 сдвига

Первый тактовый импульс записывае Б первый разряд регистра В 1, приходящую на вход управления сдвигом регистра 8 с выхода триггера 9. Единичный сигнал с выхода первого разряда регистра 8 поступает на вход установки в О триггера 9 и на вход синхронизации триггера 4. При этом на вьрсоде триггера 9 появляется О, а на прямом выходе триггера 4 1, которая, поступив на управляющий вход мультиплексора 10, разрешает прохождение через него информации со счетчика 11. Появившийся в результате этого двоичный код на выходе мультиплексора 10, поступает на адресные входы блока 12 памяти, определяя тем самым адрес ячейки, в которую записывается информация.

Второй тактовый импульс сдвигает 1 во второй разряд регистра 8, а в первый разряд записывает О, приходящий на вход управления сдвигом регистра 8 с триггера 9. Единичньй сигнал с выхода второго разряда регистра 8 поступает на вторые входы элементов И 13 и 14, первые входы которых соединены соответственно с прямым и инверсным выходами триггера 4.

Сформированньй в результате этого на выходе элемента И 13 единичный сигнал поступает на вход разрешения записи блока 12. памяти. По данному сигналу происходит запись информации о ходе отслеживаемой программы с регистра 6 в нулевую ячейку (содержимо счетчика 11 в исходном состоянии обнулено) блока 12 памяти.

Третий тактовый импульс сдвигает 1 в третий разряд регистра 8, а во второй разряд аналогично записыва- ет О.

Единичный сигнал с выхода третьего разряда регистра 8 поступает на вход формирователя 15 импульса. Сформированньй в результате этого на выходе элемента 15 сигнал определенной длительности поступает на вторые входы элементов И 16 и 17, первые входы которых соединены соответственно с прямым и инверсным выходами триггера 4.

Одновременно сигнал с выхода формрователя 15 импульса поступает на вход установки в 1 триггера 9 и регистра 8 сдвига. В результате ре 1401465

г истр 8 обнуляется, а триггер 9 уста- с выхода элемента И 17, производится навливается в единичное состояние. запись информации в регистр 23, выНа выходе элемента И 16 вьграбаты- ход которого соединен с информацион- вается единичный сигнал, который, по- ступая на сченый вход счетчика 11, увеличивает его содержимое на единицу, таким образом происходит переадресация блока памяти.

Одновременно импульс с выхода эле-ю выхода элемента И 17 одновременно мента И 16 поступает на вход установ- поступает на выход признака считы- ки в О триггера 2 и сбрасывает его, вания устройства и на вход установки в результате регистр 8 блокируется.

Процесс считывания информации из блока памяти начинается с момента по-15 ячеек блока 12 памяти. С выхода эле- явления на входе 18 сигнала разреше- мента И 16 при записи в ячейку или с

выхода элемента И 17 при считывании сформированные импульсы подаются соным выходом 24 устройства.

Переадресация блока памяти производится импульсом, сформированным на. выходе элемента И 17 и поступающим на вход +1 счетчика 22. Сигнал с

в О триггера 19, сбрасывая его. Счетчик 21 определяет заполнение

ния считьшания, который поступает на вход установки в 1 триггера 19 и взводит его. Сигнал, сформированный на выходе триггера 19, поступает 20 счетчика 21, изменяя его содержимое. на первый вход элемента И 20, на вто- В случае заполнения всех ячеек накоответственно на входы ЧГ или -1

пителя (переполнение счетчика 21) сигнал Ошибка с выхода переполнения подается на выход 26 признака 25 ошибки устройства.

рой вход которого заводится сигнал с выхода О счетчика 21.

Сигнал на выходе элемента И 20 появляется лишь в том случае, если в блоке памяти заполнена хотя бы одна ячейка.

Сигнал с выхода элемента И 20 поступает на вход элемента ИЛИ 3. Сформированньм в результате этого на выходе элемента ИЛИ 3 единичный сигнал, поступая на первый вход элемента И 7, разрешает прохождение через него тактовой частоты, поступающей на второй вход элемента И 7.

Аналогично процессу записи происходит запуск и работа регистра В сдвига.

По поступлении на вход синхронизации триггера 4 единичного сигнала с первого выхода первого разряда регистра 8 сдвига, на прямом выходе триггера 4 устанавливается. О, на инверсном - 1. В результате этого на управляющем входе мультиплексора 10 присутствует управляющий сигнал, разрешающий прохождение на адресные входы блока 12 памяти кода со счетчика 22.

В следующий момент времени после формирования единичного импульса на выходе второго разряда регистра сдвига, на выходе элемента И 14 вырабатывается единичньй сигнал, по коход которого соединен с информацион-

ным выходом 24 устройства.

Переадресация блока памяти производится импульсом, сформированным на. выходе элемента И 17 и поступающим на вход +1 счетчика 22. Сигнал с

выхода элемента И 17 одновременно поступает на выход признака считы- вания устройства и на вход установки

ячеек блока 12 памяти. С выхода эле- мента И 16 при записи в ячейку или с

в О триггера 19, сбрасывая его. Счетчик 21 определяет заполнение

счетчика 21, изменяя его содержимое. В случае заполнения всех ячеек накоответственно на входы ЧГ или -1

0 счетчика 21, изменяя его содержимое. В случае заполнения всех ячеек накопителя (переполнение счетчика 21) сигнал Ошибка с выхода переполнения подается на выход 26 признака 5 ошибки устройства.

Формула изобретения

Устройство управления памятью, содержащее два регистра, три счетчи0 ка, блок памяти, два элемента И, элемент ИЛИ, причем информационные входы первого регистра являются информационными входами устройства, выход первого регистра соединен с инфор- мационным входом блока памяти, информационный выход которого соединен с информационным входом второго регистра, выход которого является информационным выходом устройства, о т дличающееся тем, что, с целью повьш1ения быстродействия, в него введены четыре триггерау с третьего по шестой элементы И, регистр сдвига,- мультиплексор, формирователь

5 импульса, причем входы установки в 1 первого и второго триггеров являются соответственно входом разрешения записи и входом разрешения считывания устройства, выход первого триггера соединен с первым входом элемента ИЛИ и информационным входом третьего триггера, выход второго триггера соединен с первым входом первого элемента И, выход которого соединен

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1984 |

|

SU1265776A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Анализатор спектра Фурье | 1987 |

|

SU1387010A1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2109399C1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1520521A1 |

Изобретение относится к вычислительной технике и может быть использовано в аппаратных и гибридных мониторах для регистрации хода программ. Целью изобретения является повышение быстродействия. ,Дпя этого в уст. ройство, содержащее два регистра, блок памяти, три счетчика, элемент ИЛИ, два элемента И, дополнительно введены четыре регистра, формирователь импульса, четыре элемента И, регистр сдвига, мультиплексор. Устройство не требует на время считывания информации блокировки записи. Пословное считывание информации из блока памяти производится в паузах между циклами записи. 1 ил.

торому происходит считывание информа- gg с вторым входом элемента ИЛИ, выход ции из блока 12 памяти. Считанная ни- которого соединен с первым входом формация поступает на информационный второго элемента И, вход регистра 23. По сигналу, поступающему на вход записи регистра 23

второго элемента И, второй вход которого является тактовым входом устройства, выход второго элемеь

с вторым входом элемента ИЛИ, выход которого соединен с первым входом второго элемента И,

второго элемента И, второй вход которого является тактовым входом устройства, выход второго элемеьразрешения заходом мультиплексора, первый и вто- 25 ства, вход разрешения записи устрой рой информационный входы которого соединены с выходами первого и втоJ

те.ства соединен с входом писи первого регистра.

разрешения заства, вход разрешения записи устрой

ства соединен с входом писи первого регистра.

| Буферное запоминающее устройство | 1981 |

|

SU993333A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Буферное запоминающее устройство | 1972 |

|

SU506909A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-07—Публикация

1986-12-05—Подача