(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1979 |

|

SU851491A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1226530A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для управления накопителем на запоминающих элементах с неразрушающим считыванием информации | 1976 |

|

SU643973A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Устройство для ввода информации | 1983 |

|

SU1113793A1 |

| Устройство для анализа формы непереодических импульсных сигналов | 1980 |

|

SU890272A1 |

| Буферное запоминающее устройство | 1977 |

|

SU720507A1 |

| Логическое запоминающее устройтво | 1979 |

|

SU858104A1 |

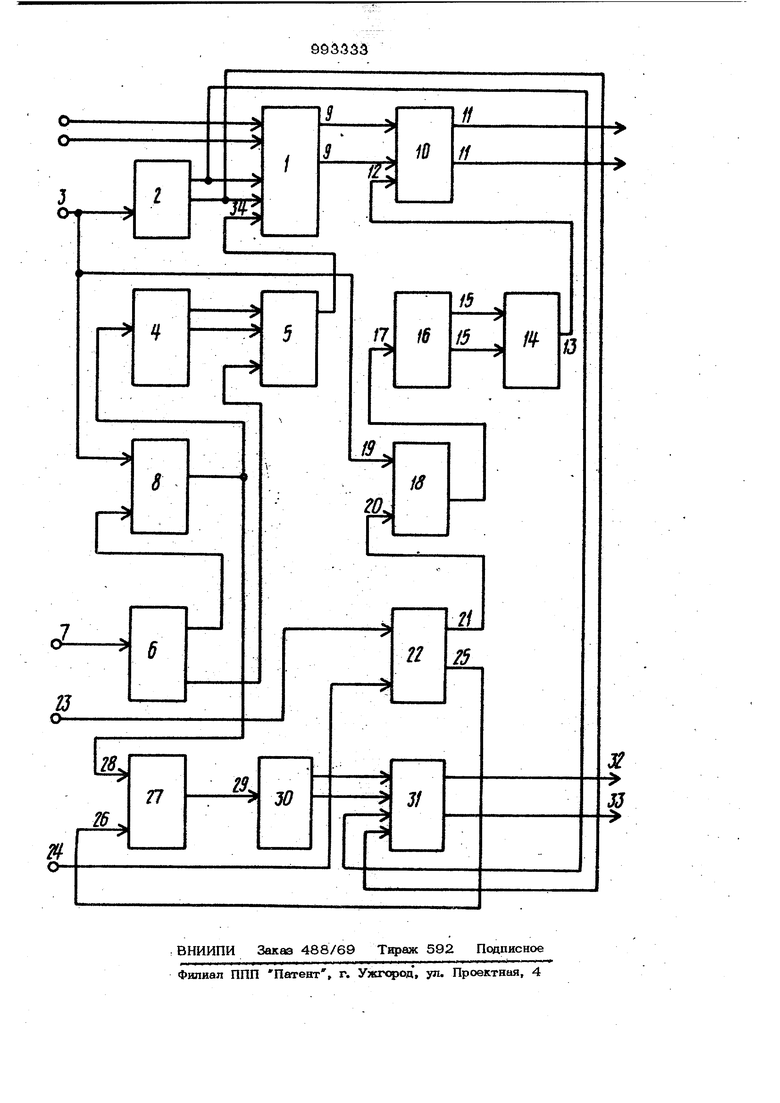

Изобретение отнсхзится к вычислительной технике и может быть использовано в телеграфной сиппаратуре, системах связи, системах отображения, передачи и обработки дискретной инфорв ации. Известно устройство для управления накопителями, предназначенное для заготовки пифро-буквенной информации, содержащее полупроводниковый накопитель, непрерьтно работающий адресный счетчик считьтания, регистр записи и бпок сравнения кодов регистра адреса записи и адресного счетчика считывания, выходы которого соединены с наксжителем Г Наиболее близким к предлагаемому по технической сущности является запоминающее устройство, содержащее накопитель, адресный счетчик, подключенный к накопителю, счетчик записи, элементы И и ИЛИ, тактовые и установочные шины и формирователь. Это устройство предназначено для записи, хранения, коррекции и считывания дифро-буквенной информации. Адресация накопителя при записи и считывании инфорв ации осуществляется за счет изменения момента выработки сигнала записи или с гатывания под воздействием соответствукшгах сигналов управления 21. Недостатком известного устройства являются ограниченные функциональные возмояоюсти устройства ввиду отсутствия возможности одновременной записи и считывания информации, кроме того, УРсутствует возможность определения состояния накопителя, т.е. его полногчэ за полнения шга отсутствия информации в нем. Это ограничивает область применения ЗУ данного типа, исключает возможность его использования в качестве приемного ЗУ. Цель изобретения - расщирение фу1П&циональных возможностей устройства за счет одновременной записи и считывании информации. Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее накопитель, адресные входы 3Йй кото1юго подключены к выходам первого счетчика, управляющий вход накопител подключен к вькоду первого элемента И, один вход которого подключен к первому выходу формирователя импульсов записи, другие входы первого элемента И подклю чены к выходам второго счетчика, вход которого подключен к выходу второго эле мента И, один вход которого подключен к входу первого счетчика и является пер вым входом устройства, другой вход второгч5 элемента И подключен к второму выходу фopмtфoвaтeля импульс овзаписи, вход которого является вторым входом устройства, дополнительно введены тре- тий и четвертый счетчики, дешифратор, формирователь сигналов считьтания, элементы И, элемент ИЛИ и регистр, информационные входы которого подключены к выходам накопителя, управляющий вход регистра подключен к выходу третьего элемента И, входы которого подключены к выходам третьего счетчика, вход третьего счетчика подключен к выходу четвертого элемента И, один из входов которого подключен к входу первого счет чика, другой вход четвертого элемента И подключен к одному из выходов формирователя импульсов считывания, другой выход которого подключен к одному из входов елемента ИЛИ, входы формирователя импульсов считьтания являются соответ ств г ощими входами устройства, другой вход элемента ИЛИ подключен к выходу второго элемента И, выход элемента ИЛИ подключен к входу четвертого снетчика, выходы которого подключены к одним из входов дешифратора, другие входы дешифратора подключены к выходам пер-вого счетчика, выходы дешифратора являются выходами устройства. Такое построение устройства позволяет следить за порядком заполнения накопителя и сигнализировать об отсутот вии в накопителе инфор лащш либо о его по ном заполнении, кроме того, появляется во можность производить считывание в произвольные моменты времени относительно записи и одновременно с записью, что .значительно расширяет функциональные возможности устройства. На чертеже изображена структурная схема предлагаемого устройства. Устройство содержит накопитель 1, первый счетчик 2, вход 3 первого такта, первьй счетчик 4 (записи), первый элемент И 5, формирователь 6 импульсов за писи, вход 7 записи, элемент И 8, информационные выходы 9 накопителя 1 . подключены к входам perucriia .Ю, выходы 11, управляющий вход 12, соединенный с выходом 13 элемента И 14, выходы 15 третьего счетчика 16, тактовый вход 17 счетчика 16, элемент И 18 с входами 19 и 2О, выход 21 формирователя 22 сигналов считывания, вход 23 второго такта, вход 24 сигналов считьюания, выход 25 формирователя 22, вход 26 элемента ИЛИ 27, вход 28 элемента ИЛИ 27, тактовый вход 29 четвертого счетчика 30, выходы разрядо|В которого подключены к соответствующим входам деши4 тора 31, выходы устройства 32 и 33 и вход 34 записи. Устройство работает следующим образом. Перед началом работы все счетчики устройства устшшвливаются в одинаковое фазовое состоящие, соответствующее адресу первой ячейки накопителя ЗУ (первое фазовое состояние), шины начальной установки на чертеже не показаны. Дешифратор счетчика 30, определяющего состояние устройства, при этом вьщает сигнал, свидетельствующий о том, что информация в накопитель не записана. Зтот сигнал запрещает считывание и разрешает запись информацйги в накопитель. При зазтиси информация, сопровождаемая сигналом записи, поступает на информационные входы накопителя (не показано). Сигнал записи по входу 7 поступает 1ш вход формирователя 6, под воздействием которого формируется сигнал, разрешающий работу элемента И 5, на выходу которого появляется сигнал записи (один раз за преиод обращения счетчика 4), поступающий на вход 34 записи накопителя 1. Так как фазовые состояния счетчика 2, являющегося адресным, и счет чика 4, работающего при записи, после воздействия сигнала начальной установки одинаковые и коэффициенты счета их равны, то перв.гй информационный знак записывается по первому адресу. После окончания действия импульса записи по входу 7 формирователь 6 вырабатьгоает одиночный импульс, вычитания, запрещающий Прохождение адрепногч) импульса первого такта через элемент И 8, при этом фаза счетчика 4 и счетгака 30 изменяется на один таг по сравншию с фазой счетчика 2. При пос.тупленшЕ следующего информашгашгого знака, сопровождаемого cигнaлo записи, происходит запись информации по второму адресу к после записи сдвга- на одии шаг фазы сч чпико -1, 5Ш Лальлейшая запись 1пи|юрмации происходит аналогично. После того, как в накопиитель записа хотя бы один знак, можно начинать считывание информации из ЗУ. Считывание производится по независимым от записи шинам. Для этого в схеме предусмотрен счетчик 16, работающий при считьгоании, который перед началом работы, так же как и счетчик 4, устанавливается в ис- ходное фазовое состояние, соответствующее первому адресу накопителя- (первая фаза). Выходы 15 разрядов счетчика 16 соединен с входами элемента И 14, на выходе которого формируется синхроимпульс считывания, соответствующий первой фазе счетчика 16, поступающий на тактовый вход регистра 1О. Под воздействием синхроимпульса считьшания информация с выходов 9 накопителя 1 считывается в регистр и поступает на выходные информационные выходы 11. Первый выведенный информационный знак хранится в выходном регистре до тех пор, пока на тактовый вход 12 регистра 1О не поступит синхроимпульс считывания с выхода элемента И 14. После начальной установки счетчика 16 первое фазовое состояние его совпадает с фазовым состоянием счетчика 2, поэтому в выходной регистр считывается ин формация, записанная по первому адресу накопителя 1. С приходом сигнала считьь вания по входу 24 считьтания на вход формирователя 22 сигналов считывания на выходе 21 последнего формируется од ночный импульс вычитания, запрещающий прохождение одного импульса первого так та через элемент И 18, При этом фаза счетчика 16 отстает на один шаг от фазы адресного счетчика 2, аналогично тому, как это происходит при записи икформации. При этом в выходной регистр считыва ся информационный знак, записанный по второму адресу и т.д. v В процессе всей работы ЗУ состояние накопителя (т.е. отсутствие в нем ннфо1 мацик и его заполнение) контролируется с помощью счетчика ЗО. После воздействия сигнала начальной установки .счетчик 30 устаиавливается в исходное (первое) фазовое состояние, одинаковое с фазовыми состояниями счетчика 4 и счетчика 16. При записи информации в накопитель 1 счетчик ЗО работает синхронно со счетчиком 4, т.е. после записи каждого 1шформационкого знака фаза ; счетшкл ,Ю изменяется одинаково с фа- 336 ЗОЙ счетчика 4, отста1«1я на шаг от фазы адресного счетчика 2. Как только фаза счетчика 30 будет соответствовать адресу последней ячейки накопителя, т.е. сигнал с дешифратора фазы совпадает с (-1) фазой адресного счетчика 2, на выходе 33 дешифратора 31 формируется сигнал, свидетельствующий о заполнении накопителя полностью. При считьшании информации из накопителя счетчик состояния работает таким образом, что с при- ходом каждого сигнала считывания его фаза опережает фазу адресного счетчика. Формирователь считывания при этом формирует одиночный импульс частоты, добавленный к тактовой последовательности на элементе ИЛИ 27. Когда первая фаза счетчикасостояния совпадает с фазой адресного счетчика 2, дешифратор 31 вырабатывает сигнал на выходе 32, свидетельствующий о том, что информации в накопителе нет. Предлагаемое устройство позволяет организовать запись и считывание информации, что расширяет область его приме- 1ения. Кроме того, индикация степени заполнения накопителя дает возможность оперативно определять его полное заполнение и отсутствие в нем инфс змашга. Устройство позволяет использовать накопители большой емкости, необходи- мые например, в приемных запоминающих устройствах электронных телеграфных аппаратов. Формула изобретения Буферное запоминающее устройство, содержащее накопитель, адресные входы которого подключены к выходам первого счетчика, управляющий вход накопителя подключен к выходу первого элемента И, один вход которого подключен к первому выходу формирователя импульсов записи, другие входы первого элемента И подключены к выходам второго счетчика, вход которого подключен к выходу второго элемента И, один вход которого подключен к входу первого счетчика и является первым входом устройства, другой вход второго элемента И подключен к второму выходу формирователя импульсов записи, вход которого является вторьпл входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет. одновременной писк и считывашгя информатга, оно содержит третий и четвертый счетчики, дешифратор, формирователь сигналов считывания, элементы И, элемент ИЛИ я регистр, информадио1шые входы которого подключены к выходам накопителя, управляющий вход регистра подключен к выходу третьего элемента И, входы ко торого подключены к выходам третьего счетчика, вход третьего счетчика подключен в выходу четвертого элемента И, один из входов которого подключен к

входу первого счетчика, другой вход чет вертого элемента И подключен к одному из выходов формирователя импульсов считьшания, другой выход которого тхопключен к одному из входов элемента ИЛИ входы формирователя импульсбв считьшания 5тляются соответствующими входами устройства, другой вход элемента ИЛИ подключен к выходу второго элемента И,

выход элемента ИЛИ подключен к входу четвертого счетчика, выходы которого подключены к одним из входов дешифратора, другие входы дешифратора подключена к выходам первого счетчика, выход дешифратора Являются выходами устройства.

Источники информации, принятые- во внимание при экспертизе

Авторы

Даты

1983-01-30—Публикация

1981-09-03—Подача