О1 QD

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Устройство формирования систем трехкратных производных нелинейных рекуррентных последовательностей | 2022 |

|

RU2792598C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ КОДОВЫХ СЛОВАРЕЙ НЕЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2009 |

|

RU2439657C2 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СИСТЕМ ДВУКРАТНЫХ ПРОИЗВОДНЫХ НЕЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2014 |

|

RU2553057C1 |

| Аналоговый декодер кода с ортогональными проверками | 1986 |

|

SU1401614A1 |

| Декодер кодов Рида-Соломона | 1988 |

|

SU1690202A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| Дельта-кодер | 1985 |

|

SU1290529A1 |

Изобретение относится к вычислительной технике. Его использование в системах передачи дискретной информации позволяет повысить помехоустойчивость. Декодер содержит мультиплксоры 1,2, сдвиговые регистры 3,4 информации и надежностей , блок 5 управления, блок 6 дешифрации, блок 14 выделения максимума и коммутатор 16. Благодаря введению блоков 7,8 дешифрации, сумматоров 9-11 по модулю два, блока 12 дискретных декодоров, блока 13 вычисления степеней сходства и блока 15 регистров в декодере осуществляется исправление всех конфигураций ошибок среди символов с восемью наименьшими надежностями. 4 з.п.ф-лы, 6 ил.

СП Јй

о

Изобретение относится к вычислиельной технике и может быть испольовано в системах передачи дискретной информации.

Цель изобретения - повышение помеоустойчивости ,

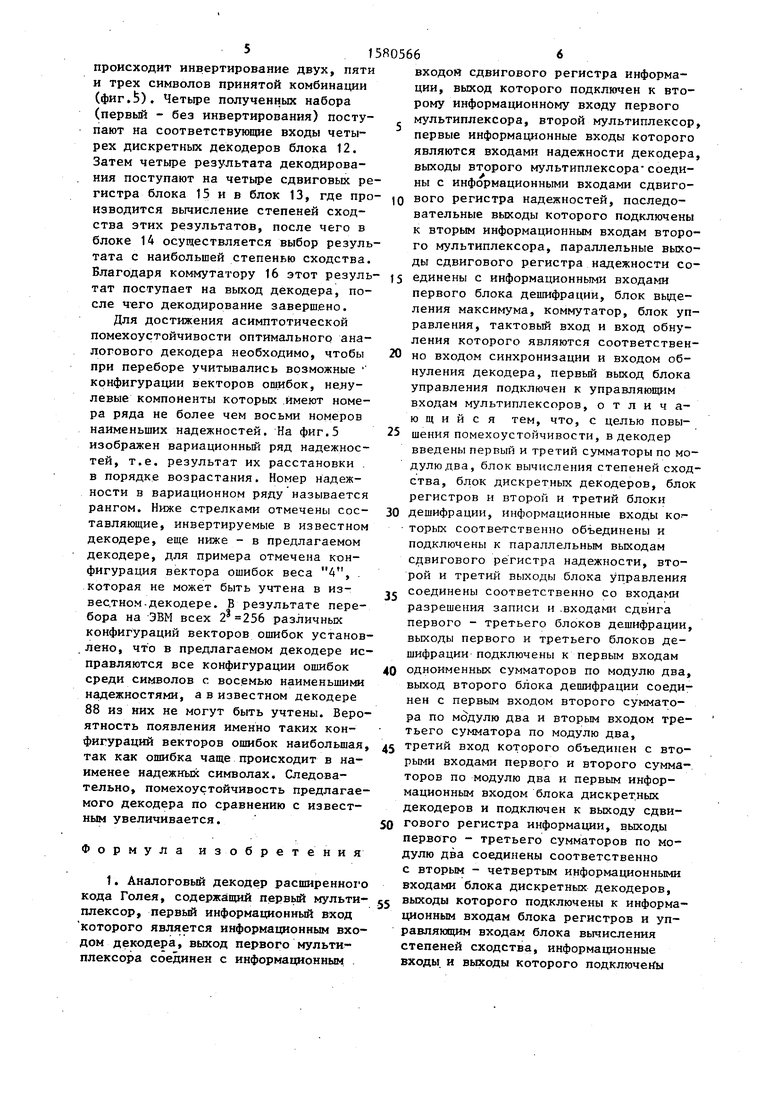

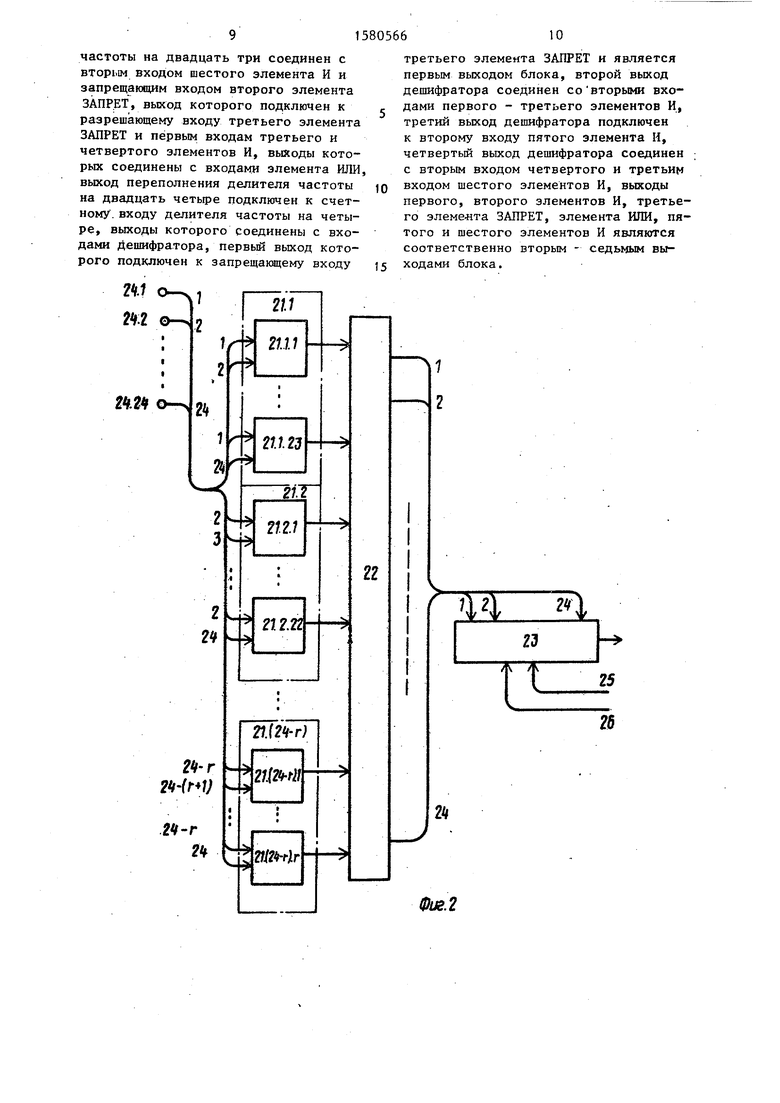

На фиг.1 приведена блок-схема предагаемого декодера; на фиг.2 - выполение блока дешифрации; на фиг.З - выполнение блока вычисления степеней сходства и блока выделения максимуа; на фиг.А - выполнение блока упавления; на фиг.З - принцип инверирования символов принимаемого ко- а, на фиг.6 - диаграммы управляющих сигналов.

Декодер содержит первый 1 и второй 2 мультиплексоры, сдвиговые регистры информации 3 и надежности 4, блок 5 управления, первый - третий блоки 6-8 ешифрации, первый - третий сумматоры 9 - 1 1 по модулю два, блок 12 дискретных декодеров, блок 13 вычисления степеней сходства, блок 14 выделения максимума, блок 15 регистров и коммутатор 16. Декодер содержит также тактовьй вход 17, вход 18 обнуления , информационный вход 19 и вход 20 надежности.

Надежности символов расширенного кода Голея представлены в виде т-раз- рядньк двузначных чисел, поэтому сдвиговый регистр надежности имеет двадцать четыре т-х разряда.

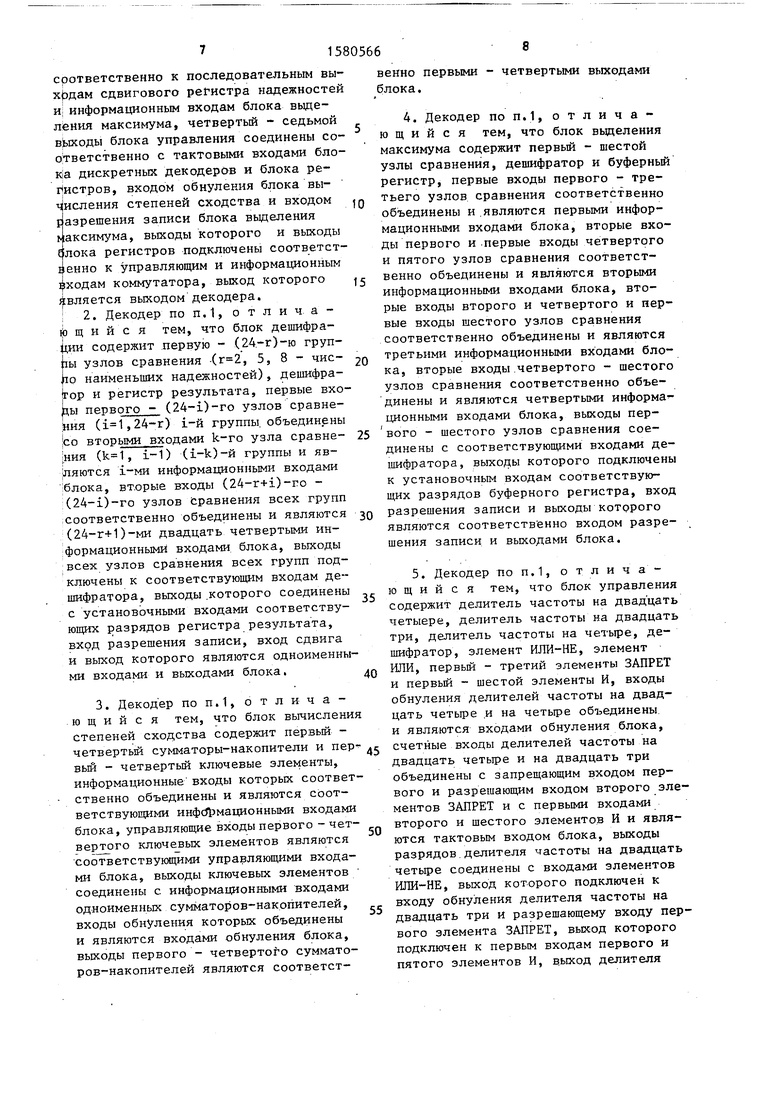

Блок 6 (7,8) дешифрации содержит (фиг.2) группы 21 узлов сравнения, дешифратор 22 и регистр 23 результата. На фиг.2 обозначены информационные входы 24, вход 25 разрешения записи и вход 26 сдвига. В каждой группе 21 осуществляется сравнение соответствующей надежности со всеми последующими вплоть до (24-г)-йх где г - число наименьших из двадцати четырех надежностей. Для блока 6 , для блока 7 , для блока 8 .

Дешифратор 22 содержит двадцать четыре пары сумматор - компаратор, на выходе каждой из которых появляется единица, если составляющая надежность (подаваемая на первые входы узлов соответствующей группы 21) входит в число г наименьших надежностей. Блок 13 вычисления степеней сходства содержит (фиг.З) первый - четвертый ключевые элементы 27 и первый - четвертьй сумматоры-накопители 28. Блок 14 выделения максимума

0

5

0

5

0

5

0

5

0

5

содержит первый - шестой узлы 29 сравнения, дешифратор 30 и буферный регистр 31.

Блок 13 содержит информационные 32 и управляющие 33 входы и вход 34 обнуления, а блок 14 - вход 35 разрешения записи. Блок 12 дискретных декодеров содержит четыре декодера кода Голея, блок 15 регистров - четыре двадцатитрехразрядных сдвиговых регистра для хранения результатов декодирования на время вычислений в блоках 13 и 14.

Блок 5 управления содержит (Фиг.4) делители частоты на двадцать четыре 36, на двадцать три 37 и на четыре 38, дешифратор 39, элемент ИЛИ-НЕ 40, первый - третий элементы 41-43 ЗАПРЕТ, элемент ИЛИ 44 и первый - шестой элементы И 45-50.

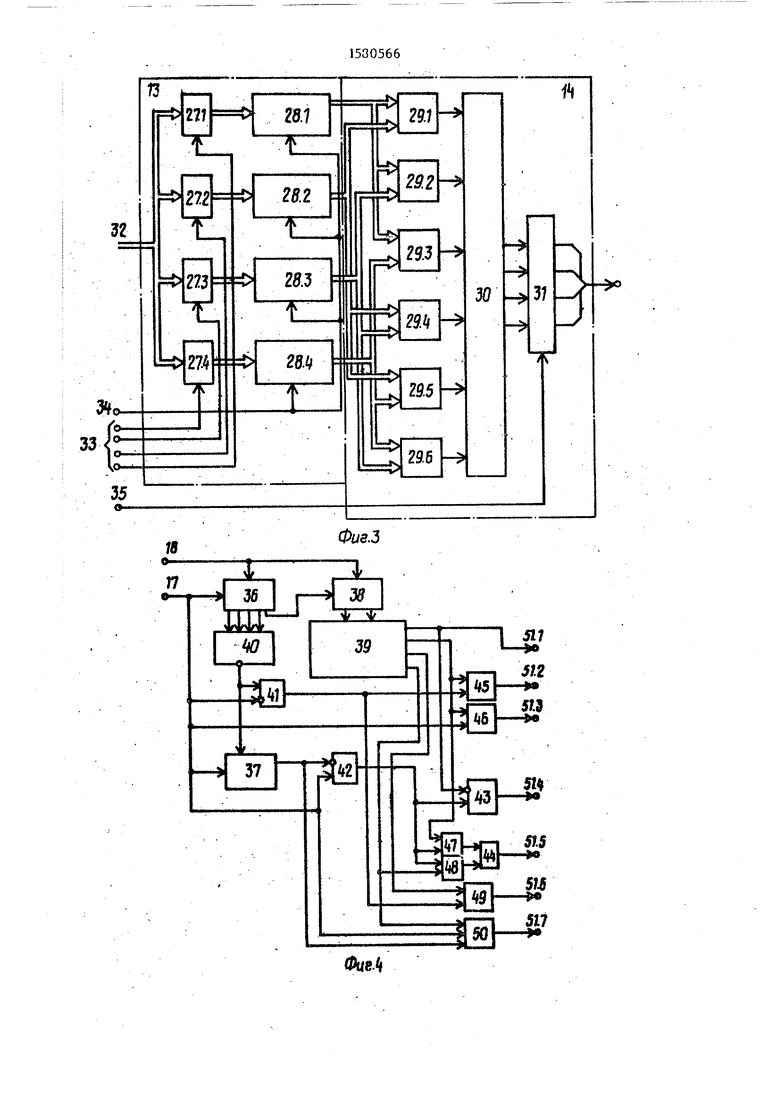

На фиг.5 стрелками отмечены символы, инвертируемые в процессе работы аналогового декодера (предлагаемого и известного). Смысл инвертирований заключается в попытке исправить заранее некоторые из ошибок. Например, во втором из векторов ошибок инвертируются два наименее надежных символа. Если в этих символах действительно произошли ошибки, то кратность исправляемых ошибок увеличивается до пяти (три ошибки в любом месте вариационного ряда исправляются при алгебраическом декодировании.

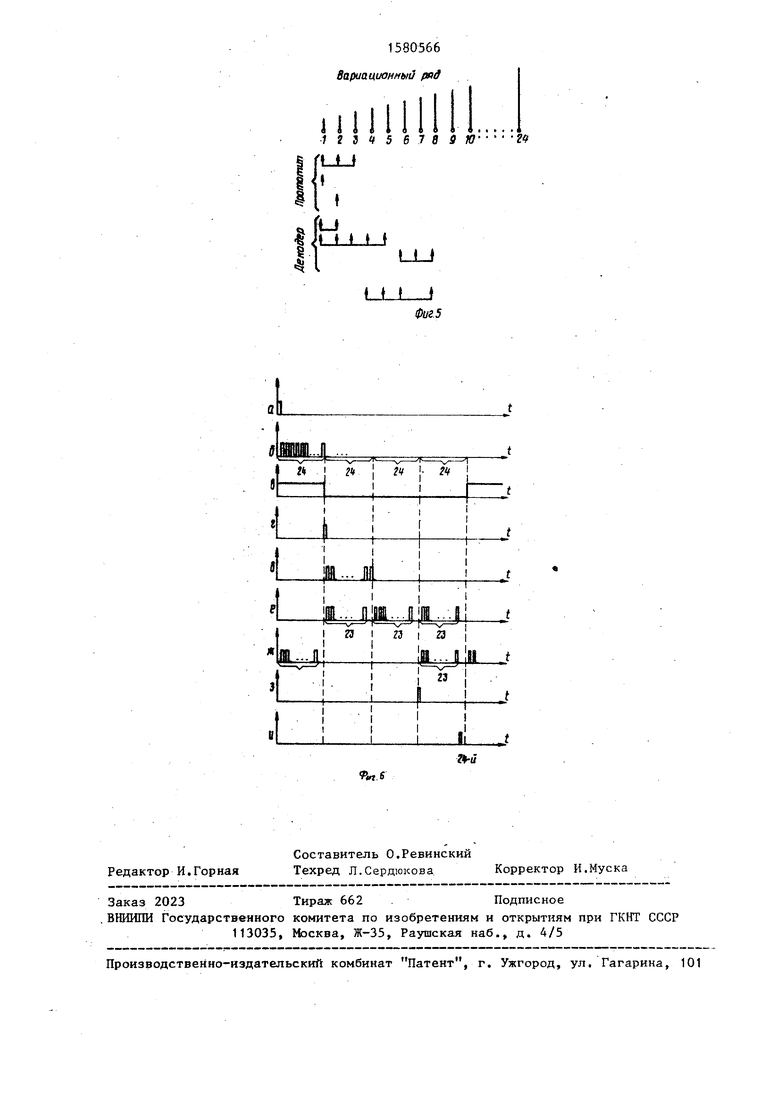

На фиг.6 обозначено: а - сигнал обнуления на входе 18, б - тактовые импульсы на входе 17, в-и - сигналы на выходах 51.1 - 51.7 блока 5 управления.

Работа декодера происходит в два этапа.

На первом этапе на выходы первого 1 и второго 2 мультиплексоров поступают сигналы с входов 19 и 20 и в течение 24 тактов в регистр 4 записываются надежности принимаемого кодового слова, а в регистр 3 - результаты демодуляции символов этого слова. На втором этапе входы мультиплексоров 1 и 2 переключаются, в блоках 6-8 определяются номера двух, пяти и восьми наименьших надежностей и результаты вычислений в этих блоках записываются в их регистры 23. Затем в течение 24 тактов эти результаты последовательно выталкиваются на выходы блоков 6 - 8 ч, благодаря сумматорам 9 - 11 по модулюя два,

происходит инвертирование двух, пяти и трех символов принятой комбинации (фиг.5). Четыре полученных набора (первый - без инвертирования) поступают на соответствующие входы четырех дискретных декодеров блока 12. Затем четыре результата декодирования поступают на четыре сдвиговых регистра блока 15 и в блок 13, где производится вычисление степеней сходства этих результатов, после чего в блоке 14 осуществляется выбор результата с наибольшей степенью сходства. Благодаря коммутатору 16 этот результат поступает на выход декодера, после чего декодирование завершено. Для достижения асимптотической помехоустойчивости оптимального аналогового декодера необходимо, чтобы при переборе учитывались возможные конфигурации векторов ошибок, нену- левые компоненты которых имеют номера ряда не более чем восьми номеров наименьших надежностей. На фиг.5 изображен вариационный ряд надежностей, т.е. результат их расстановки в порядке возрастания. Номер надежности в вариационном ряду называется рангом. Ниже стрелками отмечены составляющие, инвертируемые в известном декодере, еще ниже - в предлагаемом декодере, для примера отмечена конфигурация вектора ошибок веса 4, которая не может быть учтена в известном декодере. В результате перебора на ЭВМ всех 2-256 различных конфигураций векторов ошибок установлено, что в предлагаемом декодере исправляются все конфигурации ошибок среди символов с восемью наименьшими надежностями, а в известном декодере 88 из них не могут быть учтены. Вероятность появления именно таких конфигураций векторов ошибок наибольшая, так как ошибка чаще происходит в наименее надежных символах. Следовательно, помехоустойчивость предлагаемого декодера по сравнению с известным увеличивается.

Формула изобретения

0

5

0

5

е

входом сдвигового регистра информации, выход которого подключен к второму информационному входу первого мультиплексора, второй мультиплексор, первые информационные входы которого являются входами надежности декодера, выходы второго мультиплексора соеди- ны с информационными входами сдвигового регистра надежностей, последовательные выходы которого подключены к вторым информационным входам второго мультиплексора, параллельные выходы сдвигового регистра надежности соединены с информационными входами первого блока дешифрации, блок выделения максимума, коммутатор, блок управления, тактовый вход и вход обнуления которого являются соответственно входом синхронизации и входом обнуления декодера, первый выход блока управления подключен к управляющим входам мультиплексоров, отличающийся тем, что, с целью повышения помехоустойчивости, в декодер введены первый и третий сумматоры по модулю два, блок вычисления степеней сходства, блок дискретных декодеров, блок регистров и второй и третий блоки 0 дешифрации, информационные входы которых соответственно объединены и подключены к параллельным выходам сдвигового регистра надежности, второй и третий выходы блока управления соединены соответственно со входами разрешения записи и входами сдвига первого - третьего блоков дешифрации, выходы первого и третьего блоков дешифрации подключены к первым входам одноименных сумматоров по модулю два, выход второго блока дешифрации соединен с первым входом второго сумматора по модулю два и вторым входом третьего сумматора по модулю два, третий вход которого объединен с вторыми входами первого и второго сумматоров по модулю два и первым информационным входом блока дискретных декодеров и подключен к выходу сдвигового регистра информации, выходы первого - третьего сумматоров по модулю два соединены соответственно с вторым - четвертым информационными входами блока дискретных декодеров, выходы которого подключены к информационным входам блока регистров и управляющим входам блока вычисления степеней сходства, информационные входы и выходы которого подключены

5

0

5

0

соответственно к последовательным вы- х|эдам сдвигового регистра надежностей и информационным входам блока выделения максимума, четвертый - седьмой выходы блока управления соединены соответственно с тактовыми входами блока дискретных декодеров и блока регистров, входом обнуления блока вы- ч исления степеней сходства и входом разрешения записи блока выделения Йаксимума, выходы которого и выходы блока регистров подключены соответственно к управляющим и информационным входам коммутатора, выход которого является выходом декодера.

и являются входами обнуления блока, счетные входы делителей частоты на двадцать четыре и на двадцать три объединены с запрещающим входом первого и разрешающим входом второго элементов ЗАПРЕТ и с первыми входами второго и шестого элементов И и являются тактовым входом блока, выходы разрядов делителя частоты на двадцать четыре соединены с входами элементов ИЛИ-НЕ, выход которого подключен к входу обнуления делителя частоты на двадцать три и разрешающему входу первого элемента ЗАПРЕТ, выход которого подключен к первым входам первого и пятого элементов И, выход делителя

частоты на двадцать три соединен с вторым входом шестого элемента И и запрещающим входом второго элемента ЗАПРЕТ, выход которого подключен к разрешающему входу третьего элемента ЗАПРЕТ и первым входам третьего и четвертого элементов И, выходы которых соединены с входами элемента ИЛИ, выход переполнения делителя частоты на двадцать четыре подключен к счетному входу делителя частоты на четыре, выходы которого соединены с входами Дешифратора, первый выход которого подключен к запрещающему входу

21

третьего элемента ЗАПРЕТ и является первым выходом блока, второй выход дешифратора соединен со вторыми входами первого - третьего элементов И, третий выход дешифратора подключен к второму входу пятого элемента И, четвертый выход дешифратора соединен с вторым входом четвертого и третьим входом шестого элементов И, выходы первого, второго элементов И, третьего элемента ЗАПРЕТ, элемента ИЛИ, пятого и шестого элементов И являются соответственно вторым - седьмым выходами блока.

14 2«1

24

18

Фиг.З

t LU-J-J

| IEEE Transactions on Communications | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Солесос | 1922 |

|

SU29A1 |

| Радиотехника | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Колесник В.Д., Мирончиков Е.Т | |||

| Декодирование циклических кодов | |||

| - М.: Связь, 1968, с.85-86 | |||

| Аналоговый декодер кода с ортогональными проверками | 1986 |

|

SU1401614A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-23—Публикация

1988-04-25—Подача