I1322470

Изобретение относится к импульсной технике и может быть использовано при построении цифровых синтезаторов частотэ хронизаторов, электромузы- кгшьных инструментов и т.д. . 5

Цель изобретения - расширение функциональных возможностей пз тем обеспечения возможности получения удвоенного коэффициента (22 вместо 11) де- I ленкя при сохранении быстродействия О

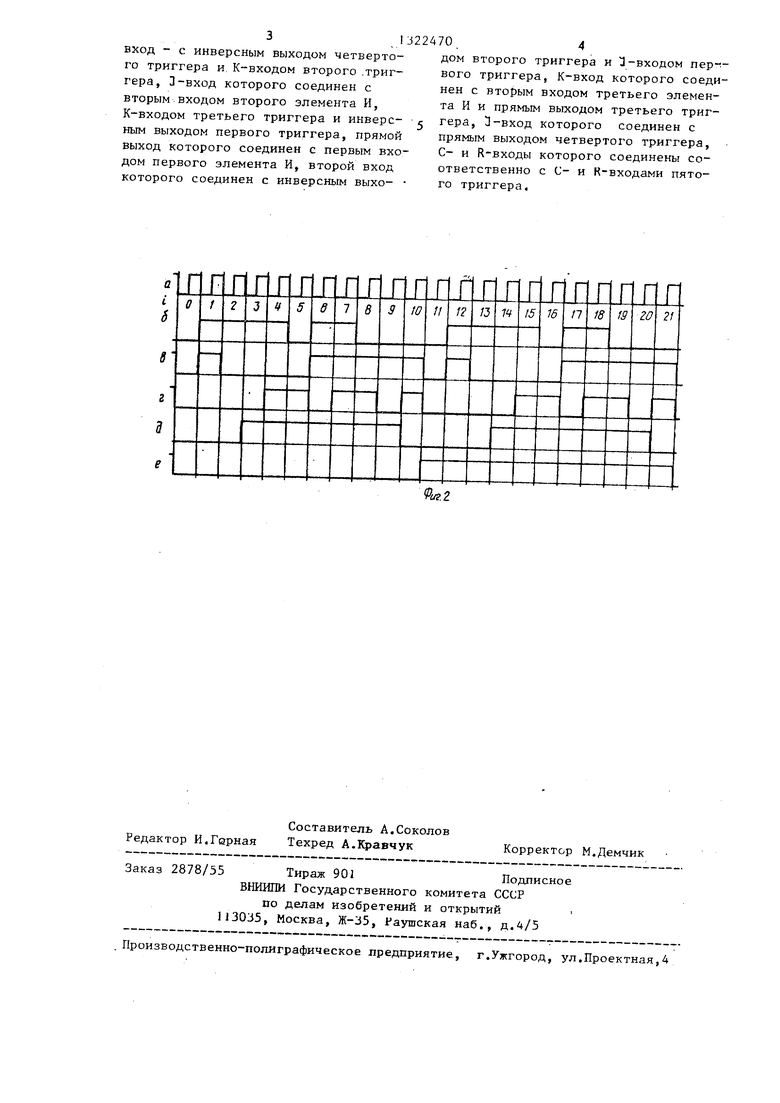

На фиг,1 приведена электрическая функциональная схема синхронного делителя частоты; на фиг,2 - временные диаграммы, поясняющие работу делителя частоты,

Синхронный делитель частоты содержит первый 1, второй 2, третий 3,, четвертый 4 и пятый 5 триггеры,, каждый из которых К-типа с R-входом

,,; 1а а, ; U Q,;

I.,Q,; U

,; к, к, Q,;

к,.,Qj; к .,

Делитель частоты работает следующим образом.

По Сброс, поступающему в виде импульса перед началом работы делителя частоты по шине 9, все триггеры I - 5 устанавливаются в исходное (нулезс1е) состояние.

Появление на шине 10 каждого такт вого импульса (фиг,2а)(по его срезу вызывает изменение состояния одного или нескольких триггеров 1 5 в соответствии с указанными логически(с входом сброса), и первый 6, вто-- 20 ми уравнениями, как показано на временной диаграмме /фиг.2), где i- порядковый номер состояния синхронного делителя частоты после появления импульса на щиие 9, т,-е„ поряд- 25 ковый номер тактового импульса на шине 10; а - входной сигнал на шине 10; б - сигнал Q, на прямом выходе триггера ; в - сигнал Q на прямом выходе триггера 2; г - сигнап Qj на

рой 7 и третий 8 элементы И, при этом К--входом и С-входы всех триггеров соединены соответственно с шиной 9 сброса и тактовой шиной 10, Прямой выход первого триггера 1 соединен с первым входом первого элемента И 6, выход которого соединен с О-входом че1 вертого триггера. 4 второй вход - с инверсным выходом второго триггера 2

менной диаграмме /фиг.2), где i- порядковый номер состояния синхронного делителя частоты после появления импульса на щиие 9, т,-е„ поряд- 25 ковый номер тактового импульса на шине 10; а - входной сигнал на шине 10; б - сигнал Q, на прямом выходе триггера ; в - сигнал Q на прямом выходе триггера 2; г - сигнап Qj на

и 3 ВХОДОМ первого триггера I, инверс-30 прямом выходе триггера 3; д - сигнал ный выход третьего триггера 3 - с 4 прямом выходе триггера 4; е - первым входом второго элемента И 7, вы.ход которого соединен с К-входом четвертого триггера 4 второй вход - с инверсным выходом первого триггера. 35 обеспечивает коэффициент деления, 1, Э-входом второго триггера 2 и К- равный 22, при сохранении быстродей- входом третьего триггера 3, К-вход второго триггера 2 соединен с инверсным выходом четвертого триггера 4 и первым входом третьего элемента И 8, 40 выход которого сое,щкен с 3- и К-зхосиг нал Q на прямом выходе триггера

Таким образом, делитель частоты

ствия,

Формула изобретения

Синхронный делитель частоты, содержащий первый, второй, третий и четвертый триггеры. С- и R-входы которых соединены соответственно с так4S товой шиной и с шиной сброса, пер- вход которого соединен с прямым выхо- „ ,,

. „выи элемент И, выход которого соедидом -четвертого триггера 4, Прямой и

нен с Л-входом четвертого триггера,

которого соединен с выходом второго элемента И, первый вход котодами пятого триггера 5, второй вход- с К-входом первого тридтера и прямым выходом третьего триггера 3, 3инверсные выходные сигналы снимаются с coOTBeTCTByioaiHX выходов пятого

триггера 5 (шины П и 12 соответствен- соединен с инверсным выходом . но). Дапитель частоты содер шт также ..ретьего триггера, о. т л и ч а ю выходную шину 13, на которой выходной сигнал реализует коэффициент деления К 11,

щ и и с я тем, что, с целью расшире- шя функциональных возможностей путем обеспечения возможности получе- 2 ния удвоенного коэффициента деления при сохранении быстродействия, в nei введе а1 пятый триггер и третий элемент И, выход которого соединен с 3 и К-входами пятого триггера, первый

При такой схеме соединения логические уравнения для 3-й К-входов всех триггеров синхронного делителя частоты (на 22) следующее;

,,; 1а а, ; U Q,;

I.,Q,; U

,; к, к, Q,;

к,.,Qj; к .,

I

Делитель частоты работает следующим образом.

По Сброс, поступающему в виде импульса перед началом работы делителя частоты по шине 9, все триггеры I - 5 устанавливаются в исходное (нулезс1е) состояние.

Появление на шине 10 каждого тактового импульса (фиг,2а)(по его срезу) вызывает изменение состояния одного или нескольких триггеров 1 5 в соответствии с указанными логическими уравнениями, как показано на временной диаграмме /фиг.2), где i- порядковый номер состояния синхронного делителя частоты после появления импульса на щиие 9, т,-е„ поряд- ковый номер тактового импульса на шине 10; а - входной сигнал на шине 10; б - сигнал Q, на прямом выходе триггера ; в - сигнал Q на прямом выходе триггера 2; г - сигнап Qj на

прямом выходе триггера 3; д - сигнал 4 прямом выходе триггера 4; е - обеспечивает коэффициент деления, равный 22, при сохранении быстродей-

прямом выходе триггера 3; д - сигнал 4 прямом выходе триггера 4; е - обеспечивает коэффициент деления, равный 22, при сохранении быстродей-

сиг нал Q на прямом выходе триггера

мом выходе триггера 3; д - сигна прямом выходе триггера 4; е - спечивает коэффициент деления, ный 22, при сохранении быстродей

Таким образом, делитель частоты

прямом 4 обеспе равный

ствия,

прямом выходе триггера 3; д - сигнал 4 прямом выходе триггера 4; е - обеспечивает коэффициент деления, равный 22, при сохранении быстродей-

Формула изобретения

соединен с инверсным выходом ..ретьего триггера, о. т л и ч а ю

щ и и с я тем, что, с целью расшире- шя функциональных возможностей путем обеспечения возможности получе- ния удвоенного коэффициента деления при сохранении быстродействия, в nei введе а1 пятый триггер и третий элемент И, выход которого соединен с 3 и К-входами пятого триггера, первый

вход - с инверсным выходом четвертого триггера и К-входом второго .триггера, О-вход которого соединен с вторым входом второго элемента И, К-входом третьего триггера и инверсным выходом первого триггера, прямой выход которого соединен с первым вхо дом первого элемента И, второй вход которого соединен с инверсным выхоРедактор И,Гарная

Составитель А.Соколов Техред А.10равчук

Заказ 2878/35 Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

.Производственно-полиграфическое лредприятие, г.Ужгород, ул.Проектная,4

22470.4

дом второго триггера и U-входом nep-i- вого триггера, К-вход которого соединен с вторым входом третьего элемента И и прямым выходом третьего триг- с гера, 3-вход которого соединен с прямым выходом четвертого триггера, С- и R-входы которого соединены соответственно с С- и К-входами пятого триггера.

Корректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты | 1986 |

|

SU1374425A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396274A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396275A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Синхронный делитель частоты | 1986 |

|

SU1429317A1 |

| Синхронный делитель частоты с четным коэффициентом деления | 1987 |

|

SU1629990A1 |

| Синхронный делитель частоты на 9 на JK-триггерах | 1987 |

|

SU1444938A1 |

| Синхронный делитель частоты | 1986 |

|

SU1354415A1 |

| Синхронный делитель частоты на 9 | 1986 |

|

SU1378055A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396273A1 |

Изобретение может быть использовано для построения, например, цифровых синтезаторов частот. Цель изобретения - расширение функциональных возможностей делителя частоты. Делитель частоты содержит 1К-тригге- ры 1 - 4 и элементы И 6 и 7. Введение 1К-триггера 5 и элемента И 8 обеспечивает коэффициент деления 22 при сохранении быстродействия устройства. 2 ил. (Л И

| Делитель частоты на 44 | 1979 |

|

SU801256A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-12—Подача