Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей биимпульсного кода в код без возврата к нулю.

Цель изобретения - упрощение устройства .

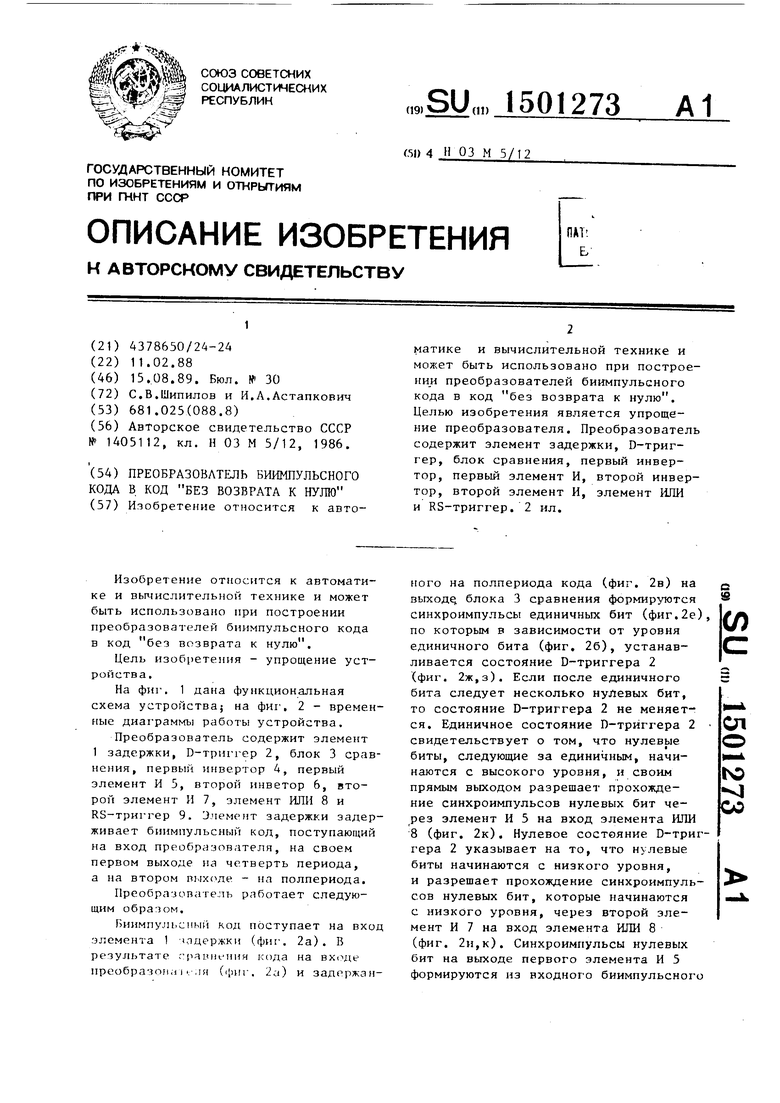

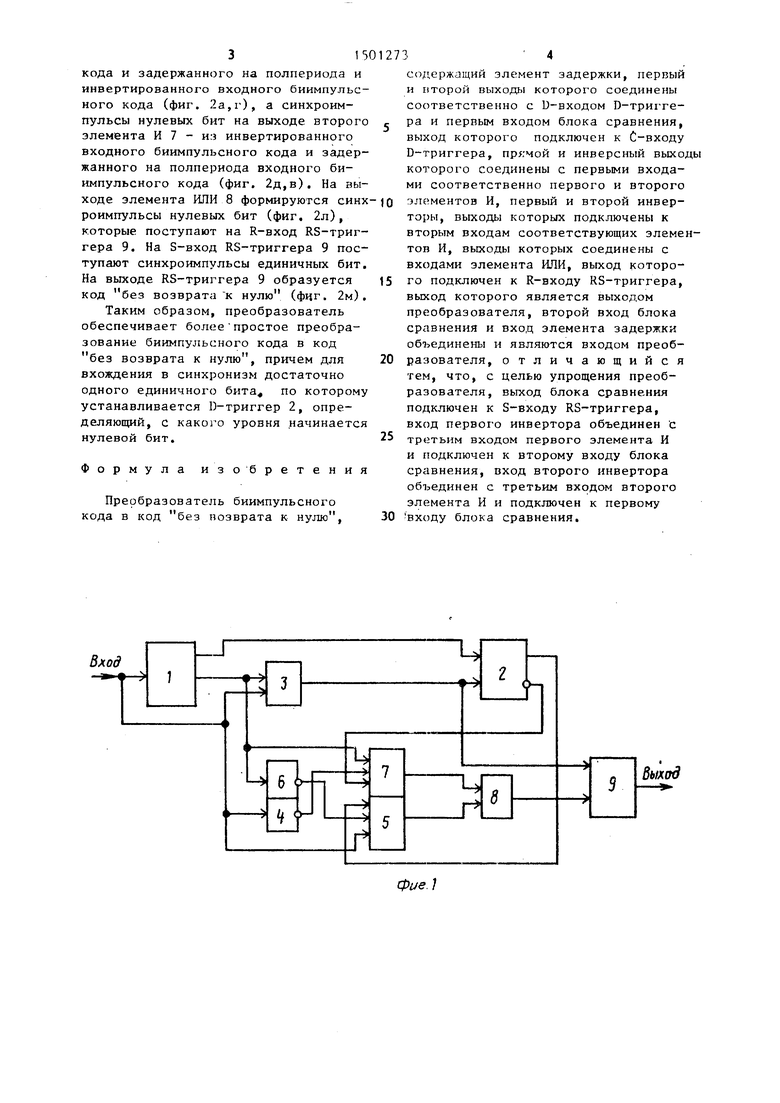

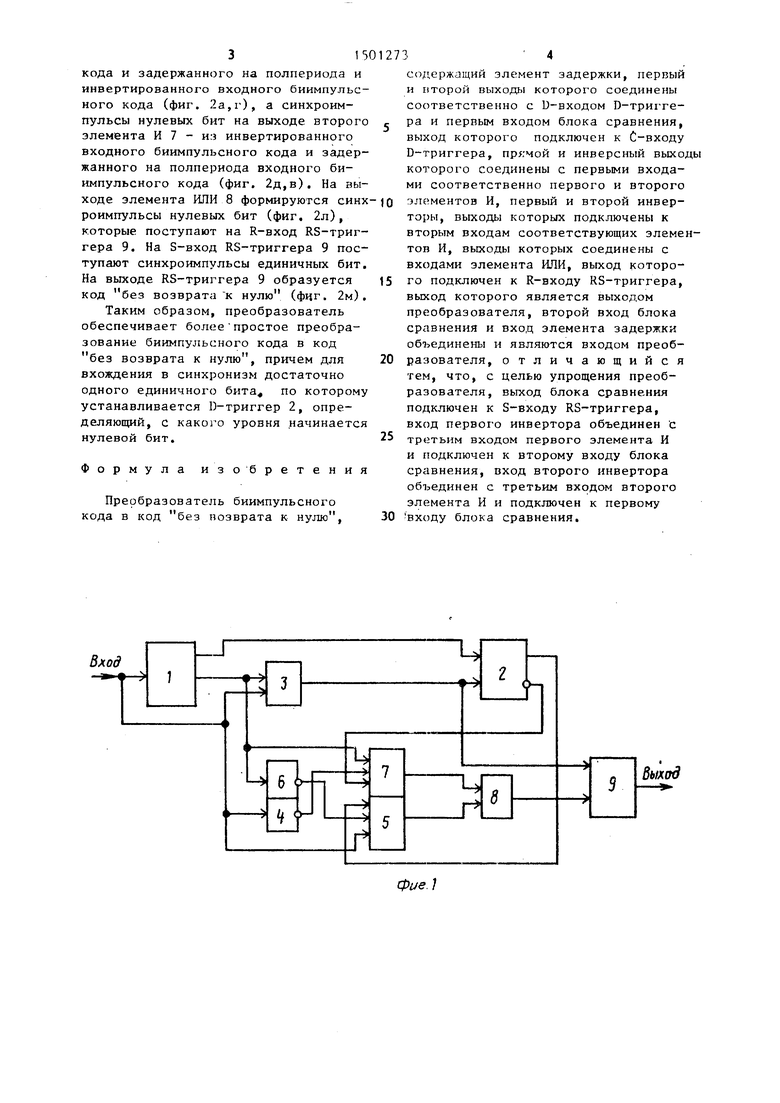

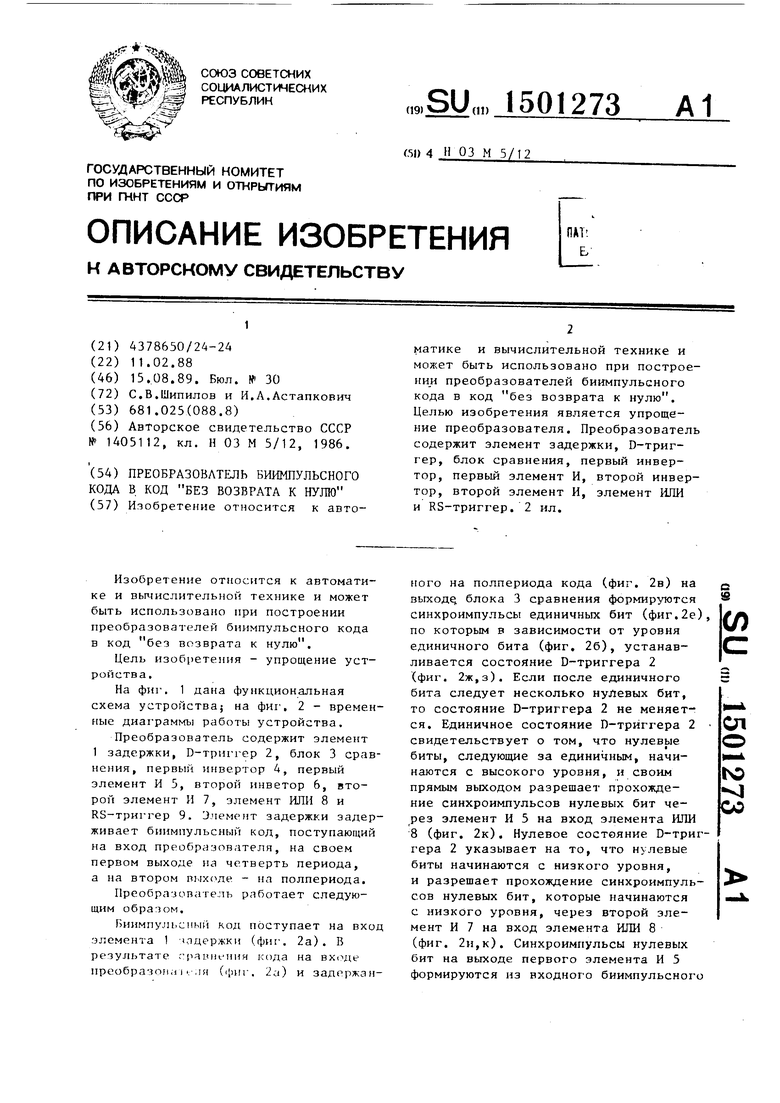

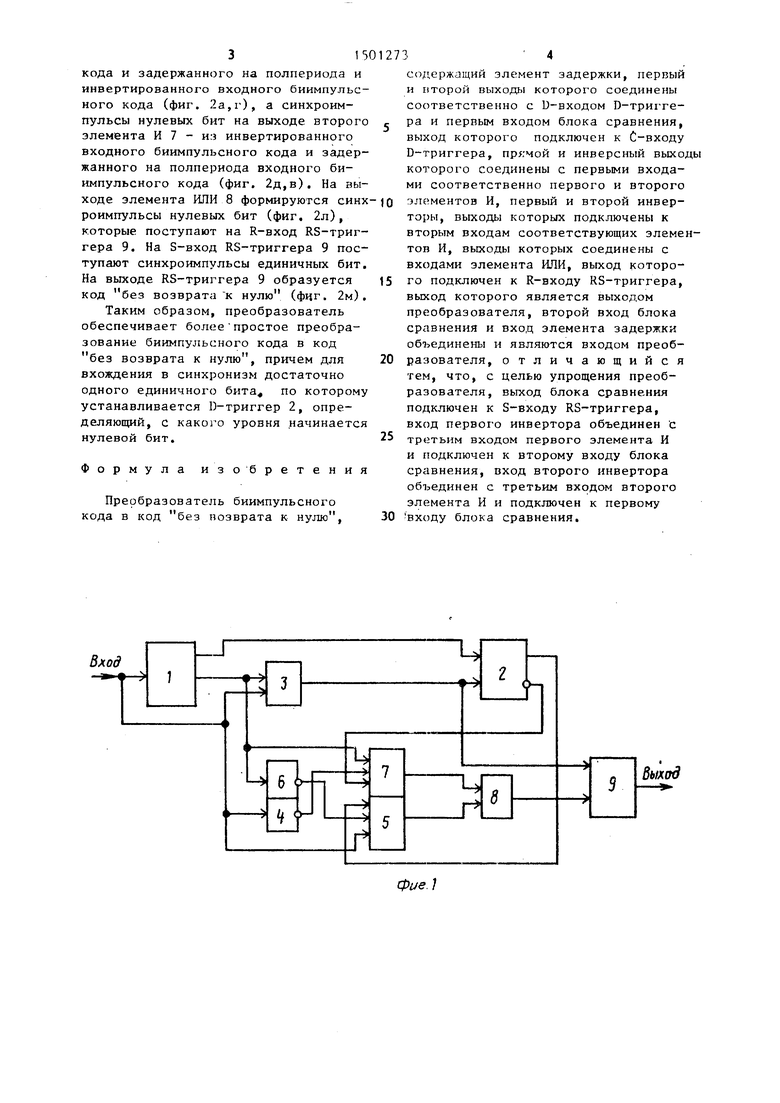

На фиг. 1 дана функциональная схема устройства; на фиг. 2 - временные диаграммы работы устройства.

Преобразователь содержит элемент 1 задержки, D-триггер 2, блок 3 сравнения, первый инвертор 4, первый

6,

ВТОэлемент И 5, второй инветор рой элемент И 7, элемент ИЛИ 8 и RS-триггер 9. Элемент задержки задерживает биимпульсный код, поступающий на вход преобразователя, на своем первом выходе на четверть периода, а на втором (1де - на полпериода.

Преобразователь работает следующим обра :з ом.

Биимпул1.смый код поступает на вход элемента 1 чпдержки (фиг . 2а) . В результате граинеиия кода на BXivif преобразона I |,,1Я (ilinr. 2а) и задержанатиожети кода

устяремен.

мент сравй

ВТОизадерающийем да, ода.

дуюа вход В ivif ержанного на полпериода кода (фиг. 2в) на выходу блока 3 сравнения формируются синхроимпульсы единичных бит (фиг.2е), по которым в зависимости от уровня единичного бита (фиг. 2б), устанавливается состояние D-триггера 2 (фиг. 2ж,з). Если после единичного бита следует несколько нулевых бит, то состояние D-триггера 2 не меняется. Единичное состояние D-трйггера 2 свидетельствует о том, что нулевые биты, следующие за единичным, начинаются с высокого уровня, и своим прямым выходом разрешает прохождение синхроимпульсов нулевых бит через элемент И 5 на вход элемента ИЛИ 8 (фиг. 2к). Нулевое состояние D-триггера 2 указывает на то, что нулевые биты начинаются с низкого уровня, и разрешает прохождение синхроимпульсов нулевых бит, которые начинаются с низкого уровня, через второй элемент И 7 на вход элемента ИЛИ 8 (фиг. 2и,к). Синхроимпульсы нулевых бит на выходе первого элемента И 5 формируются из входного биимпульсного

С S

(Л

СП

to

Ч

СО

31501273

кода и задержанного на полпериода и инвертированного входного биимпульс- ного кода (фиг. 2а,г), а синхроимпульсы нулевых бит на выходе второго элемента И 7 - из инвертированного входного биимпульсного кода и задержанного на полпериода входного биимпульсного кода (фиг. 2д,в). На высодержащий элемент задержки, первый и нторой выходы которого соединены соответственно с D-входом В-три1те- ра и первым входом блока сравнения, выход которого подключен к С-входу D-триггера, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь биимпульсного кода в код "без возврата к нулю | 1986 |

|

SU1405112A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2259010C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИИМПУЛЬСНОГО КОДА В БИНАРНЫЙ КОД | 2004 |

|

RU2258305C1 |

| Преобразователь код-напряжение | 1988 |

|

SU1508348A1 |

| Устройство для приема информации | 1988 |

|

SU1672571A1 |

| Преобразователь интервалов времени в цифровой код | 1980 |

|

SU930217A1 |

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1554115A1 |

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1255984A2 |

| Преобразователь кода | 1989 |

|

SU1612376A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2259009C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей биимпульсного кода в код "без возврата к нулю". Целью изобретения является упрощение преобразователя. Преобразователь содержит элемент задержки, D - триггер, блок сравнения, первый инвертор, первый элемент И, второй инвертор, второй элемент И, элемент ИЛИ и RS-триггер. 2 ил.

ходе элемента ИЛИ 8 формируются синх-jo элементов И, первый и второй инверроимпульсы нулевых бит (фиг. 2л), которые поступают на R-вход RS-триг- гера 9. На S-вход RS-триггера 9 поступают синхроимпульсы единичных бит. На выходе RS-триггера 9 образуется 15 код без возврата к нулю (фчг. 2м).

Таким образом, преобразователь обеспечивает более простое преобразование биимпульсного кода в код без возврата к нулю, причем для 20 вхождения в синхронизм достаточно одного единичного бита, по которому устанавливается 1)-триггер 2, определяющий, с какого уровня начинается нулевой бит.25

Формула изо бретения

Преобразователь биимпульсного кода в код без возврата к нулю, 30

торы, выходы которых подключены к вторым входам соответствующих элемен тов И, выходы которых соединены с входами элемента ИЛИ, выход которого подключен к R-входу RS-триггера, выход которого является выходом преобразователя, второй вход блока сравнения и вход элемента задержки объединены и являются входом преобразователя, отличающийся тем, что, с целью упрощения преобразователя, выход блока сравнения подключен к S-входу RS-триггера, вход первого инвертора объединен с третьим входом первого элемента И и подключен к второму входу блока сравнения, вход второго инвертора объединен с третьим входом второго элемента И и подключен к первому входу блока сравнения.

Вход

торы, выходы которых подключены к вторым входам соответствующих элеметов И, выходы которых соединены с входами элемента ИЛИ, выход которого подключен к R-входу RS-триггера, выход которого является выходом преобразователя, второй вход блока сравнения и вход элемента задержки объединены и являются входом преобразователя, отличающийся тем, что, с целью упрощения преобразователя, выход блока сравнения подключен к S-входу RS-триггера, вход первого инвертора объединен с третьим входом первого элемента И и подключен к второму входу блока сравнения, вход второго инвертора объединен с третьим входом второго элемента И и подключен к первому входу блока сравнения.

Выход

| Преобразователь биимпульсного кода в код "без возврата к нулю | 1986 |

|

SU1405112A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-11—Подача