Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации.

Известен преобразователь кода (см. А.С. СССР №1236615 от 25.04.84, МКИ: Н 03 М 5/12, «Декодер», А.Б.Бурченко, В.Н.Степанов, В.Д.Тришкин и А.А.Яковлев, опубл. 07.06.86, Бюл. №21), содержащий первый и второй D-триггеры, элемент задержки, элемент НЕ, выход которого соединен с входом синхронизации второго D-триггера, вход установки в нуль которого подключен к выходу элемента задержки, RS-триггер и элемент И, выход которого подключен к входу элемента задержки, выход которого является выходом синхронизации устройства и соединен с входом установки в нуль первого D-триггера, вход синхронизации которого объединен с входом элемента НЕ и является входом устройства, инверсный выход каждого D-триггера подключен к информационному входу другого D-триггера, к соответствующему входу элемента И и к соответствующему входу RS-триггера, выход которого является информационным выходом устройства.

Недостатком известного преобразователя кода является сложность схемы, обусловленная наличием большого количества соединений между элементами.

Наиболее близким по совокупности существенных признаков к заявляемому изобретению является преобразователь кода (см. А.С. СССР №1363476 от 07.03.86, МКИ: Н 03 М 5/12, «Преобразователь кода», А.Г.Исаев и И.В.Келтуяла, опубл. 30.12.87, Бюл. №48), содержащий элемент задержки, первый выход которого соединен с первыми входами первого и второго триггеров, второй вход первого триггера является входом преобразователя, инверсный выход второго триггера соединен с первым входом третьего триггера, прямой выход которого является первым (информационным) выходом преобразователя, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход второго триггера и вход элемента задержки объединены и подключены к входу преобразователя, третьи входы первого и второго триггеров объединены и подключены к первому выходу элемента задержки, второй выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, прямой выход первого триггера соединен с вторым входом третьего триггера, инверсный выход которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является вторым (тактовым) выходом преобразователя.

Недостатками известного преобразователя кода являются:

- необходимость формирования признака начала информационной посылки, обеспечивающего взаимную синхронизацию приемника и передатчика и достоверную передачу сообщений вследствие использования фазоманипулированного кода в качестве входного кода преобразователя;

- отсутствие возможности формирования на выходе преобразователя кода сигнала стробирования слова вследствие отсутствия в преобразователе кода функции выдачи сигнала стробирования слова при наличии полезной информации на входе преобразователя.

Задачей, на решение которой направлено заявляемое изобретение, является создание преобразователя кода, обладающего расширенными функциональными возможностями, а именно: преобразование входной самосинхронизирующейся последовательности импульсов, не требующей дополнительного формирования признака начала информационной посылки, формирование преобразователем кода сигнала стробирования слова.

Технический результат, заключающийся в расширении функциональных возможностей, достигается тем, что в преобразователь кода, содержащий первый, второй и третий триггеры, последний из которых является RS-триггером, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, информационные вход и выход, тактовый выход, введены четвертый триггер, элемент ИЛИ-НЕ, инвертор, формирователь импульса по фронту и срезу, первый и второй счетчики, формирователь импульса по фронту, элемент И, элемент ИЛИ, тактовый вход и выход стробирования, первый, второй и четвертый триггеры выполнены в виде RS-триггеров, S-вход последнего из которых соединен с информационным входом преобразователя, R-входом первого счетчика, входами инвертора и формирователя импульса по фронту и срезу, R-вход - с выходом формирователя импульса по фронту и R-входом третьего RS-триггера, а инверсный выход - с первыми входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента ИЛИ-НЕ, второй вход которого соединен с тактовым входом преобразователя, а выход - с тактовыми входами первого и второго счетчиков, R-вход последнего из которых соединен с выходом инвертора, выход второго разряда - со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и S-входом третьего RS-триггера, а выход третьего разряда - с S-входом второго RS-триггера, выход которого соединен с первым входом элемента ИЛИ, а R-вход - с выходом второго разряда первого счетчика, выход третьего разряда которого соединен с S-входом первого RS-триггера, а выход четвертого разряда - с входом формирователя импульса по фронту, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с R-входом первого RS-триггера, выход которого соединен со вторым входом элемента ИЛИ, выход которого соединен с информационным выходом преобразователя, выход формирователя импульса по фронту и срезу соединен с первым входом элемента И, второй вход которого соединен с выходом третьего RS-триггера и выходом стробирования преобразователя, а выход - с тактовым выходом преобразователя.

Указанная совокупность признаков позволяет расширить функциональные возможности преобразователя кода, а именно:

- обеспечить преобразование входной самосинхронизирующейся последовательности импульсов, не требующей дополнительного формирования признака начала информационной посылки, за счет использования кода, характеризующегося обязательной сменой уровня в начале каждого битового интервала, логический "0" и логическая "1" принимают на время битового интервала высокий или низкий уровень сигнала, при этом длительность битового интервала логического "0" меньше длительности битового интервала логической "1";

- обеспечить формирование на выходе преобразователя кода сигнала стробирования слова за счет определения наличия полезной информации на входе преобразователя и последующей выдачи сигнала стробирования слова.

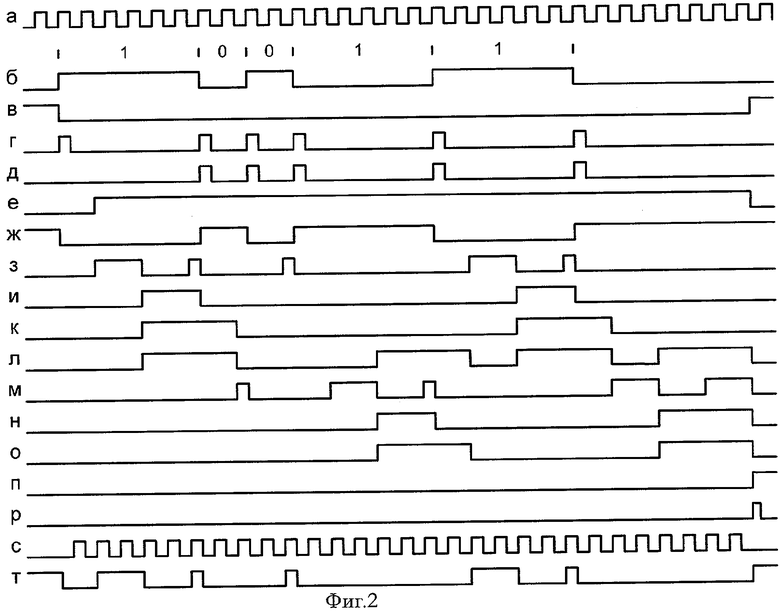

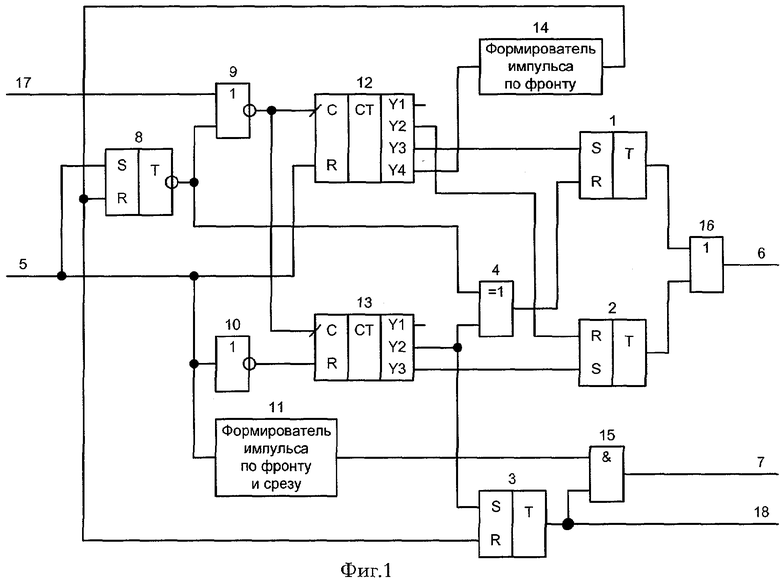

На фиг.1 приведена принципиальная электрическая схема преобразователя кода; на фиг.2 - временные диаграммы работы преобразователя кода.

Преобразователь кода содержит (см. фиг.1) первый 1, второй 2 и третий 3 триггеры, последний из которых является RS-триггером, элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, информационные вход 5 и выход 6, тактовый выход 7, четвертый триггер 8, элемент 9 ИЛИ-НЕ, инвертор 10, формирователь 11 импульса по фронту и срезу, первый 12 и второй 13 счетчики, формирователь 14 импульса по фронту, элемент 15 И, элемент 16 ИЛИ, тактовый вход 17 и выход 18 стробирования. Первый 1, второй 2 и четвертый 8 триггеры выполнены в виде RS-триггеров. S-вход четвертого RS-триггера 8 соединен с информационным входом 5 преобразователя, R-входом первого счетчика 12, входами инвертора 10 и формирователя 11 импульса по фронту и срезу, R-вход - с выходом формирователя 14 импульса по фронту и R-входом третьего RS-триггера 3, а инверсный выход - с первыми входами элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента 9 ИЛИ-НЕ. Второй вход элемента 9 ИЛИ-НЕ соединен с тактовым входом 17 преобразователя, а выход - с тактовыми входами первого 12 и второго 13 счетчиков, R-вход последнего из которых соединен с выходом инвертора 10, выход второго разряда - со вторым входом элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ и S-входом третьего RS-триггера 3, а выход третьего разряда - с S-входом второго RS-триггера 2. Выход второго RS-триггера 2 соединен с первым входом элемента 16 ИЛИ, а R-вход - с выходом второго разряда первого счетчика 12, выход третьего разряда которого соединен с S-входом первого RS-триггера 1, а выход четвертого разряда - с входом формирователя 14 импульса по фронту. Выход элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с R-входом первого RS-триггера 1, выход которого соединен со вторым входом элемента 16 ИЛИ, выход которого соединен с информационным выходом 6 преобразователя. Выход формирователя 11 импульса по фронту и срезу соединен с первым входом элемента 15 И, второй вход которого соединен с выходом третьего RS-триггера 3 и выходом 18 стробирования преобразователя, а выход - с тактовым выходом 7 преобразователя.

Формирователь 11 импульса по фронту и срезу может быть выполнен по схеме, представленной в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.58, рис.1.37а. Формирователь 14 импульса по фронту может быть выполнен по схеме, представленной в книге Хоровиц П., Хилл У. «Искусство схемотехники: В 3-х томах: Т.2.» Пер. с англ. - 4-е изд., перераб. и доп. - М.: Мир, 1993, стр.173, рис.8.97а.

Преобразователь кода работает следующим образом.

В исходном состоянии на тактовом входе 17, информационном входе 5, информационном выходе 6, тактовом выходе 7 и выходе 9 стробирования присутствует уровень логического "0". Первый 1, второй 2, третий 3 и четвертый 8 RS-триггеры, первый 12 и второй 13 счетчики находятся в состоянии логического "0".

На тактовый вход 17 (см.фиг.2, а) поступают тактовые импульсы. Преобразователь готов к преобразованию кода. На информационный вход 5 (см. фиг.2,б) поступает информационная посылка, причем на один битовый интервал информационной посылки, соответствующий логической "1", приходится шесть импульсов на тактовом входе 17, а на один битовый интервал информационной посылки, соответствующий логическому "0", - два импульса на тактовом входе 17. По приходу на информационный вход 5 информационной посылки на S-вход RS-триггера 8 поступает уровень логической "1". RS-триггер 8 устанавливается в единичное состояние, с его инверсного выхода (см.фиг.2, в) на первый вход элемента 9 ИЛИ-НЕ поступает уровень логического "0" и переводит элемент 9 ИЛИ-НЕ в режим инверсии информации, поступающей на его второй вход. С приходом информационной посылки на выходе формирователя 11 импульса по фронту и срезу (см.фиг.2, г) вырабатывается импульс, поступающий на первый вход элемента 15 И. На состояние тактового выхода 7 (см.фиг.2, д) это не оказывает влияния, т.к. RS-триггер 3 находится в нулевом состоянии и уровень логического "0" с его выхода (см.фиг.2, е), поступая на второй вход элемента 15 И, запрещает прохождение импульсов с первого входа элемента 15 И на его выход.

Преобразование нечетных битов информационной посылки происходит следующим образом. По приходу на информационный вход 5 нечетного бита информационной посылки уровень логической "1" поступает на R-вход счетчика 12, удерживая его в нулевом состоянии, и на вход инвертора 10. На выходе инвертора 10 (см.фиг.2, ж) устанавливается уровень логического "0", который, поступая на R-вход счетчика 13, снимает удерживающий счетчик 13 в нулевом состоянии потенциал и разрешает его переключение. По срезам импульсов, поступающих на тактовый вход 17, происходит переключение счетчика 13. По срезу второго импульса, поступающего на тактовый вход 17, на выходе второго разряда счетчика 13 (см.фиг.2, з) устанавливается уровень логической "1", который поступает на S-вход третьего RS-триггера 3, а также через элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ поступает на R-вход RS-триггера 1 для установки последнего в нулевое состояние. При этом в процессе преобразования первого бита информационной посылки RS-триггер 3 устанавливается в единичное состояние, уровень логической "1" с выхода RS-триггера 3 поступает на выход стробирования 18, а также на второй вход элемента 15 И, разрешая прохождение импульсов с выхода формирователя 11 импульса по фронту и срезу на тактовый выход 7. Если текущий преобразуемый бит информационной посылки соответствует логической "1", то по срезу четвертого импульса, поступающего на тактовый вход 17, на выходе третьего разряда счетчика 13 (см.фиг.2, и) устанавливается уровень логической "1", который поступает на S-вход RS-триггера 2 и устанавливает последний в единичное состояние, в противном случае RS-триггер 2 остается в нулевом состоянии. Логический уровень выхода RS-триггера 2 (см.фиг.2, к) через элемент 16 ИЛИ поступает на информационный выход 6 (см.фиг.2, л). В момент окончания битового интервала на входе формирователя 11 импульса по фронту и срезу формируется отрицательный перепад. На выходе формирователя 11 импульса по фронту и срезу вырабатывается импульс, который через элемент 15 И поступает на тактовый выход 7. В это время на информационном выходе 6 присутствует логический уровень преобразованного бита информационной посылки.

Преобразование четных битов информационной посылки происходит следующим образом. По приходу на информационный вход 5 четного бита информационной посылки уровень логического "0" поступает на R-вход счетчика 12, снимая удерживающий счетчик 12 в нулевом состоянии потенциал и разрешая его переключение, и на вход инвертора 10. На выходе инвертора 10 устанавливается уровень логической "1", который поступает на R-вход счетчика 13, удерживая его в нулевом состоянии. По срезам импульсов, поступающих на тактовый вход 17, происходит переключение счетчика 12. По срезу второго импульса, поступающего на тактовый вход 17, на выходе второго разряда счетчика 12 (см.фиг.2, м) устанавливается уровень логической "1", который поступает на R-вход RS-триггера 2 для установки последнего в нулевое состояние. Если текущий преобразуемый бит информационной посылки соответствует логической "1", то по срезу четвертого импульса, поступающего на тактовый вход 17, на выходе третьего разряда счетчика 12 (см.фиг.2, н) устанавливается уровень логической "1", который поступает на S-вход RS-триггера 1 и устанавливает последний в единичное состояние, в противном случае RS-триггер 1 остается в нулевом состоянии. Логический уровень выхода RS-триггера 1 (см.фиг.2, о) через элемент 16 ИЛИ поступает на информационный выход 6. В момент окончания битового интервала информационной посылки на входе формирователя 11 импульса по фронту и срезу формируется положительный перепад. На выходе формирователя 11 импульса по фронту и срезу вырабатывается импульс, который через элемент 15 И поступает на тактовый выход 7. В это время на информационном выходе 6 присутствует логический уровень преобразованного бита информационной посылки.

После преобразования последнего бита информационной посылки уровень логического "0" поступает на R-вход счетчика 12, снимая удерживающий счетчик 12 в нулевом состоянии потенциал и разрешая его переключение, и на вход инвертора 10. На выходе инвертора 10 устанавливается уровень логической "1", который поступает на R-вход счетчика 13, удерживая его в нулевом состоянии. По срезам импульсов, поступающих на тактовый вход 17, происходит переключение счетчика 12. По срезу второго импульса, поступающего на тактовый вход 17, на выходе второго разряда счетчика 12 устанавливается уровень логической "1", который поступает на R-вход RS-триггера 2 для установки последнего в нулевое состояние. По срезу четвертого импульса, поступающего на тактовый вход 17, на выходе третьего разряда счетчика 12 устанавливается уровень логической "1", который поступает на S-вход RS-триггера 1 и устанавливает последний в единичное состояние. Уровень логической "1" с выхода RS-триггера 1 через элемент 16 ИЛИ поступает на информационный выход 6. По срезу восьмого импульса, поступающего на тактовый вход 17, на выходе четвертого разряда счетчика 12 (см.фиг.2, п) устанавливается уровень логической "1", который поступает на вход формирователя 14 импульса по фронту, на выходе которого (см.фиг.2, р) вырабатывается импульс, поступающий на R-входы RS-триггеров 3 и 8, устанавливая их в нулевое состояние. Уровень логической "1" с инверсного выхода RS-триггера 8 поступает на первый вход элемента 9 ИЛИ-НЕ, выводя элемент 9 ИЛИ-НЕ из режима инверсии информации, поступающей на его второй вход, и блокируя, таким образом, поступление тактовых импульсов на тактовые входы счетчиков 12 и 13 (см.фиг.2, с), и через элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ на R-вход RS-триггера 1 (см.фиг.2, т), устанавливая его в нулевое состояние. Таким образом, на информационном выходе 6 и выходе 18 стробирования устанавливается уровень логического "0".

Для преобразования следующей информационной посылки необходимо подать ее на информационный вход 5. Следует отметить, что количество битов в информационной посылке нечетное.

Изготовлен лабораторный макет преобразователя кода, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2002 |

|

RU2249911C2 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2002 |

|

RU2253944C2 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2274949C2 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 2005 |

|

RU2297096C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2258304C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИИМПУЛЬСНОГО КОДА В БИНАРНЫЙ КОД | 2004 |

|

RU2258305C1 |

| Устройство фиксации переходов через нуль периодического сигнала | 1984 |

|

SU1187145A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2262191C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2259009C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2003 |

|

RU2260907C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в преобразовании входной самосинхронизирующейся последовательности импульсов, не требующей дополнительного формирования признака начала информационной посылки, формировании преобразователем кода сигнала стробирования слова, что расширяет функциональные возможности. Преобразователь кода содержит RS-триггеры (1-3, 8), элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (4), элемент ИЛИ-НЕ (9), инвертор (10), формирователь импульса по фронту и срезу (11), счетчики (12, 13), формирователь импульса по фронту (14), элемент И (15), элемент ИЛИ (16), информационный (5) и тактовый (17) входы, информационный (6), тактовый (7) и стробирования (18) выходы. 2 ил.

Преобразователь кода, содержащий первый, второй и третий триггеры, последний из которых является RS-триггером, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, информационные вход и выход, тактовый выход, отличающийся тем, что введены четвертый триггер, элемент ИЛИ-НЕ, инвертор, формирователь импульса по фронту и срезу, первый и второй счетчики, формирователь импульса по фронту, элемент И, элемент ИЛИ, тактовый вход и выход стробирования, первый, второй и четвертый триггеры выполнены в виде RS-триггеров, S-вход последнего из которых соединен с информационным входом преобразователя, R-входом первого счетчика, входами инвертора и формирователя импульса по фронту и срезу, R-вход - с выходом формирователя импульса по фронту и R-входом третьего RS-триггера, а инверсный выход - с первыми входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента ИЛИ-НЕ, второй вход которого соединен с тактовым входом преобразователя, а выход - с тактовыми входами первого и второго счетчиков, R-вход последнего из которых соединен с выходом инвертора, выход второго разряда - со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и S-входом третьего RS-триггера, а выход третьего разряда - с S-входом второго RS-триггера, выход которого соединен с первым входом элемента ИЛИ, а R-вход - с выходом второго разряда первого счетчика, выход третьего разряда которого соединен с S-входом первого RS-триггера, а выход четвертого разряда - с входом формирователя импульса по фронту, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с R-входом первого RS-триггера, выход которого соединен со вторым входом элемента ИЛИ, выход которого соединен с информационным выходом преобразователя, выход формирователя импульса по фронту и срезу соединен с первым входом элемента И, второй вход которого соединен с выходом третьего RS-триггера и выходом стробирования преобразователя, а выход - с тактовым выходом преобразователя.

| Преобразователь кода | 1986 |

|

SU1363476A1 |

| Декодер | 1984 |

|

SU1236615A1 |

| Преобразователь кода Миллера | 1987 |

|

SU1510092A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

Авторы

Даты

2005-08-20—Публикация

2004-03-31—Подача