сл

с

а

СП

00

со

Изобретение относится к измерителной технике и может быть использовано для исследования кратковременных однократных электрических сигналов.

Целью изобретения является повышение эффективности использования памяти путем экономии ее объема.

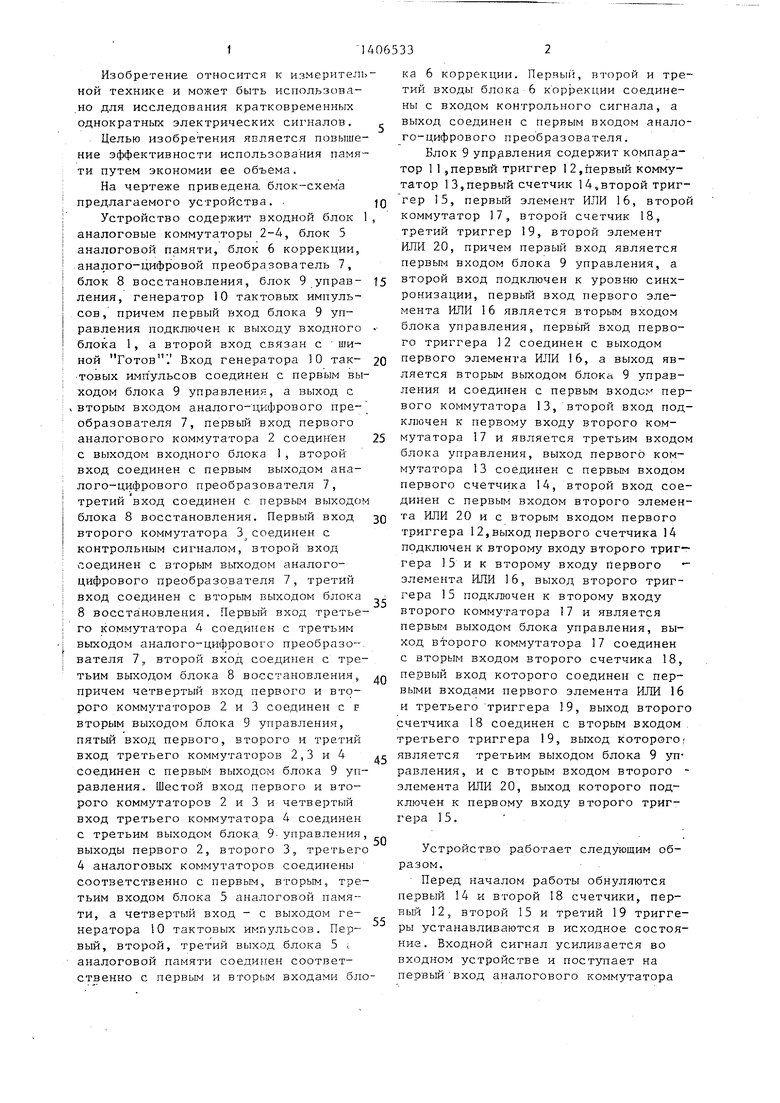

На чертеже приведена блок-схема предлагаемого устройства. .

Устройство содержит входной блок аналоговые коммутаторы 2-Д, блок 5 аналоговой памяти, блок 6 коррекции, аналого-цифровой преобразователь 7, блок 8 восстановления, блок 9 управления, генератор 10 тактовых импульсов, причем первый вход блока 9 управления подключен к выходу входного блока 1, а второй вход связан с шиной Готов . Вход генератора 10 так- Товых импульсов соединен с первым выходом блока 9 управления, а выход с вторым входом аналого-цифрового преобразователя 7, первый вход первого аналогового коммутатора 2 соединен с выходом входного блокгЗ 1 , второй вход соединен с первым выходом аналого-цифрового преобразователя 7, третий вход соединен с первым выходо блока 8 восстановления. Первый вход второго коммутатора 3 соединен с контрольным сигналом, второй вход v-:oeдинeн с вторым выходом аналого- цифрового преобразователя 7, третий вход соединен с вторым выходом блока 8 восста новления. Первый вход третьего коммутатора 4 соединен с третьим выходом аналого-цифрового преобразователя 7, второй вход соединен с третьим выходом блока 8 восстановления, причем четвертый вход первого и второго коммутаторов 2 и 3 соединен с Е вторым выходом блока 9 управления, пятый вход первого, второго и третий вход третьего коммутаторов 2,3 и 4 соединен с первым выходом блока 9 управления. Шестой вход первого и второго коммутаторов 2 и 3 и четвертый вход третьего коммутатора 4 соединен с третьим выходом блока. 9-управления выходы первого 2, второго 3, третьег 4 аналоговых коммутаторов соединенЕ) соответственно с первым, вторым, третьим входом блока 5 аналоговой памяти, а четвертый вход - с выходом генератора 10 тактовых импульсов. Первый, второй, третий выход блока 5 i. аналоговой памяти соединен соответственно с первым и вторым входами бл

0

5

0

5

0

5

0

5

0

5

ка 6 коррекции. Первый, второй и тре- rmi входы блока 6 коррекции соединены с входом контрольного сигнала, а выход соединен с первым входом аналого-цифрового преобразователя.

Блок 9 управления содержит компаратор 1 1 ,первый триггер 12,первый коммутатор 1 3,первый счетчик 14,второй триггер 15, первый элемент ИЛИ 16, второй коммутатор 17, второй счетчик 18, третий триггер 19, второй элемент ИЛИ 20, причем первый вход является первым входом блока 9 управления, а второй вход подключен к уровню синхронизации, первый вход первого элемента ИЛИ 16 является вторым входом блока управления, первЬгй вход первого триггера 12 соединен с выходом первого элемента ИЛИ 16, а выход является вторым выходом блока 9 управления и соединен с первым входом первого коммутатора 13, BTOpoii вход подключен к первому входу второго коммутатора 17 и является третьим входом блока управления, выход первого коммутатора 13 соединен с первым входом первого счетчика 14, второй вход соединен с первым входом второго элемента ИЛИ 20 и с вторым входом первого триггера 1 2, выход первого счетчика 14 подключен к второму входу второго триггера 15 и к второму входу первого элемента ИЛИ 16, выход второго триггера 15 подключен к второму входу второго коммутатора 17 и является первьв выходом блока управления, выход второго коммутатора 17 соединен с вторым входом второго счетчика 18, первый вход которого соединен с первыми входами первого элемента ИЛИ 16 и третьего триггера 19, выход второго счетчика 18 соединен с вторым входом . третьего триггера 19, выход которого является третьим выходом блока 9 управления, и с вторым входом второго - элемента ИЛИ 20, выход которого подключен к первому входу второго триггера 15.

Устройство работает следующим образом.

Перед началом работы обнуляются первый 14 и второй 18 счетчики, первый 12, второй 15 и третий 19 триггеры устанавливаются в исходное состояние. Входной сигнал усиливается во входном устройстве и пост ттает на первьй вход аналогового коммутатора

2, на другой вход которого поступает контрольный сигнал калиброванной амплитуды,. При превьпиении входным сигналом уровня синхронизации компара-(, тор 11 вырабатывает импульс, который лереводит триггер 12 в единичное состояние, подключая тем самым исследуемый и контрольный сигнал на вход блока 5 аналоговой памяти. Сигнал с пер вого триггера 12 разрешает прохождение импульсов записи с генератора 10 тактовых импульсов через первый коммутатор 13 на вход первого счетчика 14. Емкость первого счетчика 14 равна емкости блока 5 аналоговой памяти. Импульс переполнения первого счетчика 14 поступает на вход второго триггера 15 и переводит его в единичное состояние, а также поступает на вход первого триггера 12 через первый элемент ИЛИ 16 и переводит его в нулевое состояние. На этом заканчивается процесс быстрой записи мгновенных значений исследуемого сигнала в аналого- вом виде в аналоговую память блока 5. Выход второго триггера 15 подключен к управляющим входам аналоговых коммутаторов, обеспечивая тем самым подключение выходов аналого-цифрового преобразователя 7 к соответствующим входам блока 5 аналоговой памяти. Одновременно с этим сигнал с второго триггера 15 поступает на генератор 10 тактовых импульсов, который начинает вырабатывать frcuMTС данного момента времени начинается процесс медленного считывания из блока 5 аналоговой памяти, корректирования в блоке 6 коррекции, преоб- разования в код АЦП 7 и запись в ту же аналоговую память.

Одновременно с началом считывания информации сигналом с второго триггера 15 разрещается прохождение импуль- сов считывания через второй коммута- тор 17 на вход второго счетчика 18. Емкость второго счетчика 18 равна емкости аналоговой памяти. ,

Импульс переполнения второго счетчика 18 поступает на вход третьего триггера 19 и устанавливает его в единичное состояние, а также поступает на вход второго триггера 1.5 через второй элемент ИЛИ 20 и переводит его в нулевое состояние. Выход третьего триггера 19 подключен к управляющим входам первого 2, второго 3, третьего 4 аналоговых коммутаторов, чем

0

5 0 5 зО

Q

5 .

50

5

обеспечивается прохождение информации .с выхода блока 5 аналоговой памяти через блок 8 восстановления, выполняющий функцию восстановления логических уровней для записи обратно в аналоговую память блока 5.

Таким образом, информация, считываемая из блока 5 аналоговой памяти, замыкается в кольцо, обеспечивая циркуляцию кода, записанного сигнала и его циклический вывод.

Формула Изобретения

1. Устройство для регистрации формы однократных электрических сигналов, содержащее входной блок, блок управления, аналого-цифровой преобразователь, генератор тактовых импульсов, вход которого соединен с первым выходом блока управления, а выход - с вторым входом аналого-цифрового преобразователя, отличающее- с я тем, что, с целью повьщ1ения эффективности, оно содержит три аналоговых коммутатора, блок во12становле- ния, блок коррекции, блок аналоговой памяти, причем первый вход первого аналогового коммутатора соединен с выходом входного блока, второй вход соединен с первым выходом аналого- цифрового преобразователя, а четвертый, пятый и шестой входы подключены к второму, первому и третьему выходам блока управления соответственно, первый вход второго аналового коммутатора соединен с щиной контрольного сигнала, второй вход соединен с вторым выходом аналого-цифрового преобразователя, а четвертый, пятьш и шестой входы подключены к- второму, первому и третьему выходам блока управления соответственно, первый вход третьего аналогового коммутатора соединен с третьим выходом аналого-цифрового преобразователя, а третий и четвертый входы подключены к первому и третьему выходам блока управления соответственно, выходы аналоговых коммутаторов соединены с соответствующими входами блока аналоговой памяти, входы блока восстановления соединены с соответствующими выходами блока аналоговой памяти, а выходы подключены соответственно к третьим входам первого и второго аналоговых коммутаторов и к второму входу третьего аналогового коммутатора и являются выходами устройства, первый вход блока коррекции соединен с шиной контрольного сигнала, второй вход блока коррекции соединен с первым выходом блока аналоговой памяти, третий вход которого соединен с вторым выходом блока аналоговой памяти, а выход является первым входом аналого-цифрового преобразователя.

2., Устройство по п. 1, отличающееся тем, что блок управления содержит три триггера, два элемента ИЛИ, два счетчика, два коммута- тора, компаратор, первый вход которого соединен с шиной синхронизации, а второй вход является первым входом блока управления, первый вход первого элемента ИЛИ является вторым входом блока управления, первый вход первого триггера соединен с выходом первого элемента ИЛИ, а выход является вторым выходом блока управления, первый вход первого коммутатора подключен к вы-

5 5

0

ходу первого триггера, второй вход подключен к первому входу второго коммутатора и является третьим входом блока управления, а выход - с первым входом первого счетчика, второй вход которого соединен с первым входом второго элемента ИЛИ и с вторым входом первого триггера, выход первого счетчика подключен к второму входу второго триггера и к второму входу первого элемента ИЛИ, а выход второго триггера подключен к второму входу второго коммутатора и является первым входом блока управления, выход второго коммутатора соединен с вторым входом второго счетчика, первый вход которого соединен с первыми входами второго счетчика и третьего триггера, а выход второго счетчика соединен с вторым входом третьего триггера, выход которого является третьим выходом блока управления, и с вторым входом второго элемента ИЛИ, выход которого подключен к первому входу второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации формы однократных электрических сигналов | 1988 |

|

SU1492313A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Анализатор спектра | 1988 |

|

SU1567992A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Программируемый трансверсальный фильтр | 1988 |

|

SU1651354A1 |

| Устройство корреляционной обработки широкополосных сигналов | 1988 |

|

SU1619414A1 |

Изобретение относится к области измерительной техники. Устройство для регистрации формы однократных электрических сигналов содержит входной блок 1 , блок 9 управления, аналого-цифро-: вой преобразователь 7, генератор 10 тактовых импульсов, блок 8 восстановления, блок 6 коррекции, блок 5 аналоговой памяти. Блок 9 управления содержит триггеры 12,15,19, элементы ИЛИ 16,20, счетчики 14,18, коммутаторы 13, 17 и компаратор П. Устройство имеет повышенную эффективность использования памяти путем экономии ее объема. 1 з.п. ф-лы, 1 ил.

| Е.И | |||

| Рехин и др | |||

| Измерение одно- | |||

| кратных сигналов в современной ядерной физике | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

Авторы

Даты

1988-06-30—Публикация

1986-12-30—Подача