Изобретение относится к измерительной технике и может быть использовано для исследования кратковременных однократных электрических сигналов.

Целью изобретения является повышение точности регистрации однократных электрических сигналов.

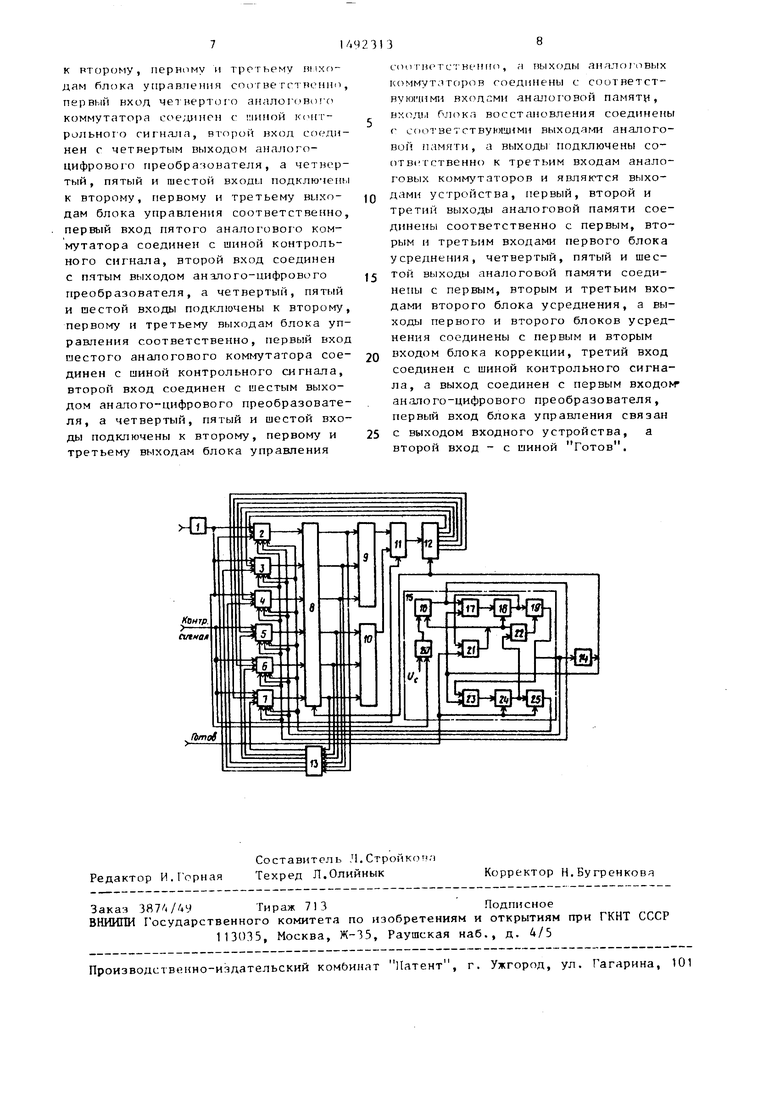

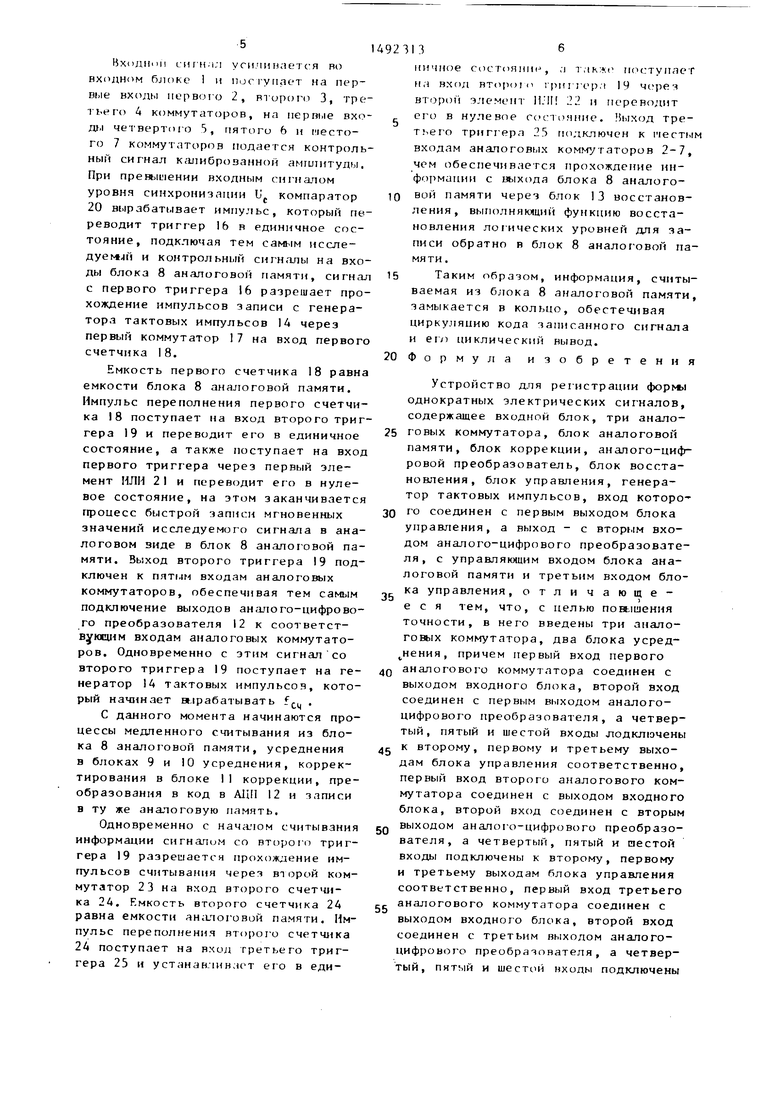

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит блок 1, ана- лог овые коммутаторы 2-7, блок 8 аналоговой памяти, первый 9 и второй 10 блоки усреднения, блок 11 коррекции.

аналого-цифровой преобразователь 12, блок 13 восстановления, генератор 14 тактовых импульсов, блок 15 управления, причем первый вход блока 15 управления подключен к выходу входного блока I, а второй вход связан с шиной Готов, вход генератора 14 тактовых импульсов соединен с первым выходом блока управления, а выход - со вторым входом аналого-цифрового преобразователя 12, первый вход первого аналогового коммутатора 2 соединен с выходом входного блока 1, второй вход соединен с первым выхо

14423

HDM ,)н;июго-1,мфр| вого иреобрлчоплтеjiK 12, третий вход соединен с перв1.гм яь:.чс1дпм блока 13 восстановления, ;ie;ja:,m вход второго xoMNryTaTopa 3 coe:ii .neH с выходом входного блока 1 , вторс й вход - с вторым выходом аналого-цифрового преобразователя 12, третий вход - с вторым выходом блока 13 восстановления. Первый вход третьего коммутатора 4 соединен с выходом входного блока 1, второй вход - с третьим выходом аналого- цифрового преобразователя 12, третий вход - с третьим выходом блока 13 восстановления, первый вход четвертого коммутатора 5 соединен с контрольным сигналом, второй вход - с четвертым выходом аналого-цифрового преобразователя 12, третий вход - с четвертым выходом блока 13 восстановления, первый вход пятого коммутатора 6 соединен с контрольным сиг- напом, второй вход - с пятым выходом аналого-цифрового преобразователя 12 третий вход - с пятым выходом блока 13 восстановления, первый вход шестого коммутатора 7 соединен с контрольным сигналом, второй вход - с шестым выходом аналого-цифрового пре образователя 12, третий вход - с шестым выходом блока 13 восстановления, причем четвертый, пятый и шестой входы первого 2, второго 3, третьего 4, четвертого 5, пятого 6 и шестого 7 коммутаторов соединены с вторым, первым и третьим выходами блока 15 управления, выходы первого 2, второго 3, третьего 4, четвертого 5, пятого 6, шестого 7 коммутато- ров соединены соответственно с первым, вторым, третьим, четвертым, пятым, иестым входами блока 8 аналоговой памяти, а седьмой вход - с выходом генератора 14 тактовых импуль- сов, первый, второй, третий выходы блока 8 аналоговой памяти соединены с первым, вторым, третьим входами первого блока 9 усреднения, а четвертый, пятый, иестой выходы блока 8

аналоговой памяти соединены с первым, вторым, третьим входами второго блока 10 усреднения соответственно, выход первого блока 9 усреднения соединен с первым входом блока 11 кор- рекции, яыход второго блока 10 усреднения соединен с вторым входом блока 1i коррекции, третий вход бля ка коррекции соединен с входом

Q 5 0 5 0 0

0

s

13

контрольного сигнала, а выход - с первым входом аналого-цифрового npi обрак нателя 12. I

Блок 15 управления С(здержит (фиг. I) первый триггер 16, первый коммутатор 17, первый счетчик 18, второй тригтер 19, компаратор 20, первый элемент ИЛИ 2I, второй элемент SM 22, второй коммутатор 23, второй счетчик 24, третий триггер 25, причем первый вход компаратора 20 является первым входом блока 15 управления, второй вход соединен с шиной синхронизации, а выход - со вторым входом первого триггера 16, первый вход первого элемента ИЛИ 21 является вторым входом блока 15 управления, первый вход первого триггера 16 соединен с выходом первого элемента ИЛИ 21, а выход является вторым выходом блока 15 управления, первый вход первого коммутатора подключен к выходу первого триггера 16, второй вход - к первому входу второго коммутатора 23 и является третьим входом блока 15 управления, а выход соединен с первым входом первого счетчика 18, второй вход которого соединен с первым входом второго элемента ИЛИ 22 и с первым входом первого триггера 16, выход первого счет- чика 18 подключен ко второму входу второго триггера и ко второму входу первого элемента ИЛИ 21, а выход второго триггера 19 подключен ко второму входу второго коммутатора 23 и является первым выходом блока 15 управления, а выход второго коммутатора 23 соединен с вторым входом второго счетчика 24, первый вход которого соединен с первыми входами третьего триггера 25 и первого эдемента ИЛИ 21, а выход второго счетчика 24 соединен со вторым входом третьего триггера 25, выход которого является третьим выходом блока 15 управления, и со вторым входом второго элемента ИЛИ 22, выход которого подключен к первому входу второго триттера 19.

Устройство работает следуквдим об- рачом.

Перед началом работы обнуляется первый 18 и второй 24 счетчики, пер- ш,1Й 16, второй 19 и третий 25 три1- геры устанаапиваются в исходное состояние .

Вх |Д1111М СИГ-Ц.1Л усилинаетс я во нхидном блоке 1 и nori-упас т на первые вхсды первог о 2, второго 3, третье г-о 4 к()ммутат }ров, на iiepni.ie вхо- ZU.i четвертого 5, пятого 6 и шестого 7 коммутаторов подается контрольный сигнал Ксчлиброванной амгиштуды, При превыи1ении входным сигналом уровня синхронизации Ь компаратор 20 вырабатывает импульс, который переводит триггер 16 в единичное состояние, подключая тем самым иссле- дуег« й и контрольный сигналы на входы блока 8 аналоговой памяти, сигнал с первого триггера 16 разрешает прохождение импульсов записи с генератора тактовых импульсов 14 через первый коммутатор 17 на вход первого счетчика 18.

Емкость первого счетчика 18 равна емкости блока 8 аналоговой памяти. Импульс переполнения первого счетчика 18 поступает на вход второго триггера 19 и переводит его в единичное состояние, а также поступает на вход первого триггера через первый элемент ИЛИ 2I и переводит его в нулевое состояние, на этом заканчивается процесс быстрой записи мгновенных значений исследуемого сигнала в аналоговом виде в блок 8 аналоговой памяти. Выход второго триггера 19 подключен к пятым входам аналоговых коммутаторов, обеспечивая тем самым подключение выходов ан 1лого-цифрового преобразователя 12 к соответст- вукядим входам аналоговых коммутаторов. Одновременно с этим сигнал со второго триггера 19 поступает на генератор 14 тактовых импульсоя, который начинает В1,|рабатывать 5, .

С данного момента начинаются процессы медленного считывания из блока 8 аналоговой памяти, усреднения в блоках 9 и 10 усреднения, корректирования в блоке II коррекции, преобразования в код в Alill 12 и записи в ту же аналоговую память.

Одновременно с нача-юм считывания информации сигналим со второго триггера 19 разрешается прохождение импульсов считывания через в1орой коммутатор 23 на вход второго счетчика 24. Кмкость второго счетчика 24 равна емкости ангшоговой памяти. Импульс переполнения второго счетчика 24 поступает на вход третьего триггера 25 и устанав:1инаот его в еди10

15

25

923136

иичное состояние, ,-j т.чкже гитступает на вход второго григ)-ор,-| 19 Ч1 рез второй элемент ИЛИ 22 и переводит его в нулевое сс-спонние. Выход третьего тригг ерл 25 подключен к I lecTt.iM входам аналоговых коммутаторов 2-7, чем обеспечивается прохождение информации с выхода блока 8 аналоговой памяти через блок 13 восстановления, ВЫПОЛНЯЮЩИЙ функцию восстановления лог ических уровней для записи обратно в блок 8 аналоговой памяти .

Таким образом, информация, считываемая из блока 8 аналоговой памяти, замыкается в кольцо, обестечлвая циркуляцию кода записанного сигнала и eiv) циклический вывод. 20 Форму л а изобретения

Устройство для регистрации однократных электрических сигналов, содержащее входной блок, три аналоговых коммутатора, блок аналоговой памяти, блок коррекции, аналого-цифровой преобразователь, блок восстановления, блок управления, генератор тактовых импульсов, вход которо го соединен с первым выходом блока управления, а выход - с вторым входом аналого-цифрового преобразователя , с управляющим входом блока аналоговой памяти и третьим входом блока управления, отличающееся тем, что, с целью повь1шения точности, в него введены три аналоговых коммутатора, два блока усред- нения, причем первый вход первого аналогового коммутатора соединен с выходом входного блока, второй вход соединен с первым выходом аналого- цифрового преобразователя, а четвертый, пятый и шестой входы лодключены к второму, первому и третьему выходам блока управления соответственно, первый вход второго аналогового коммутатора соединен с выходом входного блока, второй вход соединен с вторым выходом аналого-цифрового преобразователя, а четвертый, пятый и шестой входы подключены к второму, первому и третьему выходам блока управления соответственно, первый вход третьего аналогового коммутатора соединен с выходом входного блока, второй вход соединен с третьим выходом аналого- цифрового преобразователя, а четвертый, пятый и шест1Ж входы подключены

30

35

40

45

50

55

к рторому, перному и третьему niixn- дам управления соитвегствешм, первый ьход четвертог о аналоговшч коммутатора сое; 1инен с шимой

рольног о гигнала, второй вход соединен с четвертым выходом аналого- цифрового преобразователя, а четвертый, пятый и шестой входь подключены к второму, первому и третьему ныхо- дам блока управления соответственно, первый вход пятого аналогового коммутатора соединен с шиной контрольного сигнала, второй вход соединен с пятым выходом аналого-цифрового

преобразователя, а четвертый, пятый и шестой входы подключены к второму, первому и третьему выходам блока управления соответственно, первый вход шестого аналогового коммутатора сое- динен с шиной контрольного сигнала, второй вход соединен с шестым выходом аналого-цифрового преобразователя, а четвертый, пятый и шестой входы подключены к второму, первому и третьему выходам блока управления

c(U) гнетс гнешк, а выходы анало1 овых коммут;1торов соединены с соответст- вуклцими входсми аналоговой памяти, ВХОД1.1 Г1ЛОКЛ восстановления соединены г с(1ответствуи)гдими выходаг-ш аналоговой памяти, а выходы подключены соответственно к третьим входам аналоговых коммутаторов и являются выходами устройства, первый, второй и третий выходы аналоговой памяти соединены соответственно с первым, вторым и третьим входами первого блока усреднения, четвертый, пятый и шестой выходы аналоговой памяти соединены с первым, вторым и третьим входами второго блока усреднения, а выходы первого и второго блоков усреднения соединены с первым и вторым входом блока коррекции, третий вход соединен с шиной контрольного сигнала, а выход соединен с первым входок аналого-цифрового преобразователя, первьй вход блока управления связан с выходом входного устройства, а второй вход - с шиной Готов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации формы однократных электрических сигналов | 1986 |

|

SU1406533A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство для регистрации однократных процессов | 1980 |

|

SU959111A1 |

| Устройство для определения содержания органических примесей в воде | 1990 |

|

SU1804624A3 |

| Многоканальный коммутатор аналоговых сигналов | 1988 |

|

SU1598149A1 |

| Устройство сигнатурной проверки аналого-цифровых преобразователей | 1979 |

|

SU790293A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

Изобретение относится к измерительной технике и может быть использовано для исследования кратковременных однократных электрических сигналов. Цель изобретения - повышение точности регистрации однократных электрических сигналов. Входной сигнал усиливается во входном устройстве и поступает на первые входы первого, второго и третьего коммутаторов, на первые входы четвертого, пятого и шестого коммутаторов подается контрольный сигнал калиброванной амплитуды. Исследуемый и контрольный сигналы подключаются на входы аналоговой памяти. Далее начинается процесс медленного считывания из аналоговой памяти, усреднения в блоках усреднения, корректирования в блоке коррекции, преобразования в код в АЦП и записи в ту же аналоговую память. Таким образом, информация, считываемая из аналоговой памяти, замыкается в кольцо, обеспечивая циркуляцию кода записанного сигнала и его циклический вывод. 1 ил.

| Рехин Е.И | |||

| и др | |||

| Измерение однократных сигналов в современной ядернор физике | |||

| - М | |||

| : Энергоатомиз- дат, 1983 | |||

| Устройство для регистрации формы однократных электрических сигналов | 1986 |

|

SU1406533A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-07-07—Публикация

1988-01-11—Подача