1 Изобретение относится к вычислительной технике и может быть использовано .при построении двоично-десятичных арифметических устройств.

Известно устройство умножения, содержащее регистр множимого, блок последовательного накопления чисел, кратных множимому, блок сдвига, блок суммирования частичных произведений, регистр множителя, блок определения цифр 1 .

Однако известное устройство сложно .

Наиболее близким к предлагаемому является устройство, содержащее десятичный сумматор, регистр-преобразователь, информационные разрядные выходы которого подключены к информационным входам сумматора, регистр множимого, информационные выходы которого подключены к информационным входам старших десятичных разр5здов регистра-преобразователя, информационные выходы младших десятичных разрядов которого подключены к информационным входам регистра множимого, регистр множителя и блок управления, выход сложения которого подключен ко входу сложения десятичного сумматорь, выход преобразования блока управлёния поДсоед инен к первому управляющему входу регистра-преобразователя, второй управляющий вход которого соединен со входом сдвига регистра множителя и с выходом управления сдвигом блока управления, выход управления приемом которого подсоединен ко входу приема в регистр множимого

L2.

0

Недостаток данного устройства большое время выполнения операции (каждая десятичная цифра множителя обрабатывается за четыре такта). Цель изобретения - увеличение

5 быстродействия устройства.

Поставленная цель достигается тем, что в устройство для умножения десятичных чисел, содержащее десятичный сумматор, преобразователь двоичного

0 кода в двоично-десятичный, информационные выходы десятичных разрядов которого подключены к информационным разрядным входам десятичного сумматора, регистр множимого, информационные разрядные выходы которого подключены к информационным входам старших десятичных разрядов преобразователя двоичного кода в двоичнодесятичный, информационные выходы

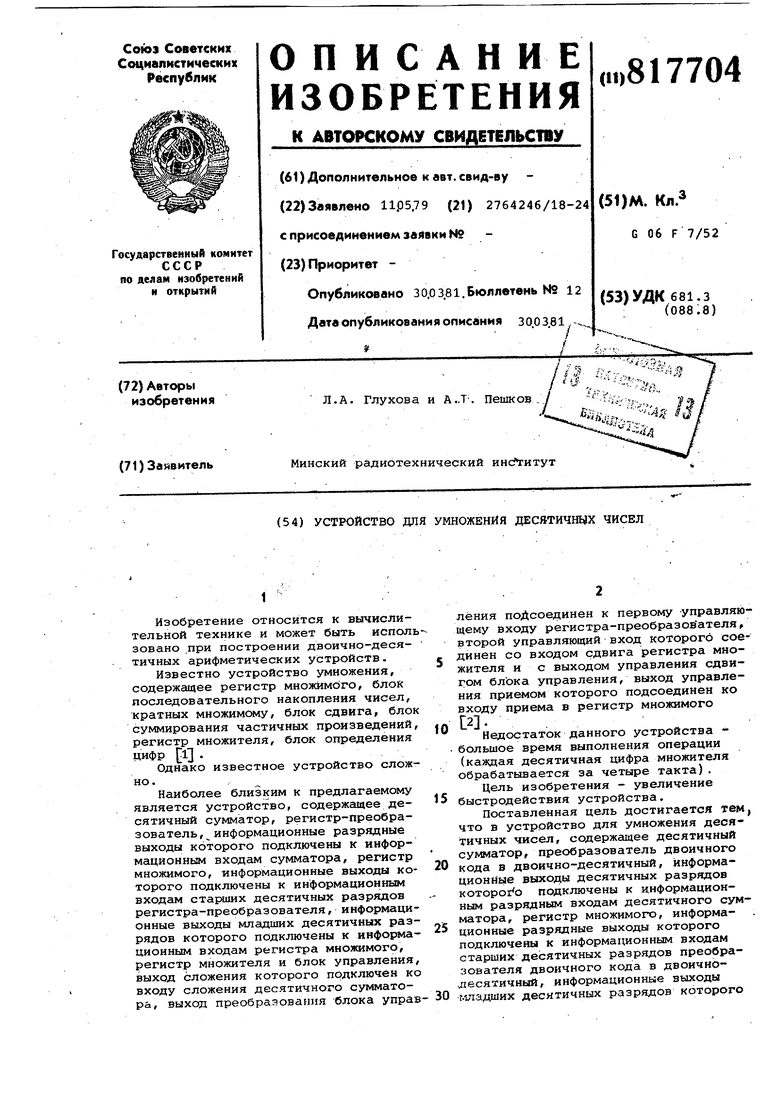

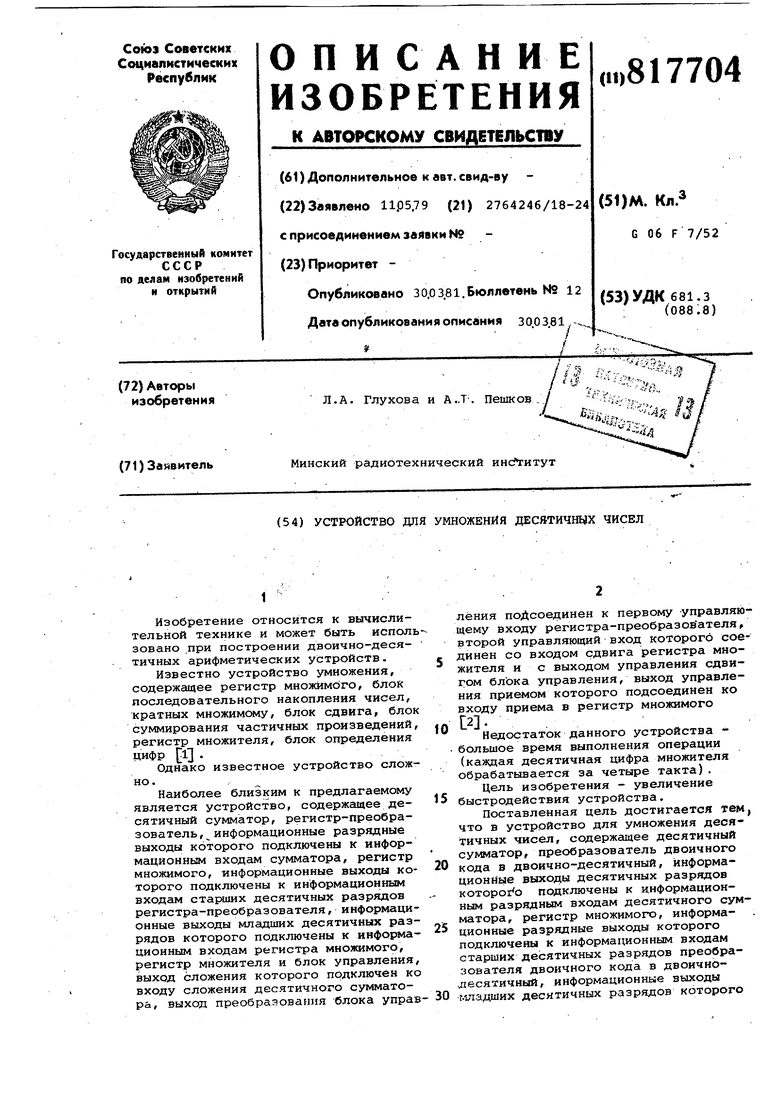

0 младших десятичных разрядов которого подсоединены к информационным разряд ным входам множимого, регистр множителя и блок управления, выход уп сложением которого подключен ко входу сложения десятичного сумматора, выход управления преобразованием блока управления подсоединен к первому управляющему входу преобразователя двоичного кода в . двоично-десятичный, второй управляющий вход которого соединен со входом сдвига регистра множителя и с выходом управления сдвигом блока управления, выход управления приемом которого подсоединен ко входу приема регистра множимого, дополнительно введен узел преобразования цифры выход з.нака которого соединен с входом управления видом операции десятичного сумматора и со входом знака блока управления, разряды информационного входа которого с весами 4, 2 и 1 подключены к разрядам информационного выхода узла преобразования цифры с весами 4, 2 и 1, разряды информационного входа с весами 8, 4, 2 и 1 которого подсоединены к разрядам выхода младшего десятичного разряда регистра множителя, к младшему разряду регистра множителя подключен выход . прибавления единицы блока управления. Узел преобразования цифры содер жит элемент НЕ, элемент И и элемен ИЛИ, первый вход которого подключен к выходу элемента И, первый вход ко торого подсоединен к выходу знака и к разряду веса 8 информационного входа узла преобразования цифры,вто рой вход элемента И через.элемент Н соединен с разрядом веса 1 информационного входа узла преобразования цифры, разряд веса 2 которого подключен ко второму входу элемента ИЛИ, вход элемента НЕ, выход элемента ИЛИ и разряд веса 4 информа ционного входа узла преобразования цифры соединены соответственно с разрядами весов 1, 2 и 4 инфо мационного выхода узла преобразования цифры. Кроме того, блок управле ния, содержит генератор тактов, счет ч-ик, семь элементов И, элемент НЕ и элемент ИЛИ, причем выход генератора соединен со счетным входом сче чика и с первыми входами элементов И, вторые входы первого, второго , и третьего элементов И подключены соответственно к трем разрядам с весами 1, 2., 4 информационного входа блока управления, выходы четвертого, пятого, шестого и седьмого элементов И являются соответст венно выходами управления преобразо ванием, сдвигом, приемом, прибавлением единицы блока управления, третьи входы первого, второго и третьего элементов И соединены соот ветственно с первым, вторым и треть ыходами счетчика, второй вход пятоо элемента И соединен с третьим ыходом и с установочным входом счетика, вторые входы шестого и седьмоо элементов И подключены к первому ыходу счетчика, третий вход седьмоо элемента И подключен к входу знаа блока управления, выход пятого элемента И соединен со входом элеента НЕ, выход которого подключен о второму входу четвертого элемена И, выходы первого, второго и третьего элементов И соединены со входами элемента ИЛИ, выход которого является выходом сложения блока управления. На фиг. 1 представлена структурная схема устройства для умножения десятичных чисел; на фиг. 2 - схема узла преобразования цифры; на фиг.З- cxebte блока управления. Устройство (фиг. 1) содержит десятичный сумматор 1, содержащий 2п десятичных разрядов, где п.разрядность десятичных операндов, преобразователь 2, содержащий 2п десятичных разрядов, информационные выходы которого подключены к информационным входам сумматора, данный блок представляет собой регистр сдвига с цепями коррекции, необходимыми для умножения десятичного числа на два, и служит для последовательного получения во время выполнения умножения необходимых кратных множимого, в качестве преобразователя может быть использован преобразователь двоичного кода в Двоично-десятичный, регистр 3 множимого, содержащий 2п-1 десятичных разрядов, входы которого подключены к выходам младших разрядов регистра-преобразователя, а выходы - ко входам старших разрядов его регистр 4 множителя, содержащий п+1 десятичный разряд,причем стар- . шие п выполнены в виде десятичных, счетчиков,-узел 5 преобразования цифры, четырехразрядный информационный вход которого подключен к выходу младшего десятичного разряда регистра 4, а выход знака - ко входу управления видом операции десятичного сумматора, блок б управления, вход 7знака которого соединен с выходом знака узла 5, трехразрядный информационный выход которого соединен с трехразрядным информационным входом 8.блока 6, выход 9 управления сложением, которого подключен ко входу сложения сумматора 1, выход 10 .преобразования блока управления соединен с первым управляющим входом преобразователя 2, второй управляющий вход которого подсоединен к выходу 11 управления сдвигом блока управления, выход 12 управления, приемом которого соединен со входом приема регистра 3, выход 13 управления прибавлением единицы блока управления

подключен ко входу прибавления единицы к следующему разряду регистра 4, вход сдвига которого соединен с выходом 11 блока 6.

Назначением узла 5 преобразования цифры является анализ значения младшего десятичного разряда регистра 4 Если в нем находится любая из цифр от 0000 до 0111 (от О до 7)-, то узел 5 осуществляет прямую передачу содержимого трех младших двоичных разрядов младшего десятичноог-о разряда регистра 4 на свой трехразрядный информационный выход, а на выходе знака узла 5 появляется.сигнал О ( + ) . Если же в младшем десятичт ном разряде регистра 4 находится цифра 1000 или 1001 (3 или 9), то на информационном выходе узла 5 появляется соответственно код 010 или 001, а на выходе - сигнал 1 (-).

Устройство работает следующим образом.

Перед началом умножения в регистр 4 заносится код множителя, в младшие разряды регистра-преобразователя 2 - код множимого, множимое и множитель представлены в коде 8-4-2-1. Умножение выполняется за число циклов, равное п+1, начиная с младшего десятичного разряда множителя .Каждый цикл состоит из трех тактов (по числу двоичных разрядов представления десятичной цифры на информационном выходе узла 5).

На первом такте первого цикла блок б управления анализирует значение знака на своем входе 7 и значение двоичного разряда веса 1 своего информационного входа 8. Если на вход 7 поступает знак минус, то блок управления формирует сигнал на выходе 13, покоторому осуществляется прибавление единицы в соседний с младшим десятичный разряд регистра 4 Если двоичный разряд веса 1 на входе 8 блока управления равен единице, то блок управления формирует сигнал на выходе 9, по которому осуществляется прибавление либо вычитание, в зависимости от знака поступившего с выхода знака узла 5 на вход управления видом операции десятичного сумматора 1, содержимого регистра-преобразователя 2 к содержимому сумматора 1. Одновременно с формированием сигнаша на выходах 9 и 13 блок управления -вырабатывает сигналы на выходах 10 и 12. Сигнал о выхода 12 поступает на вход приема регистра 3 множимого и обеспечивает запоминание его содержимого. Сигнал с выхода 10 управляет умножением на два содержимого регистра-преобразователя 2.

Таким обраэ-ом, к началу второго такта цикла в преобразователе 2 сформирован код двухкратного множимого

На втором такте блок управления анализирует разряд веса 2 своего информационного входа 8. Если, на нем 1, то блок управления вырабатывает сигнална выходе 9, по кото, рому выполняется прибавление или вычитание, в зависимости от сигнала на выходе знака узла 5, содержимого преобразователя 2 к содержимому сумматора 1. Одновременно формируется -р сигнал на выходе 10 блока управления, по которому в преобразователе 2 производится удвоение его содержимого (формирование четырехкратного множимого) . .

На третьем такте блок управле5 ния анализирует разряд веса

4 своего информационного входа, . и если на нем 1, то формирует сигнал на выходе 9, обеспечив прибавление содержимого преобразователя к содержимому сумматора. Одновременно вырабатывается сигнал на выходе 11 блока управления, по которому в преобразователь 2 принимается содержимое регистра 3, т.е. к началу следующего 25 цикла в регистре 2 установлено множимое, сдвинутое на один.десятичный разряд 5лево и выполняется сдвиг на один десятичный разряд вправо содер- жимого регистра множителя. На этом выполнение первого цикла закончено-.Все остальные циклы выполняются аналогично. Умножение заканчивается после обработки (п+1)-ой цифры множителя. I . ,

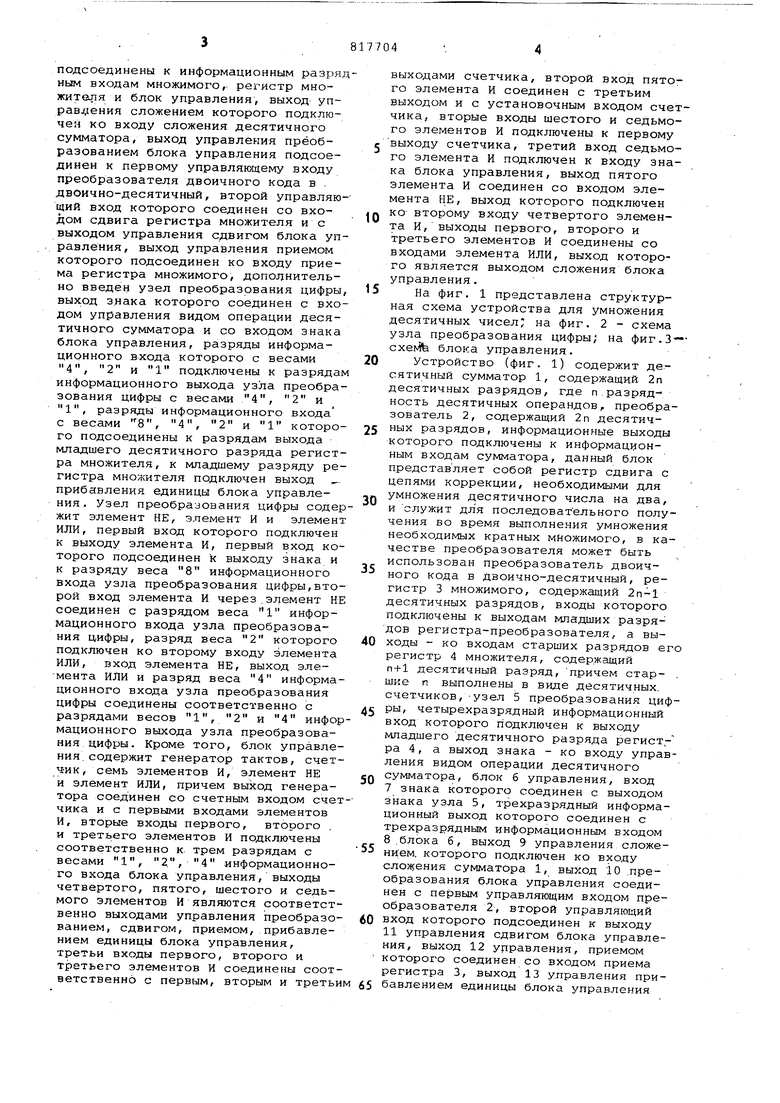

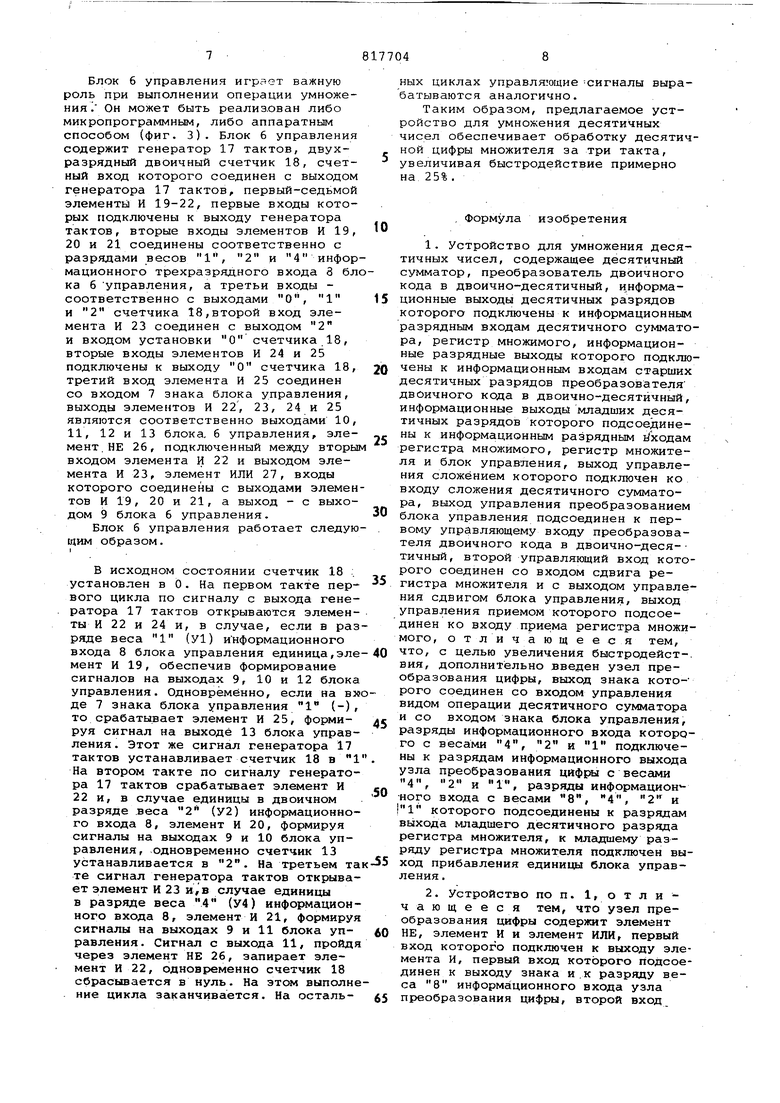

р Схема узла 5 преобразования цифры (фиг. 2) содержит элемент и 14, первый вход которого соединен с двоичным разрядом веса 8 .(Х8) информационного входа и выходом знака узла 0 преобразования цифры (S); элемент НЕ 15, вход которого соединен с двоичными разрядами веса 1 четырехразрядного информационного входа () и тpexpaзpяднo.p информационного выхода 5 (У1) узла 5, а йыход - со вторым

входом элемента И 14, элемент ИЛИ 16, первый вход которого подключен к вы ходу элемента И 14, а второй вход и

выход соединены соответственно с двол ичными разрядами веса 2 четырехраз- рядного информационного входа (Х2) и трехразрядного информационного вы-хода (У2).узла 5, двоичный разряд веса 4 информационного входа (Х4) которого соединен с пвоичным разря - дом веса 4 информационного выхода (У4) узла 5.

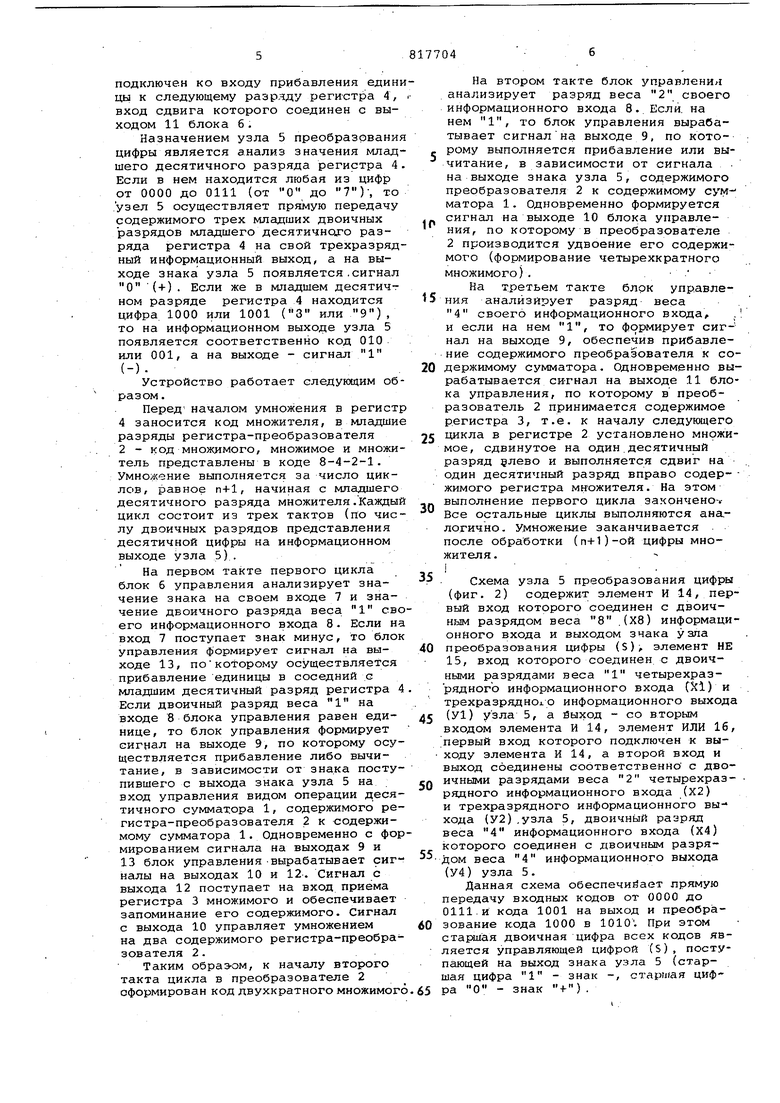

Данная схема обеспечивает прямую передачу входных кодов от 0000 до 0111.и кода 1001 на выход и преобразование кода 1000 в 1010. При этом старшая двоичная цифра всех кодов является управляющей цифрой (S), поступающей на выход знака узла 5 (старшая цифра 1 - знак -, старшая цифра О - знак Ч). Блок 6 управления играет важную роль при выполнении операции умножения i Он может быть реализован либо микропрограммным, либо аппаратным способом (фиг. 3). Блок 6 управления содержит генератор 17 тактов, двухразрядный двоичный счетчик 18, счетный вход которого соединен с выходом генератора 17 тактов, первый-седьмой элементы И 19-22, первые входы которых подключены к выходу генератора тактов, вторые входы элементов И 19, 20 и 21 соединены соответственно с разрядами весов 1, 2 и 4 инфор мационного трехразрядного входа 8 бл ка 6 управления, а третьи входы соответственно с выходами О, 1 2 счетчика 18,второй вход элемента И 23 соединен с выходом 2 и входом установки О счетчика 18, вторые входы элементов И 24 и 25 подключены к выходу О счетчика 18, третий вход элемента И 25 соединен со входом 7 знака блока управления, выходы элементов И 22, 23, 24 и 25 являются соответственно выходами 10, 11, 12 и 13 блока, 6 управления, элемент. НЕ 26, подключенный между вторы входом элемента И 22 и выходом элемента И 23, элемент ИЛИ 27, входы которого соединены с выходами элемен тов И 19, 20 и 21, а выход - с выходом 9 блока 6 управления. Блок б управления работает следую щим образом. в исходном состоянии счетчик 18 .. установлен в (Э. На первом такте первого цикла по сигналу с выхода генератора 17 тактов открываются элементы И 22 и 24 и, в случае, если в раз ряде веса 1 (У1) информационного входа 8 блока управления единица,эле мент И 19, обеспечив формирование сигналов на выходах 9, 10 и 12 блока управления. Одновременно, если на вх де 7 знака блока управления 1 {-) то срабатывает элемент И 25, формируя сигнал на выходе 13 блока управления. Этот же сигнал генератора 17 тактов устанавливает счетчик 18 в 1 На втором такте по сигналу генератора 17 тактов срабатывает элемент И 22 и, в случае единицы в двоичном разряде веса 2 (У2) информационно го входа 8, элемент И 20, формируя сигналы на выходах 9 и 10 блока управления, -одновременно счетчик 13 На третьем т устанавливается в те сигнал генератора тактов открыва ет элемент И 23 и,в случае единицы в разряде веса 4 (У4) информацион ного входа 8, элемент И 21, формиру сигналы на выходах 9 и 11 блока управления. Сигнал с выхода 11, пройд через элемент НЕ 26, запирает элемент И 22, одновременно счетчик 18 сбрасывается в нуль. На этом выполн ние цикла заканчивается. На остальных циклах управляющие сигналы выраатываются аналогично. Таким образом, предлагаемое устройство для умножения десятичных чисел обеспечивает обработку десятичной цифры множителя за три такта, увеличивая быстродействие примерно на 25%. , формула изобретения 1. Устройство для умножения десятичных чисел, содержащее десятичный сумматор, преобразователь двоичного кода в двоично-десятичный, информационные выходы десятичных разрядов которого подключены к информационным разрядньом входам десятичного сумматора, регистр множимого, информационные разрядные выходы которого подключены к информационным входам старших десятичных разрядов преобразователя двоичного кода в двоично-десятичный, информационные выходи младших десятичных разрядов которого подсоединены к информационным разрядным входам регистра множимого, регистр множителя и блок управления, выход управления сложением которого подключен ко входу сложения десятичного сумматора, выход управления преобразованием блока управления подсоединен к первому управляющему входу преобразователя двоичного кода в двоично-деся- тичный, второй управляющий вход которого соединен со входом сдвига регистра множителя и с выходом управления сдвигом блока управления, выход управления приемом которого подсоединен ко входу приема регистра множимого, отличающееся тем, что, с целью увеличения быстродейст-. ВИЯ, дополнительно введен узел преобразования цифры, выход знака которого соединен со входом управления видом операции десятичного сумматора и со входом знака блока управления, разряды информационного входа которого с весами 4, 2 и 1 подключены к разрядам информационного выхода узла преобразования цифры с весами 4, 2 и 1, разряды информацион ного входа с весами 8, 4, 2 к которого подсоединены к разрядам выхода младшего десятичного разряда регистра множителя, к младшему разряду регистра множителя подключен выход прибавления единицы блока управления . 2. Устройство по п. 1, отличающееся тем, что узел преобразования цифры содержит элемент НЕ, элемент И и элемент ИЛИ, первый вход которого подключен к выходу элемента И, первый вход которого подсоединен к выходу знака и.к разряду веса 8 информационного входа узла преобразования цифры, второй вход

элемента И через элемент НЕ соединен с разрядом веса 1 информационного входа узла преобразования цифры, разряд веса 2 которого подключен ко второму входу элемента ИЛИ, вход элемента НЕ, выход элемента ИЛИ и разряд веса 4 информационного входа узла преобразования цифры соединены соответственно с разрядами весов .

1И I

И 4 информационного выхоА I

да узла преобразования цифры.

3. Устройство по п. 1,отличающееся тем, что блок управления содержит генератор тактов, счетчик, семь элементов И, элемент НЕ и элемент ИЛИ, причем выход генератора соединен со счетным входом счетчика и с первыми входами элементов И, вторые входы первого, второго и третьего элементов И подключены соответственно к трем разрядам с весами 1, 2 и 4, информационного входа блока управления, выходы четвертого, пятого, шестого и седьмого элементов И являются соответственно выходами управления преобразованием, сдвигом, приеме, прибавлёнйем единицы блока управления, третьи входы пергэго, второго и третьего элементов И соединены соответственно с первым, вторьм и третьим выходами счетчика/ второй вход пятого элемента И соединен с третьим выходом и с установочным входом счетчика, вторые входы шестого и седьмого элементов И Подключены к первому выходу счетчика, третий вход седьмого элемента И подключен к входу знака

0 блока управления, вЁгход пятого элемента И соединен со элемента НЕ, выход которого ло|дключен ко второму входу четвертого элемента И,выходы первого второгр и третьего эле5ментов И соединены со входами элемента ИЛИ, выход которого является выходом сложения блока управления. .

Источники инф фма1ши

0 принятые S& внимание при экспертизе

1.Авторское свидетельство СССР 510714, кл. q 06 F 7/52, i976v

2.йаторское свидетельство СССР йо заявке 2344731/18-24, 62.04.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1979 |

|

SU832554A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1182514A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1989 |

|

SU1668979A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

III I

XI

У1

фи.2

Авторы

Даты

1981-03-30—Публикация

1979-05-11—Подача