Устройство относится к импульсной технике .и может быть использовано в цифровой вычислительной технике.

Цель изобретения -.расширение функциональных возможностей путем- 5 формирования импульсного сигнала при произвольной смене входной ин- ормации, уменьшение потребляемой ощности, уменьшение массогабарит- ных показателей за счет введения 0 овторителей прямого и инверсного входных .сигналов и двух транзисторов с соответствующими связями меж- у ними.

15

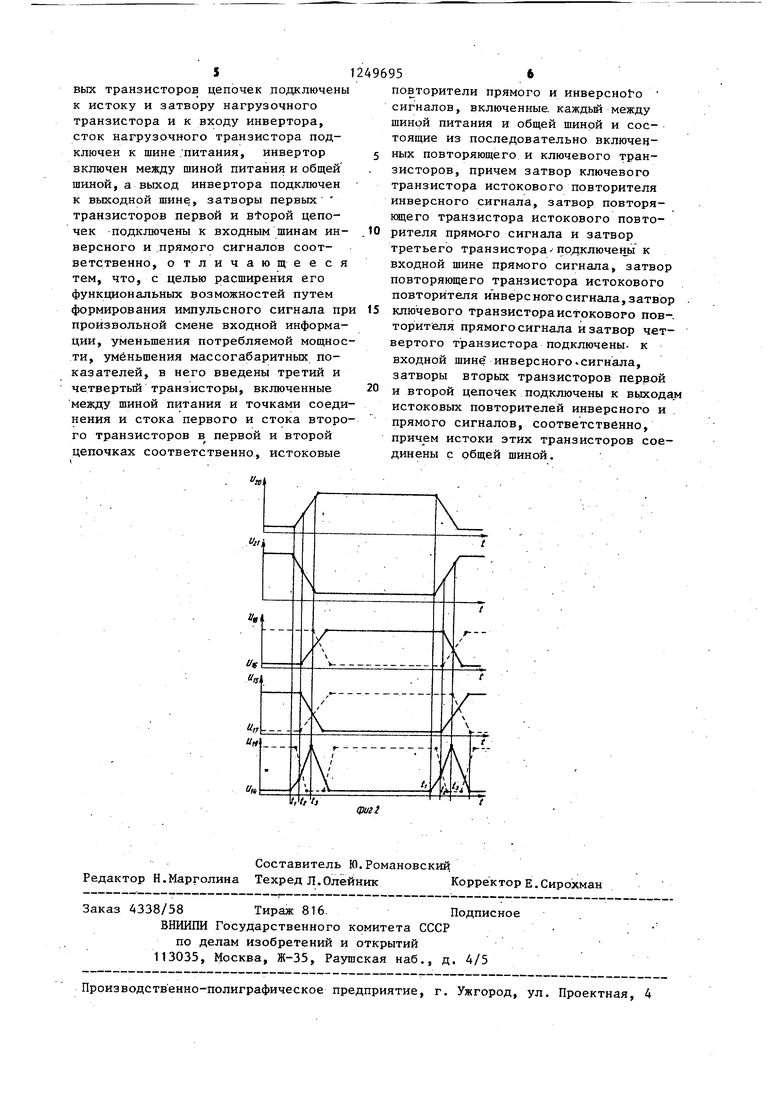

На фиг. 1 изображено устройство бнаружения смены адресного сигнала в интегральном.исполнении на МОП- . транзисторах; на фиг. 2 - временные диаграммы работы устройства. 20

- Устройство содержит истоковый повторитель прямого сигнала на повторяющем .и ключевом транзисторах 1 и 2, истоковый повторитель инверсного 25 сигнала на повторяющем и ключевом, транзисторах 3 и 4 , первую цепочку последовательно.соединенных первого

и второго транзисторов 5 и 6, вторую цепочку последовательно соединенных JQ первого и второго транзисторов 7 и 8, нагрузочного транзистора 9, третьего и .четвертого транзисторов 10 и 11, инвертора ца транзисторах 12,.и 13, Стоки транзисторов 5 и 7 соединены с истоком нагрузочного транзистора 9 в точке 14, в эту же точку подключен вход инвертора - затвор транзистора 13. Истоки транзисторов 6 и 8 соединены с общей шиной, а их затворы подключены к выходам истоко- вых повторителей инверсного и прямого сигналов соответственно в .точках 15 и 1&. Истоки дополнительных транзисторов 10 и 11 подключены к общим точкам 17 и 18 последовательно соединенных транзисторов 5 и 6, 7 и 8

соответственно. .Стоки транзисторов 10 и 11 подключены к шине питания, истоковые повторители прямого (транзисторы 1 и 2) и .инверсного сигналов (транзисторы 3 и 4), инвертор (транзисторы 12 и. 13) включены между шиной питания и общей шиной, выход инвертора подключен к выходной шине в точ- . ке 19.. 55

Затворы транзисторов 5 и 7 под-.

ключены соответственно к входным ши- №ам инверсного и прямого сигналов в

35

40

45

0

5

Q

5

5

0

5

точках 21 и 20. К шине 20 подключены затвор повторяющего транзистора 1 - истоковогр повторителя прямого сигнала, затвор ключевого транзиетора 4 - истокового повторителя инверсного сигнала,и затвор третьего транзистора 10. К шине 21 инверсного сигнала подключены затвор ключевого транзис-. тора 2 - истокового повторителя прямого сигналаг, затвор повторяющего транзистора 3 - истокового повторителя инверсного сигнала и затвор четвертого транзистора 11. .

На временных диаграммах работы устройства (фиг. 2), обозначены потенциалы в точках 14-21 соответственно .

Устройство работает следующим образом. - .

Пусть в исходном состоянии прямой сигнал имеет уровень логического О, а инверсный сигнал - уровень - Логической 1, тогда в точке 1.7 .установится низкий уровень напряжения, а в точке 18 - высокий уровень напряжения. При смене адресного сигнала прямой сигнал перезСо- дит в состояние логической 1, а инверсный сигнал - в состояние логического О. При этом истоковый повторитель прямого, сигнала переходит в состояние логической 1. Уровень напряжения в точке 16 ниже уровня напряжения прямого сигнала на величину порогового напряжения транзистора 1. Таким образом, на- дряжение в точке 18 уменьшается после того, как уровень прямого входного сигнала превьш1ает уровень двух пороговых напряжений МОП-транзис- . торов (момент tg

. В исходном состоянии ток нагрузочного транзистора 9 протекает че-г рез первую цепочку последовательно соединенных транзисторов 3 и 6.Размеры транзисторов 9, 5 и 6 выбирают так, что в исходном состоянии напряжение в точке 14 ниже порогового напряжения транзистора 13.

При переходном процессе напряжение в точке 17 начинает повышаться при превышении уровня прямого входного сигнала уровня порогового на-. пряжения первого транзистора 10 (момент tJ ), что приводит к уменьшению , проводимости транзистора 5. Кроме того, с самого начала переходного процесса (момент t, ) транзистор 5

I

нач инает закрываться по затвору. Таким образом, от момента времени t до, напряжение в точке А начинает возрастать за счет зарядного тока нагрузочного транзистора 9 и уменьшения напряжения на затворе транзистора 5. С момента времени i до момента t скорость возрастания напряжения в точке 14 увеличивается за счет двух дополнительных про- цессов, - дополнительного запирания транзистора 5 по его истоку (точка 17)i разряда точки 18 на точку 14 за счет открытия транзистора 7 прямым входным сигналом.

С момента времени t (уровень двух пороговых напряжений входного прямого сигнала) начинается понижение напряжения в точке 18 через транзистор 8. Когда напряжение в точке 18 понизится так, что разность напряжений между точками 20 и 18 превысит пороговое напряжение транзистора 7, последний откроется и на- пряжение в точке 14 начнет понижаться через, открытые транзисторы 7 и 8-, Размеры транзисторов 7 - 9 выбирают так, .что в установившемся состоянии в точке 14 уровень напряжения не превышает уровень порогового напряжения транзистора 13. Напряжение на выходной шине 19 в целом является инверсным напряжению в точке 14; Инвертор на транзисторах 12 и 13 позволяет подключить к выходной шине большую емкостную и токрвую нагрузки выбор соотношения размеров транзисторов инвертора позволяет устанавливать минимальную длительность импульсного сигнала на выходной клемме. При переключении инверсного входного сигнала в состояние логической 1, а прямого входного сигнала - в состояние логического О процессы, происходящие в точках 16, 15, 17, 18, аналогичны описанным процессам в точках 15, 16, 18, 17 соответственно, работа истоковых повторителей прямого, инверсного сигналов, первой и второй цепочек, третьего и четвертог транзисторов аналогичны описанной работе -иссоковых повторителей инверсного, прямого сигналов, второй и первой цепочек транзисторов,, третьего и. четвертого транзисторов соответст- венно.

Таким образом , при любом изменении адресных сигналов происходит вы

0

5 О 5

,

0

работка импульсного /сигнала и его формирование не ев язано с наличием других сигналов.

Работа предлагаемого устройства не связана с процессами заряда и разряда и возникновением задержек в.. этих процессах. Еди нственным условием работы устройства является то, что уровни логического О входных сигналов меньше порогового напряжения транзисторов, а уровни логической 1 превышаю т уровень двух пороговых напряжений. Последнее выполняется в ИС, реализованных на МОП-транзисторах «.совместимых с ТТЛ Йс1..

Таким образом, предлагаемое Устройство является пороговым формирователем импульсного сигнала и импульсный сигнал формируется при любых длительностях фронтов входных сигналов.

Все вновь вводимые элементы не приводят к изменению тока потребления элементов, входящих в общую часть известного и предлагаемого устройств, количество вводимых элементов меньше, чем количество элементов в известном устройстве. При этом для работы предлагаемого устройства не требуется наличие других устройств (в известном - регистр 40).

Таким образом, в предлагаемом устройстве расширяются функциональные ,возможности за счет формирования импульсного сигнала при асинхронной . (не связанной с тактирующими сигналами) смене информации.

Преимущества предлагаемого устройства по сравнению с известным заключаются в формировании импульсного сигнала при произвольной смене входных адресных сигналов, уменьшенном потреблении тока, кроме того для работы устройства не требуется наличие других дополнительных и синхронизирующих устройств.

Формула изобретения

Устройство обнаружения смены адресного сигнала в интегральном исполнении на МОП-транзисторах, содержащее инвертор, нагрузочный транзистор, первую и вторую цепочки, причем каждая цепочка состоит из последовательно соединенных первого и второго транзисторов, стоки первых транзисторов цепочек подключены к истоку и затвору нагрузочного транзистора и к входу инвертора, сток нагрузочного транзистора подключен к шине /питания, инвертор включен между шиной питания и общей шиной, а выход инвертора подключен к выходной шине, затворы первых транзисторов первой и вфорой цепочек подключены к входным шинам инверсного и .прямого сигналов соответственно, отличающееся тем, что, с целью расщирения его функциональных возможностей путем формирования импульсного сигнала при произвольной смене входной информации, уменьшения потребляемой мощности, уменьшения массогабаритных показателей, в него введены третий и четвертый транзисторы, включенные между шиной питания и точками соединения и стока первого и стока второго транзисторов в первой и второй цепочках соответственно, истоковые

Ut

tftf м

Составитель Ю.Романовский Редактор Н.Марголина Техред Л.Олёйник Корректор Е.Сирохман

Заказ 4338/58 Тираж 816.Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

повторители прямого и инверсного сигналов, включенные, каждый между шиной питания и общей шиной и состоящие из последовательно включенных повторяющего и ключевого транзисторов, причем затвор ключевого транзистора истокового повторителя инверсного сигнала, затвор повторя- кяцего транзистора истокового повторителя прямо-го сигнала и затвор третьего транзистора-пр.дключень1 к входной шине прямого сигнала, затвор повторяющего транзистора истокового повторителя и нверсного сигнала, затвор ключевого транзистораHctoKOBOFo пов-. торит еля прямого сигнала и затвор четвертого транзистора подключены- к входной шине инверсного.сигнала, затворы вторьк транзисторов первой и второй цепочек подключены к вьжодам истоковых повторителей инверсного и прямого сигналов, соответственно, причем истоки этих транзисторов соединены с общей шиной.

-г

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Импульсный генератор (его варианты) | 1980 |

|

SU911693A1 |

| Устройство формирования импульсов на МДП-транзисторах | 1986 |

|

SU1345339A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Двухтактный усилитель импульсного сигнала | 1981 |

|

SU1108611A1 |

| Устройство для последовательного включения источников питания в МДП интегральных схемах | 1986 |

|

SU1406771A1 |

| Стабилизатор постоянного напряжения | 1975 |

|

SU547747A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Сумматор | 1983 |

|

SU1101863A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

Устройство может быть использовано в импульсной и в цифровой вычислительной технике. Цель изобретения - расширение функционадьных возможностей путем формирования импульсного сигнала при произвольной смене входной информации, уменьшение пот.ребляемой мощности, уменьшение массо-габаритных показателей путем введения повторителей прямого и инверсного входных сигналов и .. . двух транзисторов с соответствующими, связями между ними. Устройство содержит истрковые повторители прямого и инверсного си-гналов на повто - ряющем и ключевом транзисторах 1 и 2, 3 и 4 соответственно, первую и вторую цепочки из последовательно соединенных транзисторов (ТР) 5 и 6, 7 и 8 соответственно, дополнительные ТР 10 и 11, инв.ертор на ТР 12 и 13. Стоки ТР 5 и 7 соединены с истоком нагрузочного ТР 9 в точке 14. Устройство является пороговым формирователем импульсного сигнала, который формируется при любых длительностях фронтов входных сигналов. Работа устройства йоясняется временными диаграммами, приведенными в описании изобретения. 2 ил. Q (Л 4 ;о а QD ел фиг.1

Авторы

Даты

1986-08-07—Публикация

1984-05-11—Подача