00

ГЧ)

dte.

Изобретение относится к радиотехнике, используется в асинхронных адресных системах связи и является усовершенствованием изобретения по авт.св. № 1319305.

Цель изобретения - повышение помехоустойчивости.

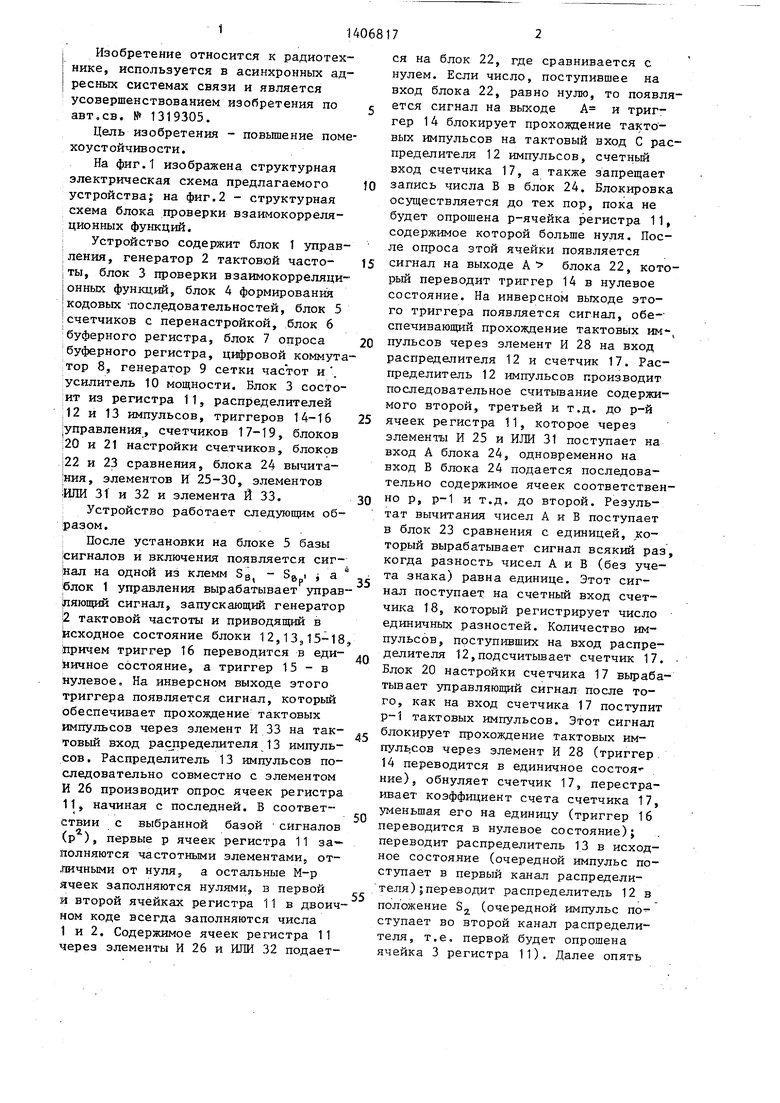

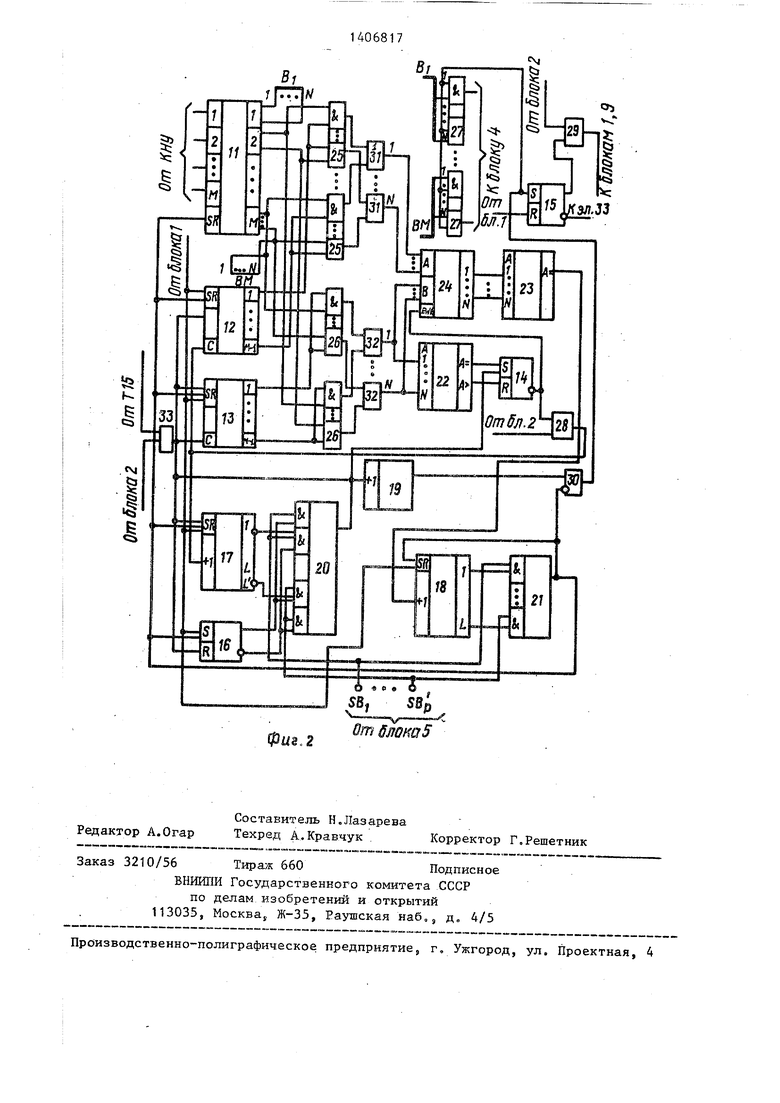

На фиг.1 изображена структурная электрическая схема предлагаемого устройстваJ на фиг.2 - структурная схема блока проверки взаимокорреляционных функций.

I Устройство содержит блок 1 управ- :ления, генератор 2 тактовхэй часто- I ты, блок 3 проверки взаимокорреляци- {онных функи,ий, блок 4 формирования кодовых -последовательностей, блок 5 счетчиков с перенастройкой, блок 6 буферного регистра, блок 7 опроса буферного регистра, цифровой коммутатор 8, генератор 9 сетки частот и . усилитель 10 мощности. Блок 3 состоит из регистра 11, распределителей |12 и 13 импульсов, триггеров 14-16 |управления, счетчиков 17-19, блоков ;20 и 21 настройки счетчиков, блоков 122 и 23 сравнения, блока 24 вычита- ния, элементов И 25-30, элементов 1Ш1И 31 и 32 и элемента И 33. : Устройство работает следующим образом.

После установки на блоке 5 базы :игналов и включения появляется сиг- ал на одной из клемм Sg - Sg i а блок 1 управления вырабатывает управ |ляющий СИГШ1Л, запускающий генератор тактовой частоты и приводящий в исходное состояние блоки 12,13,15-18 причем триггер 16 переводится в еди- Иичное состояние, а триггер 15 - в нулевое. На инверсном выходе этого триггера появляется сигнал, который обеспечивает прохолвдение тактовых Импульсов через элемент И 33 на так- товый вход распределителя 13 импульсов. Распределитель 13 импульсов последовательно совместно с элементом И 26 производит опрос ячеек регистра 11, начиная с последней. В соответствии с выбранной базой сигналов (р), первые р ячеек регистра 11 заполняются частотными элементами, от- .Мичными от нуля 5 а остальные М-р ячеек заполняются нулями, в первой и второй ячейках регистра 11 в двоичном коде всегда заполняются числа 1 и 2. Содержимое ячеек регистра 11 через элементы И 26 и ИЛИ 32 подается на блок 22, где сравнивается с нулем. Если число, поступившее на вход блока 22, равно нулю, то появляется сигнал на выходе А и триггер 14 блокирует прохождение тактовых импульсов на тактовый вход С распределителя 12 импульсов, счетньш вход счетчика 17, а также запрещает запись числа В в блок 24. Блокировка осз/ществляется до тех пор, пока не будет опрошена р-ячейка регистра 11, содержимое которой больше нуля. После опроса этой ячейки появляется сигнал на выходе А блока 22, который переводит триггер 14 в нулевое состояние. На инверсном выходе этого триггера появляется сигнал, обе- спечивающий прохождение тактовых импульсов через элемент И 28 на вход распределителя 12 и счетчик 17. Распределитель 12 импульсов производит последовательное считывание содержимого второй, третьей и т.д. до р-й ячеек регистра 11, которое через элементы И 25 и ИЛИ 31 поступает на вход А блока 24, одновременно на вход В блока 24 подается последовательно содержимое ячеек соответственно р, р-1 и т.д. до второй. Результат вычитания чисел А и В поступает в блок 23 сравнения с единицей, который вырабатывает сигнал всякий раз когда разность чисел А и В (без учета знака) равна единице. Этот сигнал поступает на счетный вход счетчика 18, который регистрирует число единичных разностей. Количество импульсов, поступивших на вход распределителя 12,подсчитывает счетчик 17. Блок 20 настройки счетчика 17 вырабатывает управляющий сигнал после того, как на вход счетчика 17 поступит р-1 тактовых импульсов. Этот сигнал блокирует прохождение тактовых им- пул15сов через элемент И 28 (триггер 14 переводится в единичное состоя - ние), обнуляет счетчик 17, перестраивает коэффициент счета счетчика 17, уменьшая его на единицу (триггер 16 переводится в нулевое состояние); переводит распределитель 13 в исходное состояние (очередной импульс поступает в первый канал распредели- теля);первводит распределитель 12 в положение S (очередной импульс по ступает во второй канал распределителя, т.е. первой будет опрошена ячейка 3 регистра 11). Далее опять

распределитель 13 совместно с элемен тами 26, 32 и 22 осуществляет поиск ячейки регистра 11, содержимое которой отлично от нуля, после чего производятся разблокировка.элемента И 28 и включение в работу распределителя 12, блоков 24 и 23, но в этом случае последними будут опрошены ячейки 3 и р-1 (соответственно распределителями 13 и 12). После опроса этих ячеек счетчик 17 совместно с блок ом 20 вырабатывает управляющий сигнал, по которому срабатьюает счетчик 19. Сигнал с выхода этого счетчика в случае отсутствия сигнала на выходе блока 21 производит перепись частотной кодовой последовательности основного представителя из регистра 11 блока 3 в регистр для хранения кодовой последовательности блока 4, а также переводит триггер 15 в единичное состояние, что отключает блок 3 (тактовые импульсы не проходят через элемент И 33) и разрешает прохождение тактовых импульсов к блокам 1 и 9 через элемент И 29.

При приходе первых четырех импульсов (от блока 2) распределитель 13 опрашивает ячейки регистра 11 с Г1-Й по 8-ю и поскольку их содержимое равно нулю, элемент И 28 не пропускает тактовые импульсы на вход С распределителя 12. После прихода пятого импульса опрашивается 7-я ячейка, где записано число 3, поэтому включаются в работу распределитель 12 и блок 24, вычисляющий с этого момента шесть разностей между числами 2иЗ; 6и4;5и7; 7и5; 4 и 6; 3 и 2. Такие разности имеют место только при нулевом сдвиге, последовательности {-3 f 1 относитель ° I i J (разность между первой парой чисел не вычисляется, так

как она всегда равна нулю - в

Г(Р-01

1 J первой временной позиции всегда расположено число 1).

После опроса распределителем 13 ячейки (распределителем 12 седьмой ячейки) блок 20 вырабатывает управляющий сигнал, после чего опрашиваются ячейки с 11-и по 8-ю регистра 11. Далее опять включаются в работу распределитель 12 и блок 23, вычисляющий пять разностей между парами

чисел Зи7; 4и6;5и5; 6и4; 7 и 3 (разность между первой и второй парами чисел при единичном сдви (Р-0 ге последовательности ;

от,W

носительно j всегда равна 1, поэтому не вычисляется, а счетчик 18 срабатьшает, когда число единичных разностей равно не р-1, а р-3). После вычисления 5-й разности срабатывают блок 20 и счетчик 19.

В этом случае если во время проверки счетчик 18 зарегистрирует р-3 единиц, срабатывает блок 21, Сигнал этого блока приводит блоки 12,

13, 15 и 16 в исходное состояние,обнуляет счетчики 17 и 18, а также обнуляет ячейки регистра 11, запрещая дальнейшее использование оптимальной системы с данным основным представителем.

ФopJ4yлa изобретения

Устройство для передачи многочастотных сигналов по авт.св. № 1319305,

отличающееся тем, что, с целью повьш ения помехоустойчивости, в него введен блок проверки взаимо- корреляционных.функций, причем выход генератора тактовой частоты соединен

с первыми входами блока управления и генератора сетки частот через блок проверки взаимокорреляционных функций, второй выход которого соединен с шестым входом блока формирования ко-

довых последовательностей, второй и третий входы блока проверки взаимокорреляционных функций соединены со- ответственно с третьим выходом блока счетчиков с перенастраиваемым коэффициентом счета и шестым выходом ка управления.

От блока 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1319305A1 |

| Устройство для передачи многочастотных сигналов | 1983 |

|

SU1107328A1 |

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1354437A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для ввода информации | 1991 |

|

SU1800452A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство для запуска импульсных невзрывных источников сейсмических колебаний | 1987 |

|

SU1453348A1 |

Изобретение относится к радиотехнике, используется в асинхронных адресньос системах связи. Цель изобретения - повышение помехоустойчивости. Устр-во содержит блок 1 управления, г-р 2 тактовой частоты, блок 4 формирования кодовых последовательностей, блок 5 счетчиков с перенастройкой, блок 6 буферного регистра, блок 7 опроса буферного регистра, цифровой коммутатор 8, г-р 9 сетки частот, усилитель 10 мощности. С целью повышения помехоустойчивости введен блок 3 проверки взаимокорреляционных функций, второй выход которого соединен с шестым входом блока 4 формирования кодовых последовательностей, второй и третий входы блока 3 проверки взаимокорреляционных функций соединены соответственно с третьим выходом блока 5 счетчиков с перенастройкой и шестым выходом блока 1 управления. 2 ил. с S

Авторы

Даты

1988-06-30—Публикация

1987-01-04—Подача