Изобретение относится к вычислительной технике и может быть использовано для организации вычислительны систем.

Целью изобретения является повышение производительности модуля за счет установления приоритетной дне- циплины обслуживания.

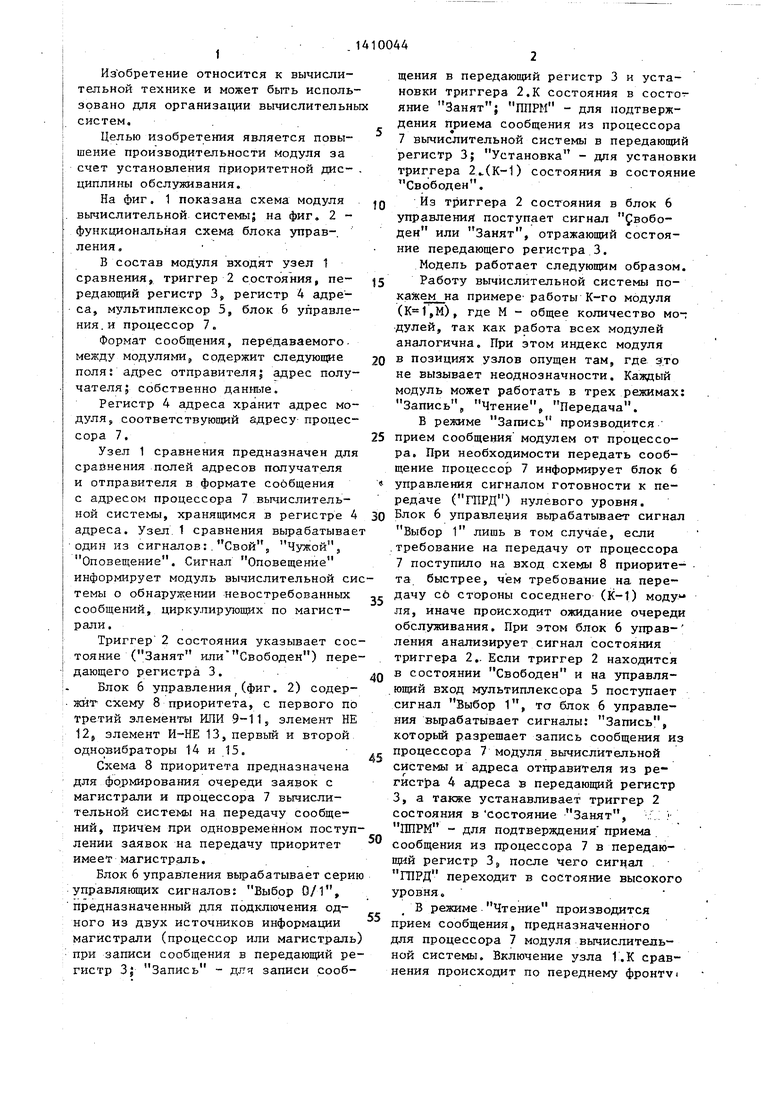

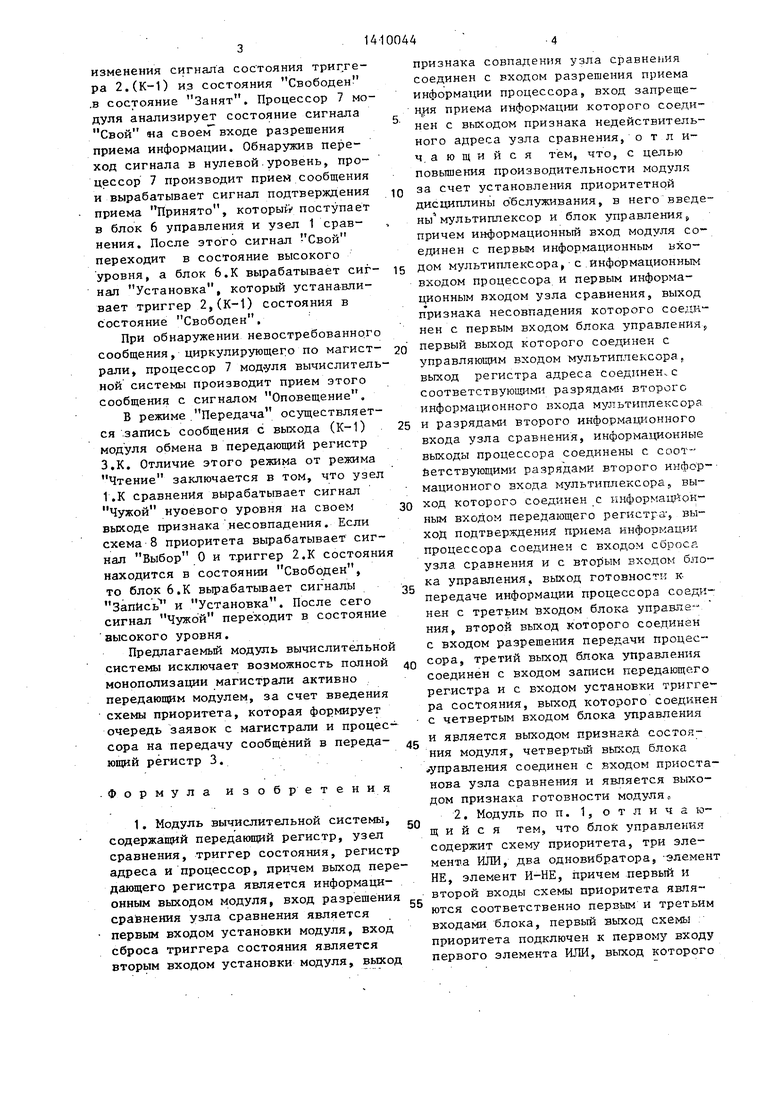

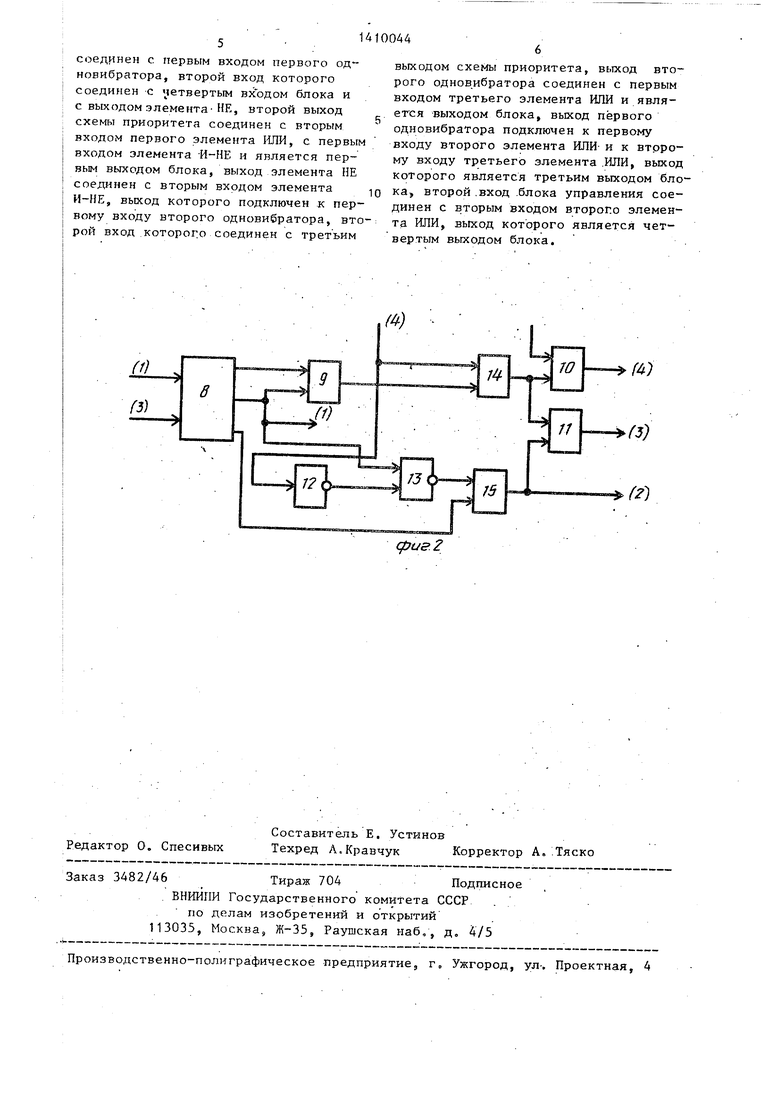

На фиг. 1 показана схема модуля вычислительной системы; на фиг. 2 - функциональная схема блока управ-, ления.

В состав модуля входят узел 1 сравнения, триггер 2 состояния, передающий регистр 3j регистр 4 адреса, мультиплексор 5, блок 6 управления, и процессор 7.

Формат сообщения, передаваемого. между модулямиJ содержит следуюпре поля; адрес отправителя; адрес получателя; собственно данные.

Регистр 4 адреса хранит адрес модуля, соответствующий адресу процессора 7.

Узел 1 сравнения предназначен для срайнения полей адресов получателя и отправителя в формате сообщения с адресом процессора 7 вычислительной системы, хранящимся в регистре 4 адреса. Узел 1 сравнения вырабатывае один из сигналов:.Свой, Чужой, Оповещение. Сигнал Оповещение информирует модуль вычислительной си темы о обнаружении невостребованных сообщений, циркулирующих по магистрали.

Триггер 2 состояния указывает состояние (Занят или Свободен) передающего регистра 3. .

Блок 6 управления (фиг. 2) содержит схему 8 приоритета, с первого по третий элементы ИЛИ 9-11, элемент НЕ 12j элемент И-НЕ 13, первый и второй одновибраторы 14 и 15.

Схема 8 приоритета предназначена для формирования очереди заявок с магистрали и процессора 7 вычислительной системы на передачу сообщений, причем при одновременном поступлении заявок на передачу приоритет имеет магистраль.

Блок 6 управления вырабатывает сери управляющих сигналов: Выбор 0/1, предназначенный для подключения одного из двух источников информации магистрали (процессор или магистраль при записи сообщения в передающий регистр 3; Запись - для записи сообO

5

0

щения в передающий регистр 3 и установки триггера 2.К состояния в состояние Занят ; ППРМ - для подтверждения приема сообщения из процессора 7 вычислительной системы в передающий регистр 3; Установка - для установки триггера 2..(К-1) состояния в состояние Свободен.

Из триггера 2 состояния в блок 6 управлений поступает сигнал вобо- ден или Занят, отражающий состояние передающего регистра 3.

Модель работает следующим образом.

Работу вычислительной системы по- на примере работы К-го модуля (,М), где М - общее количество модулей, так как работа всех модулей аналогична. При этом индекс модуля в Позициях узлов опущен там, где это не вызывает неоднозначности. Каждый модуль может работать в трех режимах: Запись, Чтение, Передача.

В режиме Запись производится 5 прием сообщения модулем от процессора. При необходимости передать сообщение процессора 7 информирует блок 6 управления сигналом готовности к передаче (ГПРД) нулевого уровня. 0 Блок 6 управления вырабатывает сигнал Выбор 1 лишь в том случае, если .требование на передачу от процессора 7 поступило на вход схемы 8 приорите- . та быстрее, чем требование на передачу со стороны соседнего (К-1) моду ля, иначе происходит ожидание очереди обслуживания. При этом блок 6 управ- ления анализирует сигнал состояния триггера 2.. Если триггер 2 находится в состоянии Свободен и на управляющий вход мультиплексора 5 поступает сигнал Выбор 1, то блок 6 управления вьфабатывает сигналы; Запись, который разрешает запись сообщения из процессора 7 модуля вычислительной системы и адреса отправителя из регистра 4 адреса в передающий регистр 3, а также устанавливает триггер 2 состояния в состояние Занят, .:.. : ППРМ - для подтверждения приема сообщения из процессора 7 в передающий регистр 3j, после чего сигнал ГПРД переходит в состояние высокого уровня. .

В режиме Чтение производится прием сообщения, предназначенного для процессора 7 модуля вычислительной системы. Включение узла 1.К сравнения происходит по переднему фронтуi

5

0

5

5

изменения сигнала состояния триггера 2.(К-1) из состояния Свободен .в состояние Занят, Процессор 7 модуля анализирует состояние сигнала Свой «а своем входе разрешения приема информации. Обнаружив переход сигнала в нулевой уровень, процессор 7 производит прием сообщения и вырабатывает сигнал подтверждения приема Принято, которые поступает в блок 6 управления и узел 1 сравнения. После этого сигнал Свой переходит в состояние высокого уровня, а блок 6.К вырабатывает сиг- нал Установка, который устанавливает триггер 2,(К-1) состояния в состояние Свободен,

При обнаружении невостребованного сообщения, циркулирующего по магист- рали, процессор 7 модуля вычислительной системы производит прием этого сообщения с сигналом Оповещение,

В режиме.Передача осуществляется .загшсь сообщения с выхода (К-1) модуля обмена в передающий регистр З.К. Отличие этого режима от режима Чтение заключается в том, что узел 1.К сравнения вырабатывает сигнал Чужой нуоевого уровня на своем выходе признака несовпадения. Если схема 8 приоритета вырабатывает сигнал Выбор О и т-риггер 2.К состояни находится в состоянии Свободен, то блок 6,К вырабатывает сигналы Запись и Установка. После сего сигнал Чужой переходит в состояние

высокого уровня.

Предлагаемьм модуль вычислительно системы исключает возможность полной монополизации магистрали активно передающим модулем, за счет введения схемы приоритета, которая формирует очередь заявок с магистрали и процессора на передачу сообщений в переда- ющий регистр 3.

Формула изобретения

1, Модуль вычислительной системы, содержащий передающий регистр, узел сравнения, триггер состояния, регист адреса и процессор, причем выход пердающего регистра является информационным выходом модуля, вход разрешени сравнения узла сравнения является первым входом установки модуля, вход сброса триггера состояния является вторым входом установки модуля, выхо

признака совпадения узла сравнения соединен с входом разрешения приема информации процессора, вход запреще- приема информации которого соединен с выходом признака недействительного адреса узла сравнения, о т л и- ч, а ю щ и и с я т ем, что, с целью повышения производительности модуля за счет установления приоритетной дисциплины Обслуживания, в него введены мультиплексор и блок управленияJ причем информационный вход модуля соединен с первым информационным входом мультиплексора,- с информационньм входом процессора и первым информационным входом узла сравнения, выход признака несовпадения которого соединен с первым входом блока управления первый выход которого соединен с управляющим входом мультиплексора, выход регистра адреса соединение соответствующими разрядами второго информационного входа мультиплексора, и разрядами второго информационного входа узла сравнения, информационные выходы процессора соединены с соот- бетствующими разрядами второго информационного входа мультиплексора, выход которого соединен с янформац-йон- ным входом передающего регистра-, выход подтверждения приема информации процессора соединен с входом сброса узла сравнения и с вторым входом блока управления, выход готовности к- передаче информации процессора соединен с третьим входом блока управле- НИН, второй выход которого соединен с входом разрешения передачи процессора, третий выход блока управления соединен с входом записи передающего регистра и с входом установки триггера состояния, выход которого соединен с четвертым входом блока управления

и является выходом признаки, состояния модуля, четвертый выход блока управления соединен с входом приоста- нова узла сравнения и является выходом признака готовности модуля„

2, Модуль по п. 1, отличающийся тем, что блок управления содержит схему приоритета, три элемента ИЛИ, два одновибратора, -элемент НЕ, элемент И-НЕ, причем первый и второй входы схемь: приоритета являются соответственно первым и третьим входами блока, первый выход схемы приоритета подключен к первому входу первого элемента ИЖ, выход которого

соединен с. первым входом первого од- новибратора, второй вход которого соединен с четвертым вхЪдом блока и с выходом элемента-НЕ, второй выход схемы приоритета соединен с вторым входом первого элемента 1ШИ, с первым входом элемента -И-НЕ и является первым выходом блока, выход элемента НЕ соединен с вторым входом элемента И-НЕ, выход которого подключен к первому входу второго одновибратора, вто рой вход которого соединен с третьим

выходом схемы приоритета, выход второго однов.ибратора соединен с первым входом третьего элемента ИЛИ и является выходом блока, выход первого одновибратора подключен к первому входу второго элемента ИЛИ и к второму входу третьего элемента .ИЛИ, выход которого является третьим выходом блока, второй .вход .блока управления соединен с вторым входом второго элемента ИЛИ, выход которого является четвертым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения абонента с кольцевой локальной сетью | 1988 |

|

SU1658158A1 |

| Канал обмена | 1988 |

|

SU1501074A1 |

| Многоканальное устройство для обмена информацией | 1988 |

|

SU1564637A1 |

| Канал обмена | 1986 |

|

SU1392570A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Канал обмена | 1986 |

|

SU1410045A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU924694A1 |

Изобретение относится к вычислительной технике и может быть использовано для организации вычисли- тельньк систем. Целью изобретения является повышение производительности модуля за счет установления приоритетной дисциплины обслуживания, Поставленная цель достигается тем, что- в устройство, содержащее узел 1 сравнения, триггер 2 состояния, передающий регистр 3, регистр 4 адреса и процессор 7, введены мультиплексор 5 и блок 6 управления. Модуль вычислительной системы выполняет новые функции, которые реализуются с относительно меньшими затратами. Ис- .ключается возможность полной монополизации магистрали активно.передающим модулем, обеспечивается освобождение магистрали от пакетов невостребованных сообщений, предназначенных отключенным либо неисправным модулям. 1 з.п. ф-лы, 2 ил. с 3

д}ие2

| Устройство связи для вычислительной системы | 1977 |

|

SU734654A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU962907A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-15—Публикация

1986-10-04—Подача