Л

65

4

х

tf

фигЛ

25

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является повышение надежности.

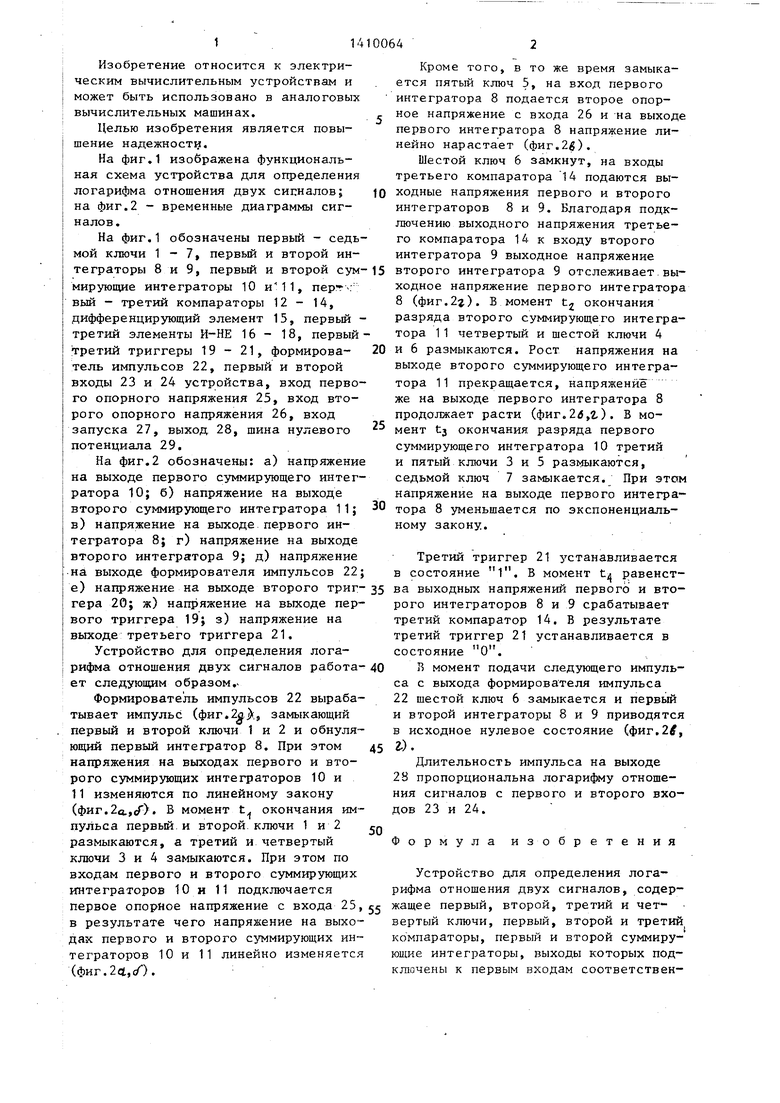

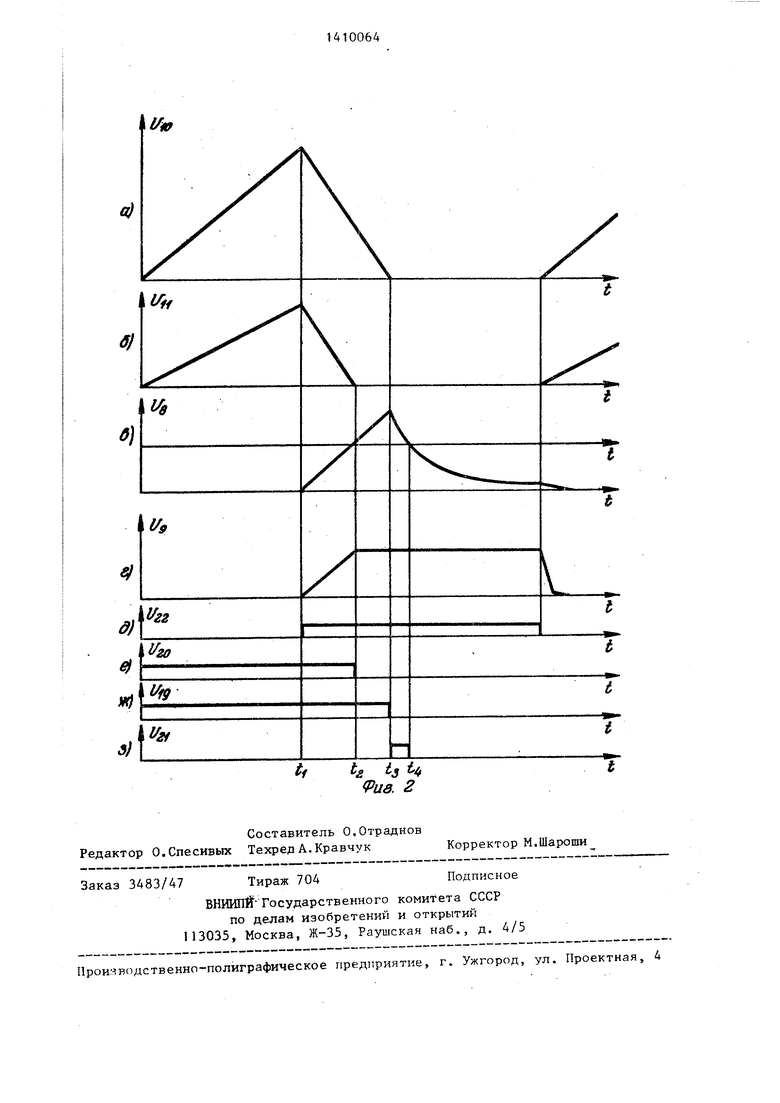

На фиг,1 изображена функциональная схема устройства для определения логарифма отношения двух сигналов; to на фиг.2 - временные диаграммы сигналов .

На фиг.1 обозначены первый - седьмой ключи 1-7, первый и второй интеграторы 8 и 9, первый и второй сум- 15 мирующие интеграторы 10 , перт-г вый - третий компараторы 12 - 14, дифференцирующий элемент 15, первый - третий элементы И-НЕ 16 - 18, первый- третий триггеры 19 - 21, формирова- 20 тель импульсов 22, первый и второй входы 23 и 24 устройства, вход первого опорного напряжения 25, вход второго опорного напряжения 26, вход запуска 27, выход 28, шина нулевого потенциала 29,

На фиг.2 обозначены: а) напряжение на выходе первого суммирующего интегратора 10; б) напряжение на выходе второго суммирующего интегратора 11; 30 в) напряжение на выходе первого интегратора 8; г) напряжение на выходе второго интегратора 9; д) напряжение на. выходе формирователя импульсов 22; е) напряжение на выходе второго триг-35 гера 20; ж) напряжение на выходе первого триггера 19; з) напряжение на выходе третьего триГ гера 21.

Устройство для определения лога- рифма отношения двух сигналов работа- 40 ет следующим образом,Формирователь импульсов 22 вырабатывает импульс (фиг.2л)г,, замыкающий первый и второй ключи 1 и 2 и обнуляющий первый интегратор 8. При этом 45 напряжения на выходах первого и второго суммирующих интеграторов 10 и 11 изменяются по линейному закону (фиг.2а.,еГ). В момент t. окончания импульса первый, и второй, ключи 1 и 2 д размыкаются, а третий и четвертый ключи 3 и 4 замыкаются. При этом по входам первого и второго суммирующих интеграторов 10 и 11 подключается первое опорное напряжение с входа 25,55 в результате чего напряжение на выходах первого и второго суммирующих интеграторов 10 и 11 линейно изменяется (фиг. 2с(.,(/ ).

5

o

0

0

Кроме того, в то же время замыкается пятый ключ 5, на вход первого интегратора 8 подается второе опорное напряжение с входа 26 и на выходе первого интегратора 8 напряжение линейно нарастает (фиг.2).

Шестой ключ 6 замкнут, на входы третьего компаратора 14 подаются выходные напряжения первого и второго интеграторов 8 и 9. Благодаря подключению выходного напряжения третьего компаратора 14 к входу второго интегратора 9 выходное напряжение второго интегратора 9 отслеживает.выходное напряжение первого интегратора 8 (фиг.2г). В момент t окончания разряда второго суммирующего интегратора 11 четвертый и шестой ключи 4 и 6 размыкаются. Рост напряжения на выходе второго суммирующего интегратора 11 прекращается, напряжений же на выходе первого интегратора 8 продолжает расти (фиг. 24,2,). В момент t3 окончания разряда первого суммирующего интегратора 10 третий и пятый ключи 3 и 5 размыкаются, седьмой ключ 7 замыкается. При этом напряжение на выходе первого интегратора 8 уменьшается по экспоненциальному закону.

Третий триггер 21 з станавливается в состояние 1. В момент t/ равенства выходных напряжений первого и второго интеграторов 8 и 9 срабатывает третий компаратор 14. В результате третий триггер 21 устанавливается в состояние О.

R момент подачи следующего импульса с выхода формирователя импульса 22 шестой ключ 6 замыкается и первый и второй интеграторы 8 и 9 приводятся в исходное нулевое состояние (фиг.2#,

г).

Длительность импульса на выходе 28 пропорциональна логарифму отношения сигналов с первого и второго входов 23 и 24.

Формула изобретения

Устройство для определения логарифма отношения двух сигналов, содержащее первый, второй, третий и чет- вертый ключи, первый, второй и третий компараторы, первый и второй суммирующие интеграторы, выходы которых подключены к первым входам соответствен-

314

но первого и в,торого компараторов, формирователь импульсов, информационные входы первого и второго ключей являются соответственно первым и вторым информационными входами устройства, отличающееся тем, что, с целью повышения надежности работы, в него введены пятый, шестой и седьмой ключи, первый и второй интеграторы, дифференцирующий элемент, первый, второй и третий элементы И-НЕ, первый, второй и третий тригге- .ры, причем выход первого ключа соединен с первым информационным входом первого суммирующего интегратора, выход второго ключа соединен с первым .информационным входом второго суммирующего интегратора, информационные входы третьего и четвертого ключей соединены с входом первого опорного напряжения устройства, выходы третьего и четвертого ключей подключены к вторым информационным входам соответственно первого и второго суммирующих интеграторов, вторые входы первого и второго компараторов подключены к шине нулевого потенциала, вьпсрд первого компаратора соединен с третьим информационным входом первого суммирующего интегратора и с входом сброс первого триггера, выход второго компаратора подключен к третьему информационному входу второго суммирующег интегратора и к входу сброса второго триггера, информационный вход пятого ключа является входом второго опорного напряжения устройства, выходы первого и второго интеграторов соединен

соответственно с первым и вторым входами третьего компаратора, выход которого подключен к информационному

входу шестого ключа и к первому входу третьего триггера, к второму входу которого подключен выход дифференцирующего элемента, прямой выход третьего триггера является выходом устройства, выходы пятого и шестого ключей соединены с информационными входами соответственно первого и второго интеграторов, между информационным входом и выходом первого интегратора включен седьмой ключ, прямой выход первого триггера подключен к управляющему входу седьмого ключа, к входу дифференцирующего элемента и к первым входам первого и второго элементов И-НЕ, прямой выход второго триггера соединен с первым входом третьего элемента И-НЕ, выход формирователя импульсов подключен к входам установки первого и второго триггеров, к вторым входам первого, второго и третьего элементов И-НЕ, к управляющим входам первого и второго ключей и к входу обнуления первого интегратора, выход первого элемента И-НЕ соединен с управляющим входом третьего

ключа, выход третьего элемента И-НЕ соединен с управляющим входом четвертого ключа, выход второго элемента И-НЕ подключен к управляющему входу пятого ключа, инверсный выход второго триггера соединен с управляющим входом шестого ключа, вход формирователя импульсов является входом запуска устройства.

а)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения отношения двух напряжений | 1980 |

|

SU1018032A1 |

| Устройство для преобразования физической величины в код | 1987 |

|

SU1481691A1 |

| Устройство для измерения отношения двух напряжений | 1983 |

|

SU1147991A1 |

| Устройство для измерения коэффициента прямоугольности амплитудно-частотной характеристики радиоприемников | 1990 |

|

SU1755383A1 |

| Генератор случайного напряжения | 1984 |

|

SU1241238A1 |

| Способ преобразования кода угла в напряжения,пропорциональные синусу и косинусу угла, и устройство для его осуществления | 1985 |

|

SU1345346A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Цифровой фазометр | 1985 |

|

SU1308935A1 |

| Устройство для измерения отношения двух напряжений | 1981 |

|

SU1026068A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ РАССЕЯНИЯ ЭНЕРГИИ И СОБСТВЕННОЙ ЧАСТОТЫ МЕХАНИЧЕСКОЙ КОЛЕБАТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2025685C1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение надежное-, ти работы. Устройство для определения логарифма отношения двух сигналов содержит первый, второй, третий, четвертый, пятый, шестой и седьмой ключи 1 , 2, 5 4, 5, 6 и 7, первый и второй интеграторы 8 и 9, первый и второй суммирующие интеграторы 10 и 11, первьвй, второй и третий компараторы 12, 13 и 14, дифференцирующий .элемент 15, первУый, второй и третий элементы И-НЕ 16, 17 и 18, первый, второй и третий триггеры 19, 20 и 21, формирователь импудьсов 22, первый и второй входы 23 и 24, вход первого опорного напряжения 25j вход второго опорного напряжения 26, вход запуска 27, выход 28, шину нулевого потенциала 29. Работа устройства основана на сравнении напряжения экспоненциальной формы с выхода первого интегратора 8 с напряжением линейной формы с выхода второго интегратора 9 и формировании результирующего импульса, пропорционального логарифму отношения двух входных сигналов. 2 ил. f. (Л с

61

б

ff)

JW

%

j;

%

i

/

Т

| Патент США № 3664744, кл | |||

| Приспособление для постепенного включения и выключения фрикционных муфт в самодвижущихся экипажах и т.п. | 1919 |

|

SU356A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Устройство для логарифмической обработки двух сигналов | 1983 |

|

SU1103250A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-15—Публикация

1986-12-29—Подача