51 М.

т

4;

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ контроля логических схем | 1987 |

|

SU1562865A1 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| Способ контроля работы насосной станции и устройство для его осуществления | 1982 |

|

SU1089300A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| БЕСПЛАТФОРМЕННАЯ ИНЕРЦИАЛЬНАЯ НАВИГАЦИОННАЯ СИСТЕМА | 2013 |

|

RU2563333C2 |

| Устройство для имитации отказов и сбоев ЭВМ | 1987 |

|

SU1564628A1 |

| Устройство для контроля магистралей ЭВМ | 1980 |

|

SU945868A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| Устройство для контроля магистралей электронных вычислительных машин | 1981 |

|

SU964648A1 |

Изобретение может быть использовано для обнаружения и указания места неисправного элемента в логических схемах из п элементов шинных формирователей. Способ контроля логических схем реализован в устройстве, содержащем элементы 1,1-l.n шинных формирователей (ШФ), образующие общую магистраль 3 электрической связи и имеющие входы 4.1- 4оП, 5о1-5.п и выходы 2.1-2.П, микроамперметр 7. Определяют состояние, возникшее на обшей магистрали 3 электрической связи в результате наличия одного или нескольких неисправных элементов ШФ, подбирают виды входных воздействий, при которых напряжение на общей магистрали 3 соответственно равно и отличается от эталонного, формируют измерительную цепь между общей магистралью и нулевой шиной логической схемы, подают на все элементы логической схемы первое входное воздействие и последовательно подают на каждый из элементов второе входное воздействие, выбирают в качестве выходного информативного параметра изменение тока в измерительной цепи. Способ имеет расширенную область использования. 1 ил. tp (Л

1

О) СО 00

Изобретение относится к контроль- но-измерительнбй технике и может быт использовано для обнаружения и .указания места неисправного элемента в логических схемах из п элементов шинных формирователей (магистральных приемопередатчиков, двунаправленных усилителей-формирователей, магистральных передатчиков, магистральных приемников)) выходы которых соединен в общую магистраль электрической связи в печатном узле.

Цель изобретения - расширение области применения способа за счет поиска неисправного элемента в логических схемах, содержащих выходные щин- ные формирователи, выходы которых соединены в общую магистраль.

В качестве входного тестового воздействия используются сигналы, последовательно изменяюпще состояние выходных элементов шинных формирователей, объединенных в магистраль, и измеряются изменения тока между магистралью и общим проводом устройства, что позволяет обнаруживать неисправный элемент,не нарушая печатного монтажа «

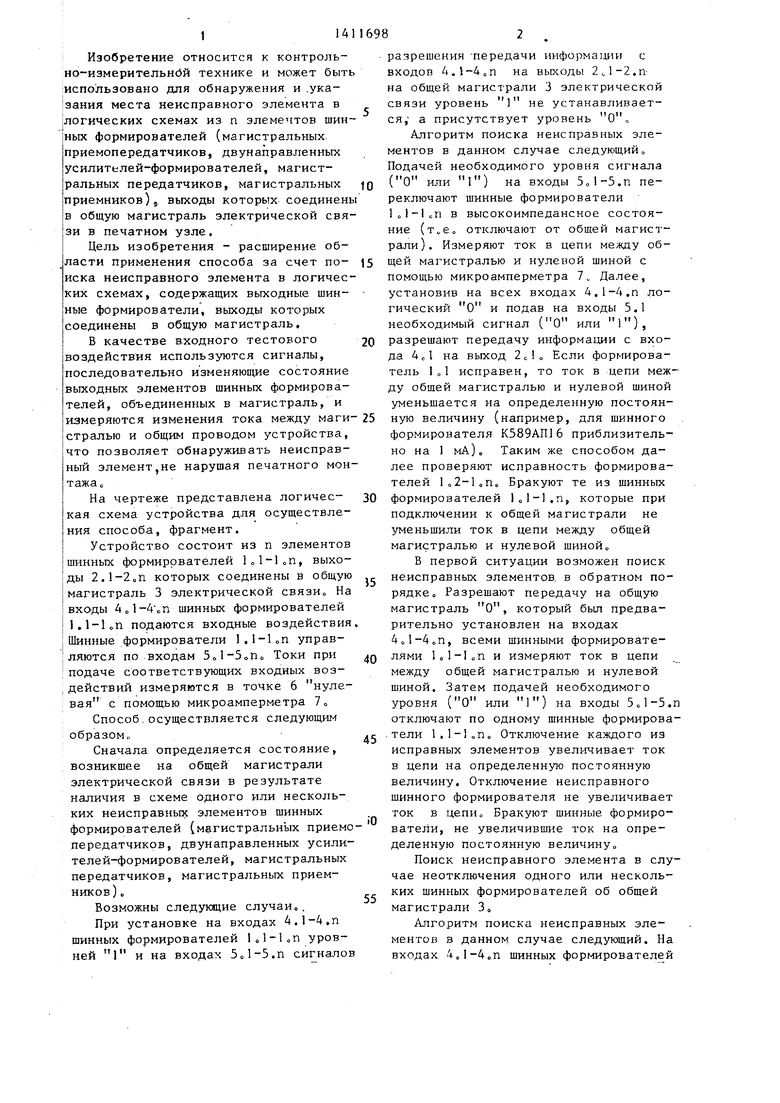

На чертеже представлена логическая схема устройства для осуществления способа, фрагмент.

Устройство состоит из п элементов шинных формирователей 1о1-1оП, выходы 2.-2„п которых соединены в общую магистраль 3 электрической связи На входы А„1-4 сП шинных формирователей 1.1-1оП подаются входные воздействия Шинные формирователи l.l-Kn управляются по входам ,По Токи при подаче соответствующих входных воздействий измеряются в точке 6 нулевая с помощью микроамперметра 7

Способ.осуществляется следующим образом,,

Сначала определяется состояние, возникшее на общей магистрали электрической связи в результате наличия в схеме одного или нескольких неисправных элементов шинных формирователей (магистральных приемо передатчиков, двунаправленных усилителей-формирователей, магистральных передатчиков, магистральных приемников) „

Возможны следующие случаи. При установке на входах 4.1-4.П шинных формирователей 1.1-1оП уровней 1 и на входах 5о1-5.п сигналов

10

15

20

25

30

15

40

45

0

55

разрешения -передачи информаили с входов А,1-4„п на выходы 2J-2.n- на общей магистрали 3 электрической связи уровень 1 не устанавливается; а присутствует уровень

Алгоритм поиска неисправных элементов в данном случае следующий Подачей необходимого уровня сигнала (О или 1) на входы 5„1-5.п переключают шинные формирователи 1о1-1оП в высокоимпедансное состояние (т„ео отключают от общей магистрали). Измеряют ток в цепи между общей магистралью и нулевой шиной с помощью микроамперметра 7 Далее, установив на всех входах 4.1-4.П логический О и подав на входы 5,1 необходимый сигнал (О или 1), разрешают передачу информации с входа 4сI на выход Если формирователь 1о1 исправен, то ток в цепи между общей магистралью и нулевой шиной уменьшается на определенную постоянную величину (например, для шинного формирователя К589АП16 приблизительно на 1 мА)„ Таким же способом далее проверяют исправность формирователей 1„2-1,п. Бракуют те из шинных формирователей 1„1-1,п, которые при подключении к общей магистрали не уменьшили ток в цепи между общей магистралью и нулевой шиной о

В первой ситуации возможен поиск неисправных элементов, в обратном порядке о Разрешают передачу на общую магистраль О, который был предварительно установлен на входах 4о1-4,п, всеми шинными формирователями lol-IoH и измеряют ток в цепи между общей магистралью и нулевой шиной. Затем подачей необходимого уровня (О или 1) на входы 5о1-5.п отключают по одному шинные формирова- .тели 1.1-1„По Отключение каждого из исправных элементов увеличивает ток в цепи на определенную постоянную величину. Отключение неисправного шинного формирователя не увеличивает ток в цепи о Бракуют шинные формирователи, не увеличивш11е ток на определенную постоянную величину

Поиск неисправного элемента в случае неотключения одного или нескольких шинных формирователей об общей магистрали 3,

Алгоритм поиска неисправных элементов в данном случае следующий. На входах 4.1-4с,п шинных формирователей

устанавливают уровень 1 и подачей соответствующих необходимых сигналов (О или 1) на входы 5.1-5.П разрешают передачу информации на выходы 2о1-2,п, На общей магистрали присутствует уровень 1, Измеряют ток в цепи между общей магистралью и нулевой шиной. Далее поочередно по одному, подавая соответствующие сигналы (О или 1) на входг 5о1-5оП, отключают шинные формирователи 1о1- оП от общей магистрали 3„ Отключение исправного шинного формирователя приводит к уменьшению тока Б цепи между общей магистралью и нулевой шиной на определенную величину (например, для К589АП16 приблизительно на 50 мА)„ Неисправный шинный формирователь при его отключении от общей магистрали не изменяет ток в цепи. Бракуют шинный формирователь, не изменивший ток в цепи между общей магистралью и нулевой шиной при отключении его от общей магистрали.

Возможен и другой алгоритм в случае неотключения одного или нескольких шинных формирователей от общей магистрали. На входах 4,1-4оП шинных формирователей 1„1-1.п устанавливают уровень О и подачей соответствующих сигналов (О или 1) на входы 5о1-5„п разрешают передачу информации с входов А,1-4,п на общую магистраль. Контролируют наличие О на общей магистрали Измеряют ток в цепи между общей магистралью и нулевой щиной;, Затем поочередно по одному отключают щинные формирователи 1о1-1оП от общей магистрали. Отключение исправного шинного формирователя увеличивает ток в цепи тока корпус на определенную постоянную величину Неисправный шинный формирователь при отключении от общей магистрали не изменяет ток в цепи между общей магистралью и нулевой щи- ной. Бракуют шинный формирователь, не изменивший ток в цепи.

Поиск неисправного элемента в случае перегрузки общей магистрали отключенными шинными формирователями, т.е. случай, когда отключенный в высркоимпедансное состояние шинный формирователь создает в общей магистрали нагрузку, равную не одному, а нескольким отключенным шинным формирователям.

11698

Для выявления элемента, перегружающего о щую магистраль, устанав.чи- вают на входах 4Л-4,п щинных формирователей 1.1-1,п уровень О и соответствующими необходимыми сигналами (О или 1) разрешают передачу этих сигналов (О) с входов 4„1-4 п на общую магист-раль. Контролируют

JQ наличие О на общей магистрали. Затем поочередно по одному отключают в высокоимпедансное состояние шинные формирователи 1,1-Кп и наблюдают изменение тока в цепи между общей 5 магистралью и нулевой шиной Исправный шинный формирователь при отключении его от общей магистрали увеличивает ток в цепи между общей магистралью и нулевой шиной на определен- JQ ную постоянную величину (например, для К589АП16 приблизительно на I мА), а подсаживающий магистраль шинный формирователь при отключении увеличивает ток в этой цепи на величину 25 меньше определенной постоянной (менее 1 мА для К589АП1б)„ Бракуют шинный формирователь, не увеличивший при отключении ток в цепи между общей магистралью и нулевой щиной на 30 определенную постоянную величину.

Формула изобретения

Способ контроля логических схем, заключающийся в том, что на контролируемую логическую схему подают напря- , жение питания, прикладывают к ческим входам испытательное воздействие, регистрируют изменение выходного информативного параметра каждо4Q го из элементов контролируемой логической схемы, сравнивают его с эталонным и по результатам сравиения судят об исправности элементов логических cxebd, отличающийся

д5 тем, что, с целью расширения области применения способа за счет поиска неисправного элемента в логических схемах, содержащих выходные шинные формирователи, выходы которых соеди35

нены в общую магистраль, синхронно переводят все элементы логической схемы, соединенные выходом с общей магистралью, в каждое из возможных выходных логических состояний и, измеряя напряжение на общей магистрали, определяют характер неисправности, подбирают виды первого и второго входных воздействий, при которых нап- ряжение на общей магистрали соответ 14116986

ственно равно и отличается от эталон-но подают на каждый н: э мчи и гги:,(.-1 еного, формируют измерительную цепьдиненных выходами с обшей MarvicTмежду общей магистралью и нулевойралью, второе входное воздействие,

шиной логической схемы, подают на выбирают в качестве выходно о инфорвсе элементы логической схемы первоемативного параметра У1зменение тока

входное воздействие и последователь-в измерительной цепи.

| Способ контроля ТТЛ интегральных схем | 1982 |

|

SU1056088A1 |

Авторы

Даты

1988-07-23—Публикация

1986-12-18—Подача