Изобретение относится к вычислительной технике и может быть использовано при построении параллельных микропроцессорных систем повышенной надежности, в час- тносги для цифровой обработки радиолокационной информации (ЦОРЛИ).

Цель изобретения - повышение надежности системы за счет сокращения длительности существования скрытых отказов в условиях малой длительности перерыва в работе и низкой достоверности встроенного контроля.

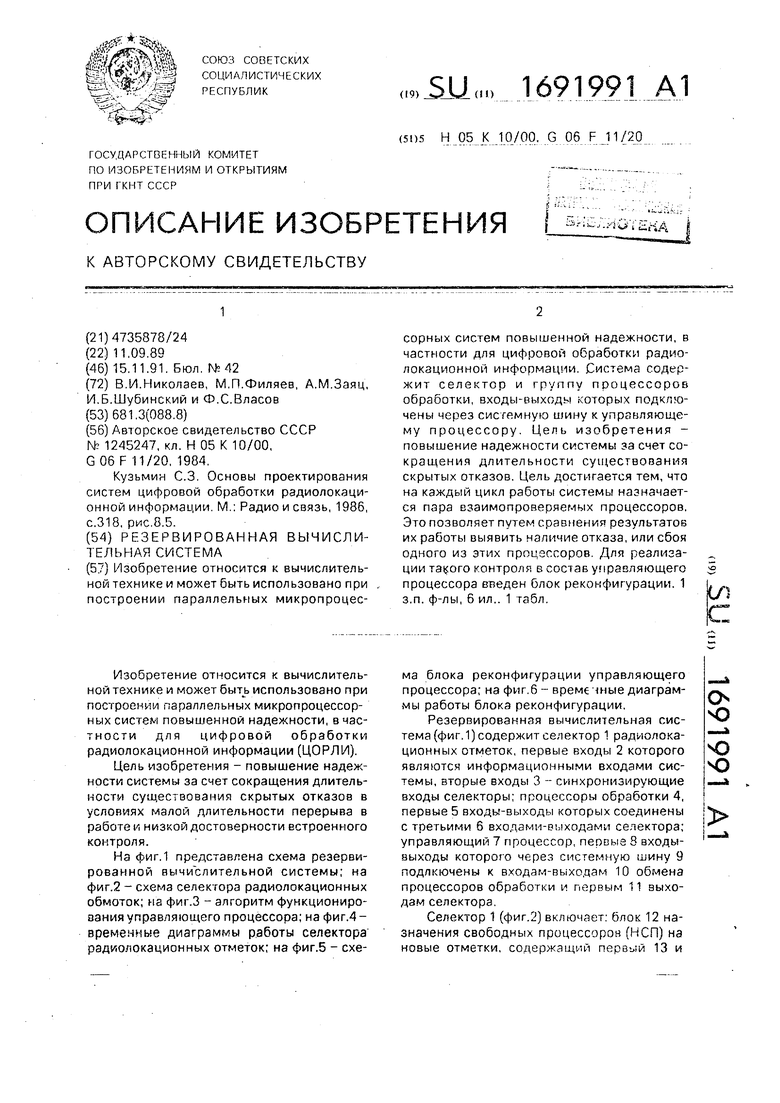

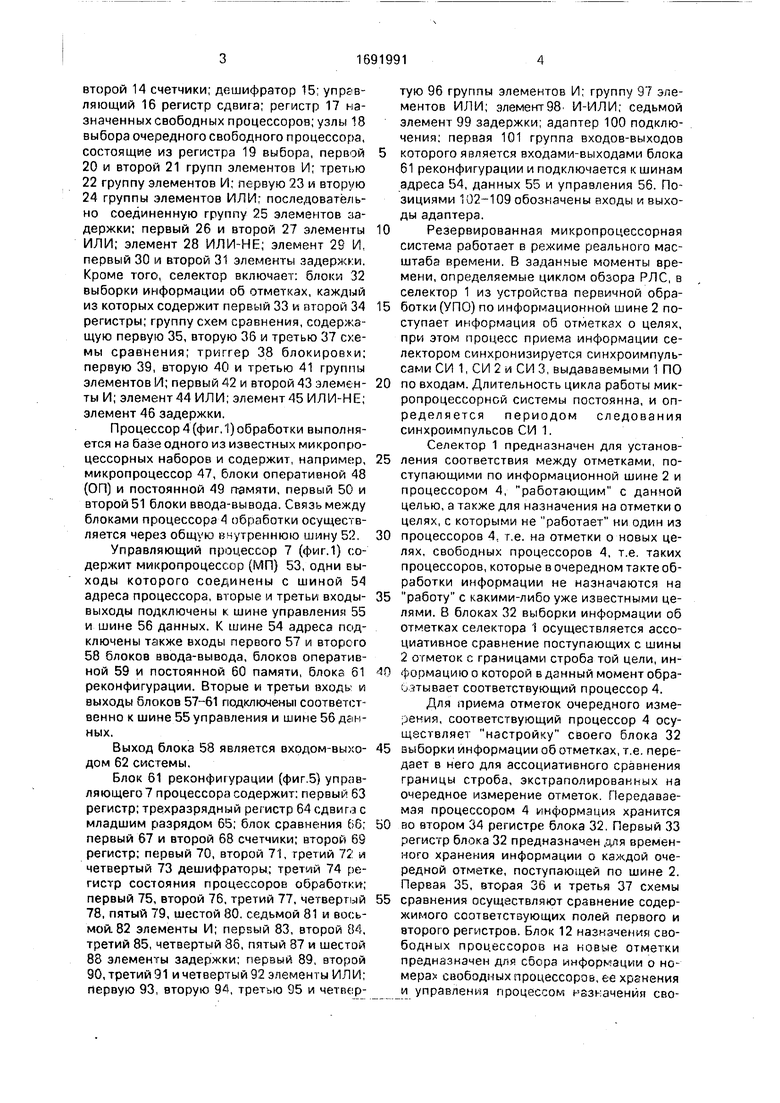

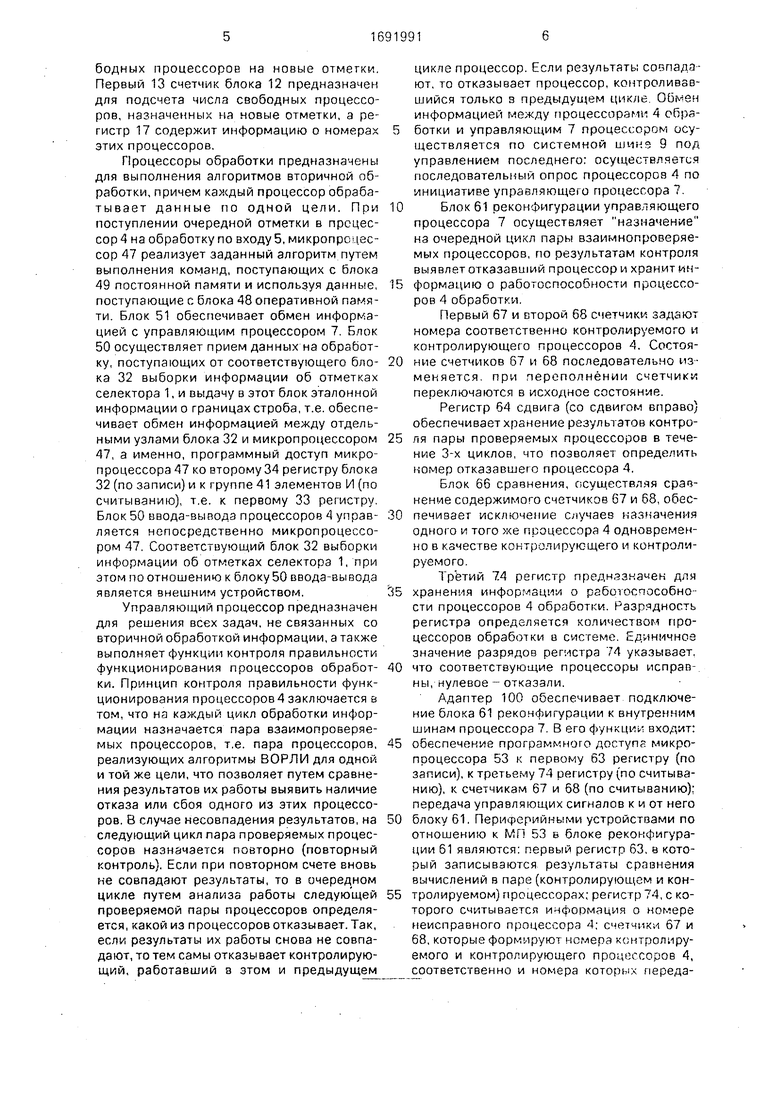

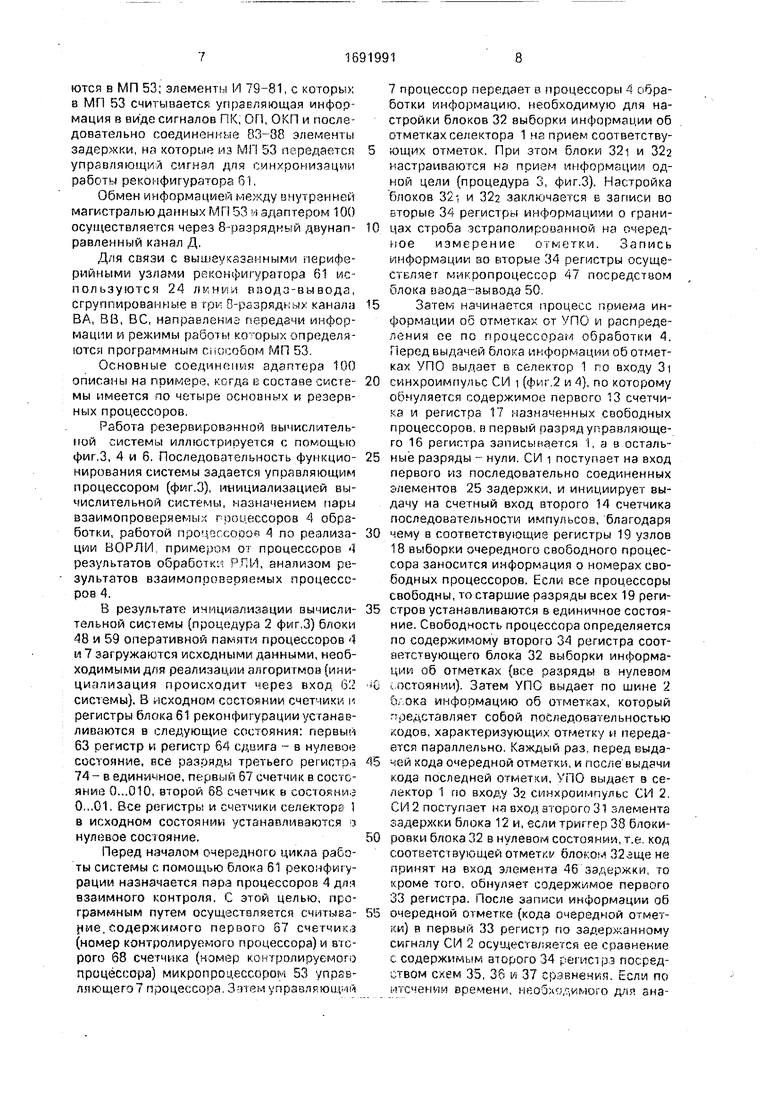

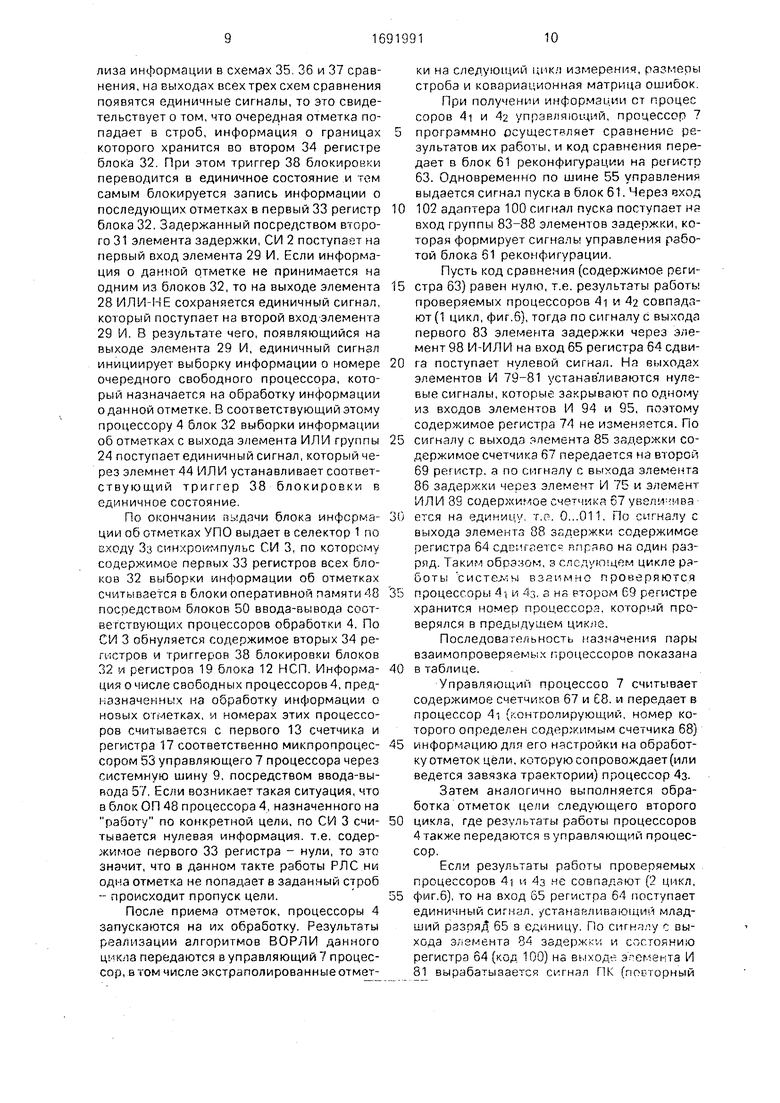

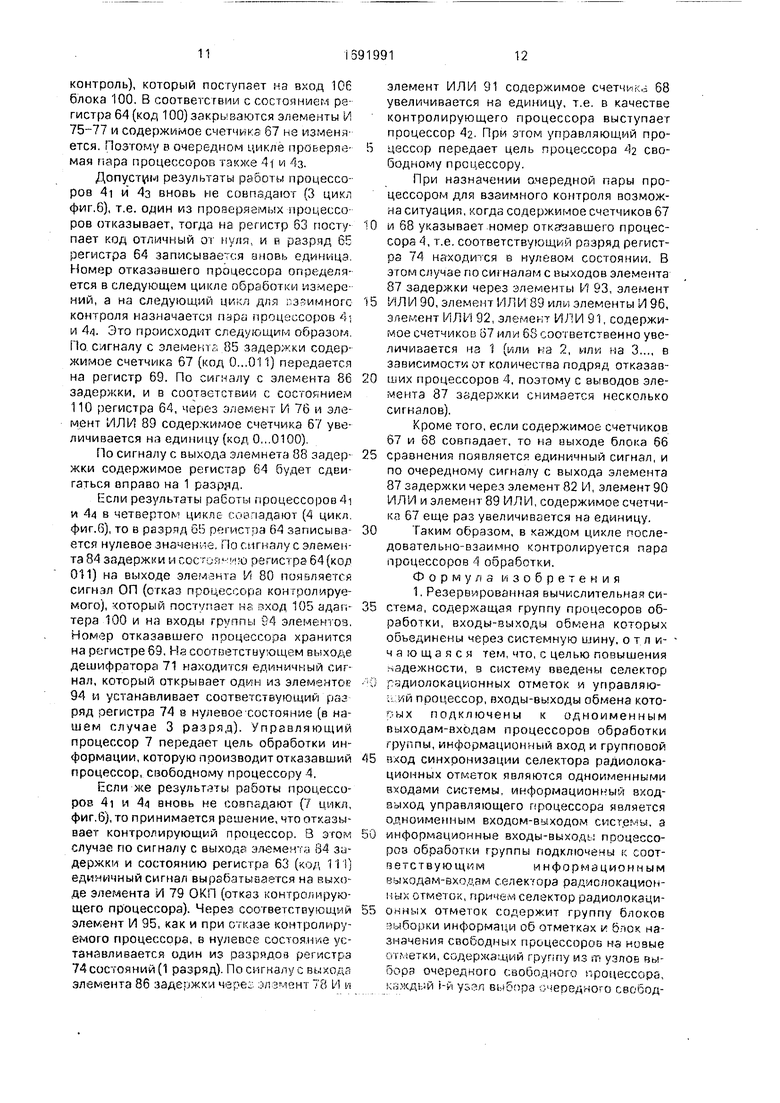

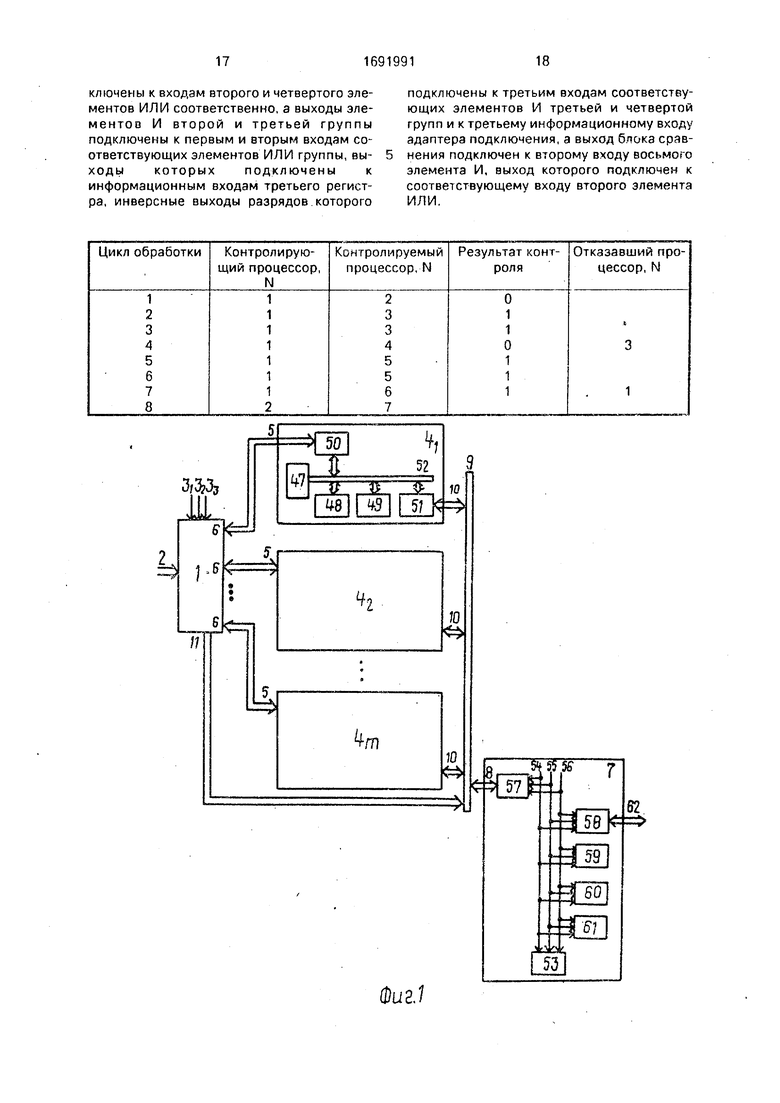

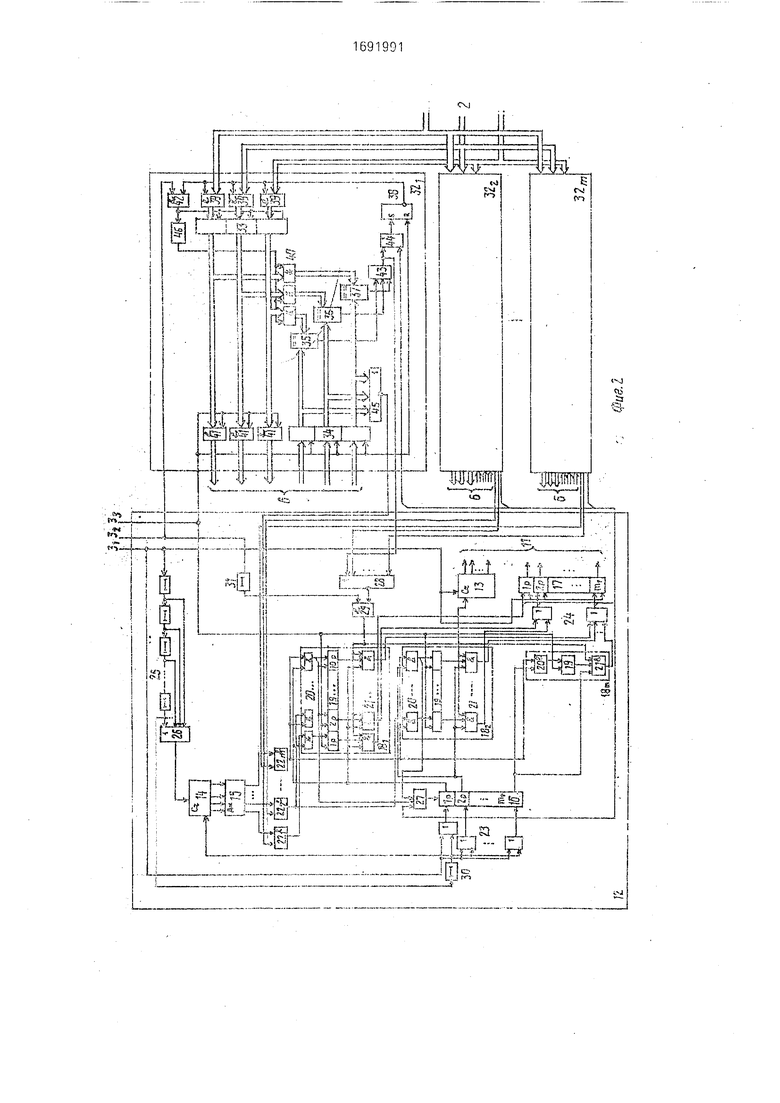

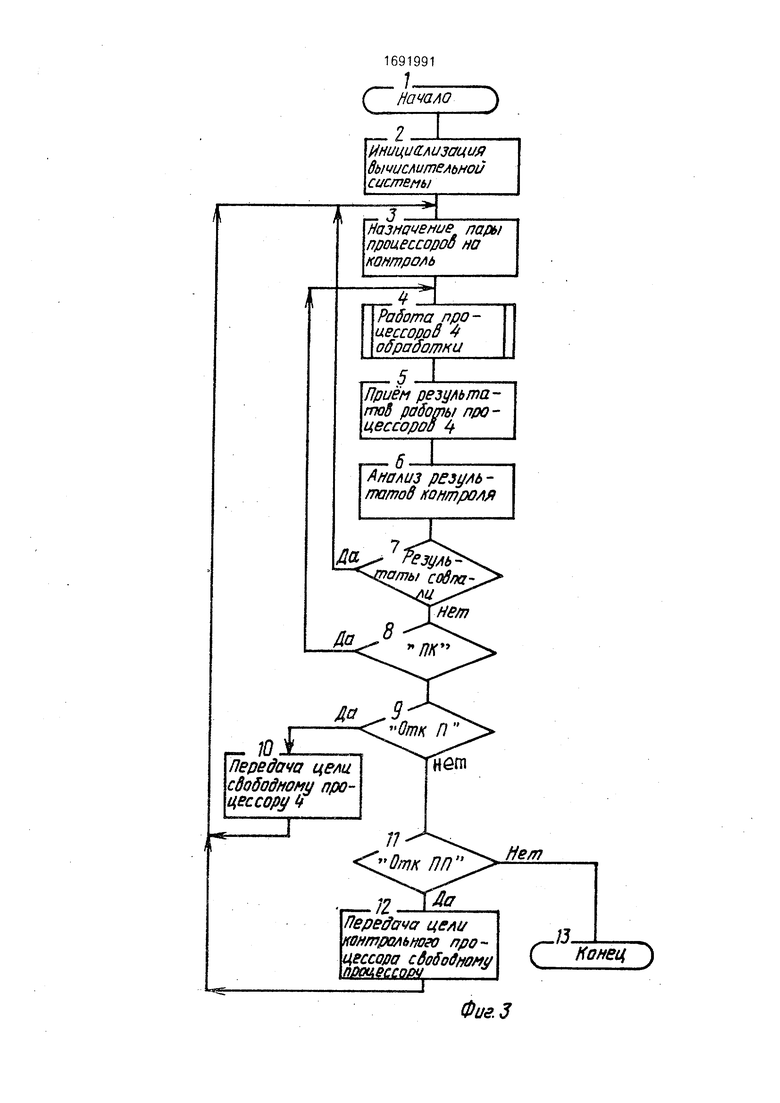

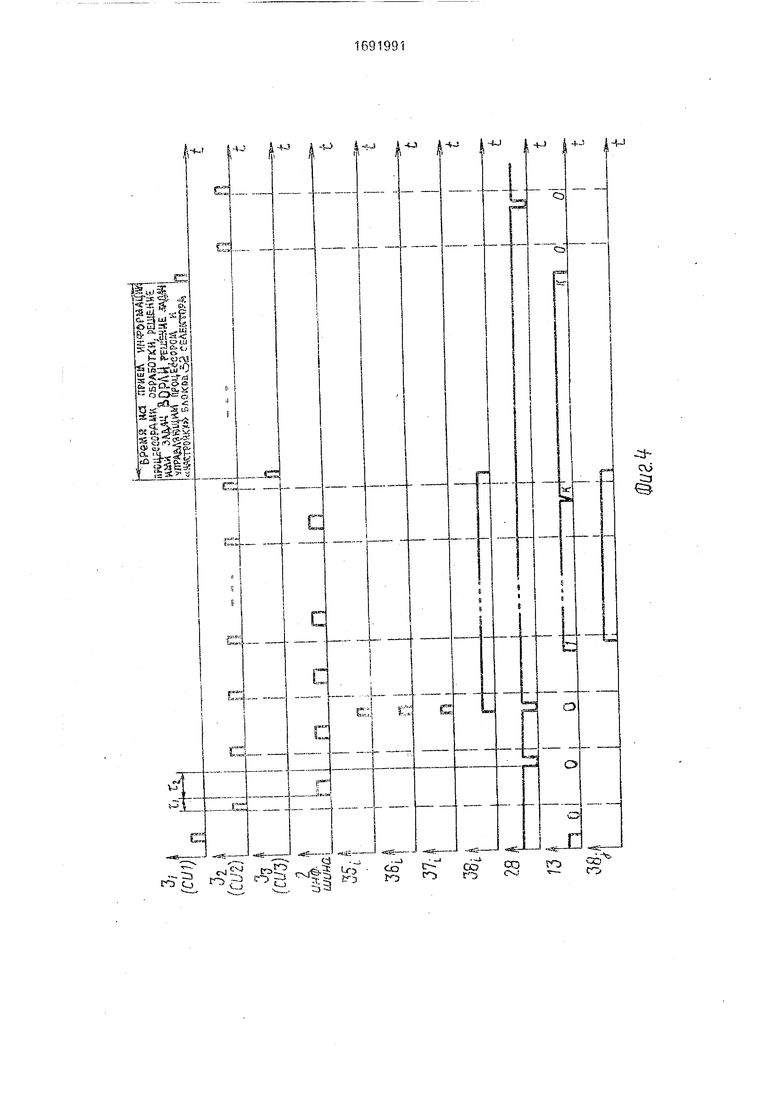

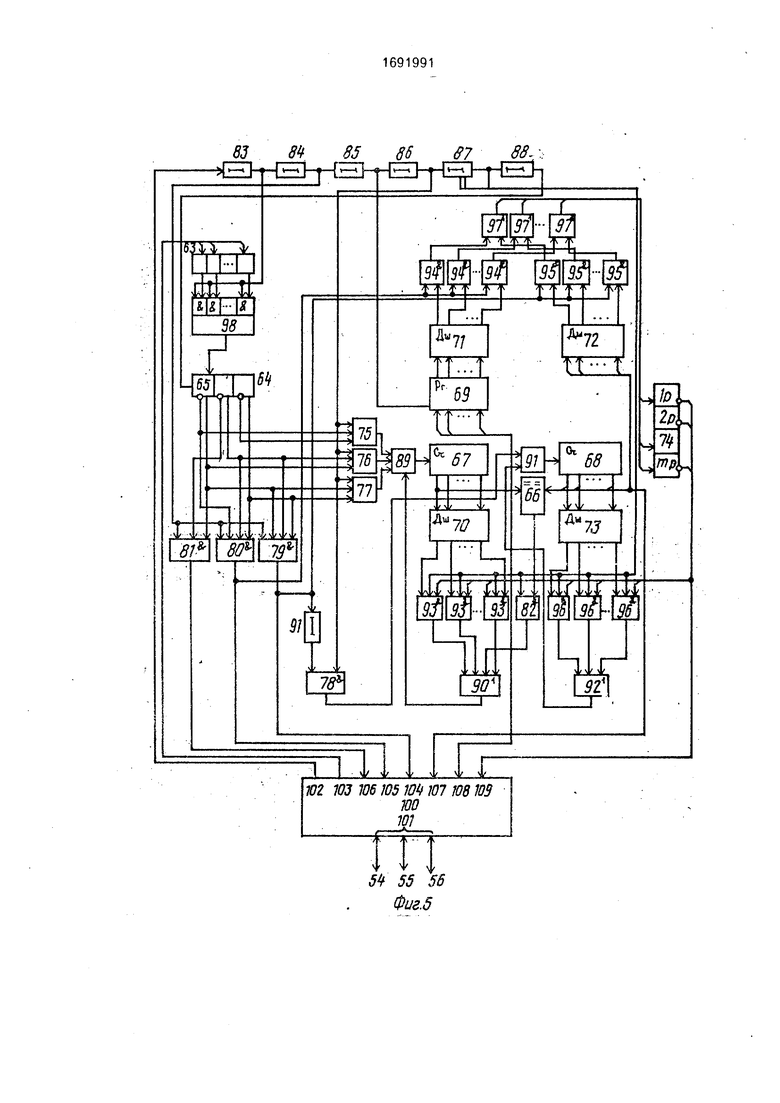

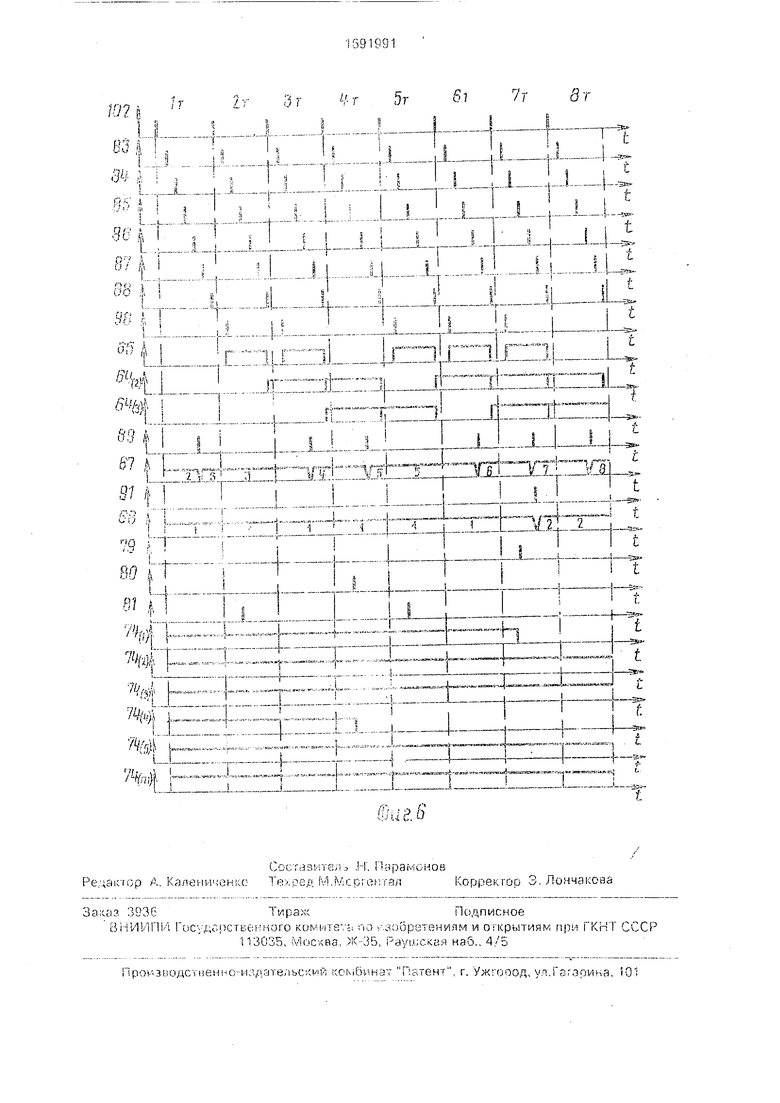

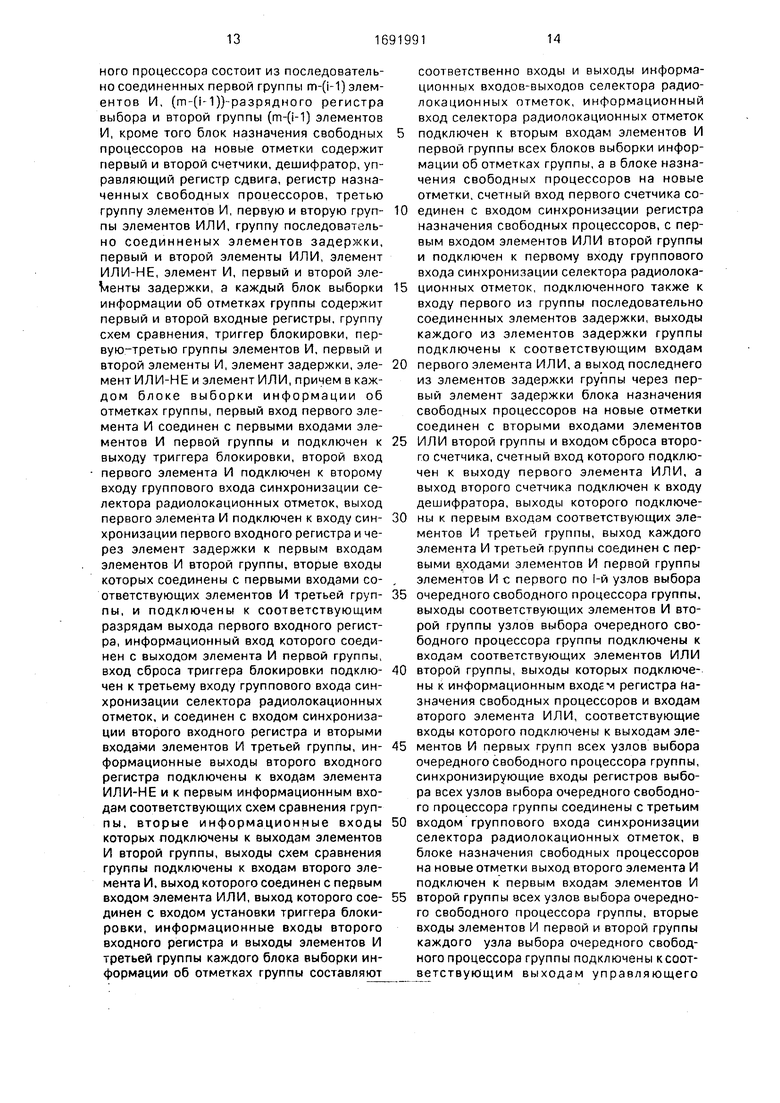

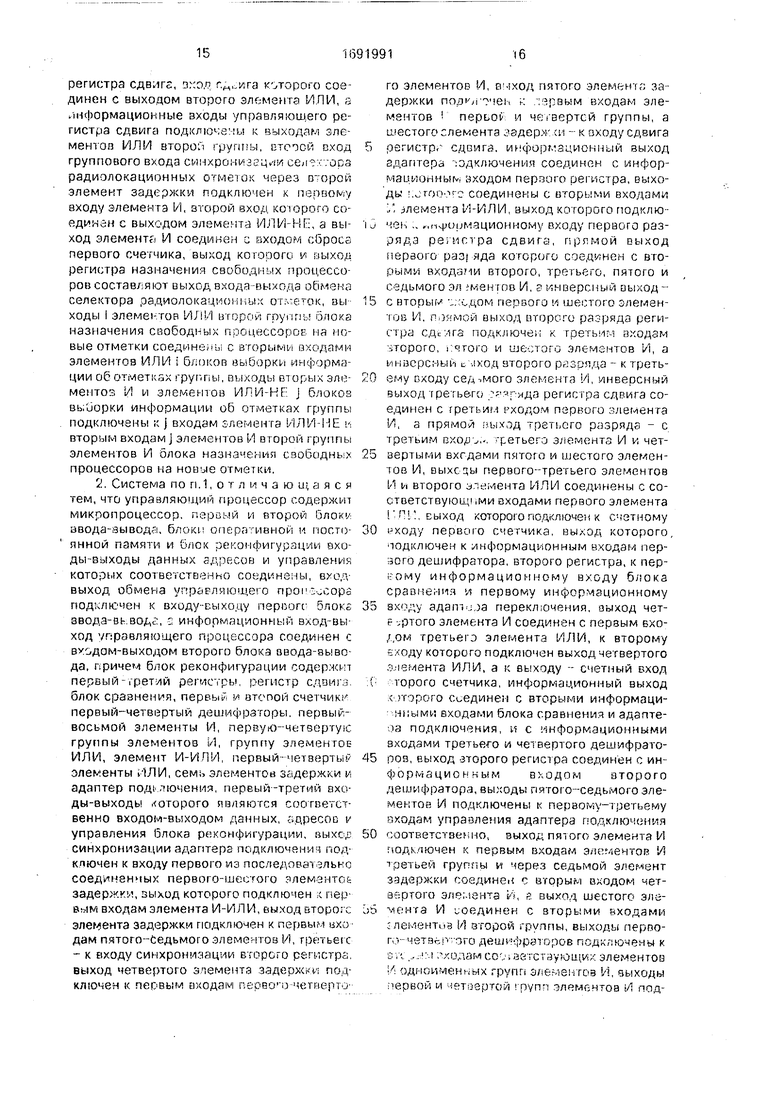

На фиг.1 представлена схема резервированной вычислительной системы; на фиг,2 - схема селектора радиолокационных обмоток; на фиг.З - алгоритм функционирования управляющего процессора; на фиг.4 - временные диаграммы работы селектора радиолокационных отметок; на фиг.5 - схема блока реконфигурации управляющего процессора; на фиг.6 - време чные диаграммы работы блока реконфигурации.

Резервированная вычислительная система (фиг.1) содержит селектор 1 радиолокационных отметок, первые входы 2 которого являются информационными входами системы, вторые входы 3 - синхронизирующие входы селекторы; процессоры обработки 4, первые 5 входы-выходы которых соединены с третьими 6 входами-выходами селектора; управляющий 7 процессор, первые 8 входы- выходы которого через системную шину 9 подлкючены к входам-выходам 10 обмена процессоров обработки и первым 11 выходам селектора.

Селектор 1 (фиг.2) включает: блок 12 назначения свободных процессоров (НСП) на новые отметки, содержащий первый 13 и

Os

О

о о

второй 14 счетчики; дешифратор 15; управляющий 16 регистр сдвига; регистр 17 назначенных свободных процессоров; узлы 18 выбора очередного свободного процессора, состоящие из регистра 19 выбора, первой 20 и второй 21 групп элементов И; третью 22 группу элементов И; первую 23 и вторую 24 группы элементов ИЛИ; последовательно соединенную группу 25 элементов задержки; первый 26 и второй 27 элементы ИЛИ; элемент 28 ИЛИ-НЕ; элемент 29 И, первый 30 и второй 31 элементы задержки. Кроме того, селектор включает: блоки 32 выборки информации об отметках, каждый из которых содержит первый 33 и второй 34 регистры; группу схем сравнения, содержащую первую 35, вторую 36 и третью 37 схемы сравнения; триггер 38 блокировки; первую 39, вторую 40 и третью 41 группы элементов И; первый 42 и второй 43 элементы И; элемент 44 ИЛИ; элемент 45 ИЛИ-НЕ; элемент 46 задержки.

Процессор4 (фиг. 1)обработки выполняется на базе одного из известных микропроцессорных наборов и содержит, например, микропроцессор 47, блоки оперативной 48 (ОП) и постоянной 49 памяти, первый 50 и второй 51 блоки ввода-вывода. Связь между блоками процессора 4 обработки осуществляется через общую внутреннюю шину 52.

Управляющий процессор 7 (фиг.1) содержит микропроцессор (МП) 53, одни выходы которого соединены с шиной 54 адреса процессора, вторые и третьи входы- выходы подключены к шине управления 55 и шине 56 данных. К шине 54 адреса подключены также входы первого 57 и второго 58 блоков ввода-вывода, блоков оперативной 59 и постоянной 60 памяти, блока 61 реконфигурации. Вторые и третьи входы и выходы блоков 57-61 подключены) соответственно к шине 55 управления и шине 56 данных.

Выход блока 58 является входом-выходом 62 системы.

Блок 61 реконфигурации (фиг.5) управляющего 7 процессора содержит; первый 63 регистр; трехразрядный регистр 64 сдвига с младшим разрядом 65; блок сравнения 66; первый 67 и второй 68 счетчики; второй 69 регистр; первый 70, второй 71, третий 72 и четвертый 73 дешифраторы; третий 74 регистр состояния процессоров обработки; первый 75, второй 76, третий 77, четвертый 78, пятый 79, шестой 80. седьмой 81 и восьмой 82 элементы И; первый 83. второй 84. третий 85, четвертый 86, пятый 87 и шестой 88 элементы задержки; первый 89, второй 90, третий 91 и четвертый 92 элементы ИЛИ; первую 93, вторую 94, третью 95 и четвертую 96 группы элементов И; группу 97 элементов ИЛИ; элемент98 И-ИЛИ; седьмой элемент 99 задержки; адаптер 100 подключения; первая 101 группа входов-выходов

которого является входами-выходами блока 61 реконфигурации и подключается к шинам адреса 54, данных 55 и управления 56. Позициями 102-109 обозначены входы и выходы адаптера.

0 Резервированная микропроцессорная система работает в режиме реального масштаба времени. В заданные моменты времени, определяемые циклом обзора РЛС, в селектор 1 из устройства первичной обра5 ботки (УПО) по информационной шине 2 поступает информация об отметках о целях, при этом процесс приема информации селектором синхронизируется синхроимпульсами СИ 1, СИ 2 и СИ 3, выдававемыми 1 ПО

0 по входам. Длительность цикла работы микропроцессорной системы постоянна, и определяется периодом следования синхроимпульсов СИ 1.

Селектор 1 предназначен для установ5 ления соответствия между отметками, поступающими по информационной шине 2 и процессором 4, работающим с данной целью, а также для назначения на отметки о целях, с которыми не работает ни один из

0 процессоров 4, т.е. на отметки о новых целях, свободных процессоров 4, т.е. таких процессоров, которые в очередном такте обработки информации не назначаются на

5 работу с какими-либо уже известными целями. В блоках 32 выборки информации об отметках селектора 1 осуществляется ассоциативное сравнение поступающих с шины 2 отметок с границами строба той цели, ин0 формацию о которой в данный момент обрабатывает соответствующий процессор 4.

Для приема отметок очередного измерения, соответствующий процессор 4 осуществляет настройку своего блока 32

5 выборки информации об отметках, т.е. передает в него для ассоциативного сравнения границы строба, экстраполированных на очередное измерение отметок. Передаваемая процессором 4 информация хранится

0 во втором 34 регистре блока 32. Первый 33 регистр блока 32 предназначен для временного хранения информации о каждой очередной отметке, поступающей по шине 2. Первая 35, вторая 36 и третья 37 схемы

5 сравнения осуществляют сравнение содержимого соответствующих полей первого и второго регистров. Блок 12 назначения свободных процессоров на новые отметки предназначен для сбора информации о номерах свободных процессоров, ее хранения и управления процессом назначения свободных процессоров на новые отметки. Первый 13 счетчик блока 12 предназначен для подсчета числа свободных процессоров, назначенных на новые отметки, а регистр 17 содержит информацию о номерах этих процессоров.

Процессоры обработки предназначены для выполнения алгоритмов вторичной обработки, причем каждый процессор обраба- тывает данные по одной цели. При поступлении очередной отметки в процессор 4 на обработку по входу 5,микропроцессор 47 реализует заданный алгоритм путем выполнения команд, поступающих с блока

49постоянной памяти и используя данные, поступающие с блока 48 оперативной памяти. Блок 51 обеспечивает обмен информацией с управляющим процессором 7. Блок

50осуществляет прием данных на обработку, поступающих от соответствующего блока 32 выборки информации об отметках селектора 1, и выдачу в этот блок эталонной информации о границах строба, т.е. обеспечивает обмен информацией между отдельными узлами блока 32 и микропроцессором 47, а именно, программный доступ микропроцессора 47 ко второму 34 регистру блока 32 (по записи) и к группе 41 элементов И (по считыванию), т.е. к первому 33 регистру. Блок 50 ввода-вывода процессоров 4 управляется непосредственно микропроцессором 47. Соответствующий блок 32 выборки информации об отметках селектора 1, при этом по отношению к блоку 50 ввода-вывода является внешним устройством.

Управляющий процессор предназначен для решения всех задач, не связанных со вторичной обработкой информации, а также выполняет функции контроля правильности функционирования процессоров обработки. Принцип контроля правильности функционирования процессоров 4 заключается в том, что на каждый цикл обработки информации назначается пара взаимопроверяе- мых процессоров, т.е. пара процессоров, реализующих алгоритмы ВОРЛИ для одной и той же цели, что позволяет путем сравнения результатов их работы выявить наличие отказа или сбоя одного из этих процессоров. В случае несовпадения результатов, на следующий цикл пара проверяемых процессоров назначается повторно (повторный контроль). Если при повторном счете вновь не совпадают результаты, то в очередном цикле путем анализа работы следующей проверяемой пары процессоров определяется, какой из процессоров отказывает. Так, если результаты их работы снова не совпадают, то тем самы отказывает контролирующий, работавший в этом и предыдущем

цикле процессор. Если результаты совпадают, то отказывает процессор, контроливав- шийся только в предыдущем цикле. Обмен информацией между процессорами 4 обрз- 5 ботки и управляющим 7 процессором осуществляется по системной шинэ 9 под управлением последнего: осуществляется последовательный опрос процессоров 4 по инициативе управляющего процессора 7.

0Блок 61 реконфигурации управляющего

процессора 7 осуществляет назначение на очередной цикл пары взаимнопроверяе- мых процессоров, по результатам контроля выявлет отказавший процессор и хранит ин5 формацию о работоспособности процессоров 4 обработки.

Первый 67 и второй 68 счетчики задают номера соответственно контролируемого и контролирующего процессоров 4. Состоя0 ние счетчиков 67 и 68 последовательно изменяется, при переполнении счетчики переключаются в исходное состояние.

Регистр 64 сдвига (со сдвигом вправо) обеспечивает хранение результатов контро5 ля пары проверяемых процессоров в течение 3-х циклов, что позволяет определить номер отказавшего процессора 4.

Блок 66 сравнения, осуществляя сравнение содержимого счетчиков 67 и 68, обес0 печивает исключение случаев назначения одного и того же процессора 4 одновременно в качестве контролирующего и контролируемого.

Третий 74 регистр предназначен для

5 хранения информации о работоспособности процессоров 4 обработки. Разрядность регистра определяется количеством процессоров обработки в системе. Единичное значение разрядов регистра 74 указывает,

0 что соответствующие процессоры исправны, нулевое - отказали.

Адаптер 100 обеспечивает подключение блока 61 реконфигурации к внутренним шинам процессора 7. В его функции входит:

5 обеспечение программного доступа микропроцессора 53 к первому 63 регистру (по записи), к третьему 74 регистру (по считыванию), к счетчикам 67 и 68 (по считыванию): передача управляющих сигналов к и от него

0 блоку 61. Периферийными устройствами по отношению к МП 53 Б блоке реконфигурации 61 являются: первый регистр 63, в который записываются результаты сравнения вычислений в паре (контролирующем и кон5 тролируемом) процессорах; регистр 74, с которого считывается информация о номере неисправного процессора 4; счетчики 67 и 68, которые формируют номера контролируемого и контролирующего процессоров 4, соответственно и номера которых передаются в МП 53; элементы И 79-81, с которых в МП 53 считывается управляющая информация в виде сигналов ПК, ОП, ОКП и последовательно соединенные 83-88 элементы задержки, на которые из МП 53 передается управляющий сигнал для синхронизации работы реконфигуратора 61.

Обмен информацией между внутренней магистралью данных МП 53 и адаптером 100 осуществляется через 8-разрядный двунаправленный канал Д.

Для связи с вышеуказанными периферийными узлами реконфигуратора 61 используются 24 линии ввода-вывода, сгруппированные в три 8-разрядных канала ВА, ВВ, ВС, направление передачи информации и режимы работы которых определяются программным способом МП 53.

Основные соединения адаптера 100 описаны на примере, когда в составе системы имеется по четыре основных и резервных процессоров.

Работа резервированной вычислительной системы иллюстрируется с помощью фиг.З, 4 и 6. Последовательность функционирования системы задается управляющим процессором (фиг.З), инициализацией вычислительной системы, назначением пары взаимопроверяемых процессоров 4 обработки, работой процессоров 4 по реализации ВОРЛИ, примером от процессоров 4 результатов обработки РЛИ, анализом результатов взаимопроверяемых процессоров 4.

В результате инициализации вычислительной системы (процедура 2 фиг.З) блоки 48 и 59 оперативной памяти процессоров 4 и 7 загружаются исходными данными, необходимыми для реализации алгоритмов(инициализация происходит через вход 62 системы). В исходном состоянии счетчики и регистры блока 61 реконфигурации устанавливаются в следующие состояния: первый 63 регистр и регистр 64 сдвига - в нулевое состояние, все разряды третьего регистра 74 - в единичное, первый 67 счетчик в состояние 0...010, второй 68 счетчик в состояние 0...01. Все регистры и счетчики селектора 1 в исходном состоянии устанавливаются в нулевое состояние.

Перед началом очередного цикла работы системы с помощью блока 61 реконфигурации назначается пара процессоров 4 для взаимного контроля. С этой целью, программным путем осуществляется считывание, содержимого первого 67 счетчика (номер контролируемого процессора) и второго 68 счетчика (номер контролируемого процессора) микропроцессором 53 управляющего 7 процессора. Затем управляющий

7 процессор передает в процессоры 4 обработки информацию, необходимую для настройки блоков 32 выборки информации об отметках селектора 1 на прием соответствующих отметок. При этом блоки 321 и 322 настраиваются на прием информации одной цели (процедура 3, фиг.З). Настройка блоков 32i и 322 заключается Б записи во вторые 34 регистры информациии о грани0 цах строба зстраполированной на очередное измерение отметки. Запись информации ао вторые 34 регистры осуществляет микропроцессор 47 посредством блока ввода-вывода 50.

5 Затем начинается процесс приема информации об отметках от УПО и распределения ее по процессорам обработки 4. Перед выдачей блока информации об отметках УПО выдает в селектор 1 по входу 3i

0 синхроимпульс СИ 1 (фиг.2 и 4), по которому обнуляется содержимое первого 13 счетчика и регистра 17 назначенных свободных процессоров, в первый разряд управляющего 16 регистра записывается 1, а в осталь5 ныё разряды - нули. СИ 1 поступает на вход первого из последовательно соединенных элементов 25 задержки, и инициирует выдачу на счетный вход второго 14 счетчика последовательности импульсов, благодаря

0 чему в соответствующие регистры 19 узлов 18 выборки очередного свободного процессора заносится информация о номерах свободных процессоров. Если все процессоры свободны, то старшие разряды всех 19 реги5 строе устанавливаются в единичное состояние. Свободность процессора определяется по содержимому второго 34 регистра соответствующего блока 32 выборки информации об отметках (все разряды а нулевом

0 состоянии). Затем УПО выдает по шине 2 Ьгока информацию об отметках, который представляет собой последовательностью кодов, характеризующих отметку и передается параллельно. Каждый раз, перед выда5 чей кода очередной отметки, и после выдачи кода последней отметки, УПО выдает в селектор 1 по входу 32 синхроимпульс СИ 2. СИ 2 поступает на вход второго 31 элемента задержки блока 12 и, если триггер 38 блоки0 ровки блока 32 в нулевом состоянии, т.е. код соответствующей отметка блоком 32зще не принят на вход элемента 46 задержки, то кроме того, обнуляет содержимое первого 33 регистра. После записи информации об

5 очередной отметке (кода очередной отметки) в первый 33 регистр по задержанному сигналу СИ 2 осуществляется ее сравнение с содержимым второго 34 регистра посредством схем 35, 36 и 37 сравнения. Если по итсчении времени, необходимого для анализа информации в схемах 35. 36 и 37 сравнения, на выходах всех трех схем сравнения появятся единичные сигналы, то это свидетельствует о том, что очередная отметка попадает в строб, информация о границах которого хранится во втором 34 регистре блока 32. При этом триггер 38 блокировки переводится в единичное состояние и тем самым блокируется запись информации о последующих отметках в первый 33 регистр блока 32. Задержанный посредством второго 31 элемента задержки, СИ 2 поступает на первый вход элемента 29 И. Если информация о данной отметке не принимается на одним из блоков 32, то на выходе элемента

28ИЛИ-НЕ сохраняется единичный сигнал, который поступает на второй вход элемента

29И. В результате чего, появляющийся на выходе элемента 29 И, единичный сигнал инициирует выборку информации о номере очередного свободного процессора, который назначается на обработку информации сданной отметке. В соответствующий этому процессору 4 блок 32 выборки информации об отметках с выхода элемента ИЛИ группы 24 поступает единичный сигнал, который через элемнет 44 ИЛИ устанавливает соответ- ствующий триггер 38 блокировки в единичное состояние.

По окончании выдачи блока информации об отметках УПО выдает в селектор 1 по входу Зз синхроимпульс СИ 3, по которому содержимое первых 33 регистров всех блоков 32 выборки информации об отметках считывается в блоки оперативной памяти 48 посредством блоков 50 ввода-вывода соответствующих процессоров обработки 4. По СИ 3 обнуляется содержимое вторых 34 регистров и триггеров 38 блокировки блоков 32 и регистров 19 блока 12 НСП. Информация о числе свободных процессоров 4, предназначенных на обработку информации о новых отметках, и номерах этих процессоров считывается с первого 13 счетчика и регистра 17 соответственно микропроцессором 53 управляющего 7 процессора через системную шину 9, посредством ввода-вывода 57, Если возникает такая ситуация, что в блок ОП 48 процессора 4, назначенного на работу по конкретной цели, по СИ 3 считывается нулевая информация, т.е. содержимое первого 33 регистра - нули, то это значит, что в данном такте работы РЛС.ни одна отметка не попадает в заданный строб - происходит пропуск цели.

После приема отметок, процессоры 4 запускаются на их обработку. Результаты реализации алгоритмов ВОРЛИ данного цикла передаются в управляющий 7 процессор, в том числе экстраполированные отметки на следующий цикл измерения, размеры строба и ковариационная матрица ошибок. При получении информации от процес соров 4i и 42 управляющий, процессор 7 5 программно осуществляет сравнение результатов их работы, и код сравнения передает в блок 61 реконфигурации на регистр 63. Одновременно по шине 55 управления выдается сигнал пуска в блок 61. Через вход

0 102 адаптера 100 сигнал пуска поступает на вход группы 83-88 элементов задержки, которая формирует сигналы управления работой блока 61 реконфигурации.

Пусть код сравнения (содержимое реги5 стра 63) равен нулю, т.е. результаты работы проверяемых процессоров 4i и 42 совпадают (1 цикл, фиг.6), тогда по сигналу с выхода первого 83 элемента задержки через элемент 98 И-ИЛ И на вход 65 регистра 64 сдви0 га поступает нулевой сигнал. Ня выходах элементов И 79-81 устанавливаются нулевые сигналы, которые закрывают по одному из входов элементов И 94 и 95, поэтому содержимое регистра 74 не изменяется. По

5 сигналу с выхода элемента 85 задержки содержимое счетчика 67 передается на второй 69 регистр, а по сигналу с выхода элемента 86 задержки через элемент И 75 и элемент ИЛИ 89 содержимое счетчика 67 увеличива

0 ется на единицу, т.е. 0...011. По сигналу с выхода элемента 88 задержки содержимое регистра 64 сдвигается вправо на один разряд. Таким образом, з следующем цикле работы системы взаимно проверяются

5 процессоры 4т и 4з. а на втором 69 регистре хранится номер процессора, который проверялся в предыдущем цикле.

Последовательность назначения пары взаимопроверяемых процессоров показана

0 в таблице.

Управляющий процессоо 7 считывает содержимое счетчиков 67 и С8. и передает в процессор 4i (контролирующий, номер которого определен содержимым счетчика 68)

5 информацию для его настройки на обработку отметок цели, которуюсопровождает(или ведется завязка траектории) процессор 4з. Затем аналогично выполняется обработка отметок цели следующего второго

0 цикла, где результаты работы процессоров 4 также передаются в управляющий процессор.

Если результаты работы проверяемых процессоров 4i и 4з не совпадают (2 цикл,

5 фиг.6), то на вход 65 регистра 64 поступает единичный сигнал, устанавливающий младший разряд 65 в единицу. По сигналу с выхода элемента 84 задержки и состоянию регистра 64 (код 100) на выходе элемента И 81 вырабатывается сигнал ПК (повторный

контроль), который поступает на вход 106 блока 100. В соответствии с состоянием регистра 64 (код 100) закрываются элементы И 75-77 и содержимое счетчика 67 не изменяется. Поэтому в очередном цикле проверяемая пара процессоров также 4f и 4з.

Допустим результаты работы процессоров 4i и 4з вновь не совпадают (3 цикл фиг.6), т.е. один из проверяемых процессоров отказывает, тогда на регистр 63 поступает код отличный от нуля, и в разряд 65 регистра 64 записывается вновь единица. Номер отказавшего процессора определяется в следующем цикле обработки измерений, а на следующий цикл для взаимного контроля назначается пара процессоров 4i и 4/}. Это происходит следующим образом. По сигналу с элемента 85 задержки содержимое счетчика 67 (код 0...011) передается на регистр 69. По сигналу с элемента 86 задержки, и в соответствии с состоянием 110 регистра 64, через элемент И 76 и элемент ИЛИ 89 содержимое счетчика 67 увеличивается на единицу (код 0...0100).

По сигналу с выхода элемнета 88 задержки содержимое регистар 64 будет сдвигаться вправо на 1 разряд.

Если результаты работы процессоров 4i и 44 в четвертом цикле совпадают (4 цикл, фиг.6), то в разряд ОБ регистра 64 записывается нулевое значение. По сигналу с элемента 84 задержки и состоянию регистра 64(код 011) на выходе элемента И 80 появляется сигнал ОП (отказ процессора контролируемого), который поступает на вход 105 адаптера 100 и на входы группы 94 элементов. Номер отказавшего процессора хранится на регистре 69. На соответствующем выходе дешифратора 71 находится единичный сигнал, который открывает один из элементов 94 и устанавливает соответствующий разряд регистра 74 в нулевое Состояние (в нашем случае 3 разряд). Управляющий процессор 7 передает цель обработки информации, которую производит отказавший процессор, свободному процессору 4.

Если же результаты работы процессоров 4i и 44 вновь не совпадают (7 цикл, фиг.6), то принимается решение, что отказывает контролирующий процессор. В этом случае по сигналу с выхода элемента 84 задержки и состоянию регистра 63 (код 111) единичный сигнал вырабатывается на выходе элегиента И 79 ОКП (отказ контролирующего процессора). Через соответствующий элемент И 95, как и при отказе контролируемого процессора, в нулевое состояние устанавливается один из разрядов регистра 74 состояний (1 разряд). По сигналу с выхода элемента 86 задержки через 78 И и

элемент ИЛИ 91 содержимое счетчик 68 увеличивается на единицу, т.е. в качестве контролирующего процессора выступает процессор 42. При этом управляющий процессор передает цель процессора 42 свободному процессору.

При назначении очередной пары процессором для взаимного контроля возможна ситуация, когда содержимое счетчиков 67

0 и 68 указывает номер отказавшего процессора 4, т.е. соответствующий разряд регистра 74 находится в нулевом состоянии. В этом случае по сигналам с выходов элемента 87 задержки через элементы И 93, элемент

5 ИЛИ 90, элемент ИЛИ 89 или элементы И 96, элемент ИЛИ 92, элемент ИЛИ 91, содержимое счетчиков 67 или 68 соответственно увеличивается на 1 (или на 2, или на 3..., в зависимости от количества подряд отказав0 ших процессоров 4, поэтому с выводов элемента 87 задержки снимается несколько сигналов).

Кроме того, если содержимое счетчиков 67 и 68 совпадает, то на выходе блока 66

5 сравнения появляется единичный сигнал, и по очередному сигналу с выхода элемента 87 задержки через элемент 82 И, элемент 90 ИЛИ и элемент 89 ИЛИ, содержимое счетчика 67 еще раз увеличивается на единицу.

0 Таким образом, в каждом цикле последовательно-взаимно контролируется пара процессоров 4 обработки.

Формула изобретения

1. Резервированная вычислительная си5 стема, содержащая группу процесоров обработки, входы-выходы обмена которых объединены через системную шину, отличающаяся тем, что, с целью повышения надежности, в систему введены селектор

G радиолокационных отметок и управляющий процессор, входы-выходы обмена которых подключены к одноименным выходам-входам процессоров обработки группы, информационный вход и групповой

5 вход синхронизации селектора радиолокационных отметок являются одноименными входами системы, информационный вход- выход управляющего процессора является одноименным входом-выходом системы, а

0 информационные входы-выходы процессоров обработки группы подключены к соответствующиминформационнымвыходам-входам селектора радиолокационных отметок, причем селектор радиолокзци5 онных отметок содержит группу блоков эыборки информаци об отметках и блок назначения свободных процессоров на новые отметки, содержащий группу из m узлов выбора очередного свободного процессора, каждый i-й уззл выбора очередного свободного процессора состоит из последовательно соединенных первой группы m-(i-1) элементов И, (т-(Ы))-разрядного регистра выбора и второй группы (m-(i-1) элементов И, кроме того блок назначения свободных процессоров на новые отметки содержит первый и второй счетчики, дешифратор, управляющий регистр сдвига, регистр назначенных свободных процессоров, третью группу элементов И, первую и вторую гругт- пы элементов ИЛИ, группу последовательно соединненых элементов задержки, первый и второй элементы ИЛИ, элемент ИЛИ-НЕ, элемент И, первый и второй эле- 1ченты задержки, а каждый блок выборки информации об отметках группы содержит первый и второй входные регистры, группу схем сравнения, триггер блокировки, пер- вую-третью группы элементов И, первый и второй элементы И, элемент задержки, эле- мент ИЛИ-НЕ и элемент ИЛИ, причем в каждом блоке выборки информации об отметках группы, первый вход первого элемента И соединен с первыми входами элементов И первой группы и подключен к выходу триггера блокировки, второй вход первого элемента И подключен к второму входу группового входа синхронизации селектора радиолокационных отметок, выход первого элемента И подключен к входу син- хронизации первого входного регистра и через элемент задержки к первым входам элементов И второй группы, вторые входы которых соединены с первыми входами соответствующих элементов И третьей труп- пы, и подключены к соответствующим разрядам выхода первого входного регистра, информационный вход которого соединен с выходом элемента И первой группы, вход сброса триггера блокировки подклю- чен к третьему входу группового входа синхронизации селектора радиолокационных отметок, и соединен с входом синхронизации второго входного регистра и вторыми входами элементов И третьей группы, ин- формационные выходы второго входного регистра подключены к входам элемента ИЛИ-НЕ и к первым информационным входам соответствующих схем сравнения груп- пы, вторые информационные входы которых подключены к выходам элементов И второй группы, выходы схем сравнения группы подключены к входам второго элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого сое- динен с входом установки триггера блокировки, информационные входы второго входного регистра и выходы элементов И третьей группы каждого блока выборки информации об отметках группы составляют

соответственно входы и выходы информационных входов-выходов селектора радиолокационных отметок, информационный вход селектора радиолокационных отметок подключен к вторым входам элементов И первой группы всех блоков выборки информации об отметках группы, а в блоке назначения свободных процессоров на новые отметки, счетный вход первого счетчика соединен с входом синхронизации регистра назначения свободных процессоров, с первым входом элементов ИЛИ второй группы и подключен к первому входу группового входа синхронизации селектора радиолокационных отметок, подключенного также к входу первого из группы последовательно соединенных элементов задержки, выходы каждого из элементов задержки группы подключены к соответствующим входам первого элемента ИЛИ, а выход последнего из элементов задержки группы через первый элемент задержки блока назначения свободных процессоров на новые отметки соединен с вторыми входами элементов ИЛИ второй группы и входом сброса второго счетчика, счетный вход которого подключен к выходу первого элемента ИЛИ, а выход второго счетчика подключен к входу дешифратора, выходы которого подключены к первым входам соответствующих элементов И третьей группы, выход каждого элемента И третьей группы соединен с первыми выходами элементов И первой группы элементов И с первого по 1-й узлов выбора очередного свободного процессора группы, выходы соответствующих элементов И второй группы узлов выбора очередного свободного процессора группы подключены к входам соответствующих элементов ИЛИ второй группы, выходы которых подключены к информационным входсм регистра назначения свободных процессоров и входам второго элемента ИЛИ, соответствующие входы которого подключены к выходам элементов И первых групп всех узлов выбора очередного свободного процессора группы, синхронизирующие входы регистров выбора всех узлов выбора очередного свободного процессора группы соединены с третьим входом группового входа синхронизации селектора радиолокационных отметок, в блоке назначения свободных процессоров на новые отметки выход второго элемента И подключен к первым входам элементов И второй группы всех узлов выбора очередного свободного процессора группы, вторые входы элементов И первой и второй группы каждого узла выбора очередного свободного процессора группы подключены ксоот- ветствующим выходам управляющего

регистра сдвига, вход r,Mt,nra которого соеинен с выходом второго элемента ИЛИ, а информационные входы управляющего регистра сдвига подключены к выходам элементов ИЛИ второй группы, ЕТСООЙ сход группового входа синхронизации сел-эк -ора радиолокационных отметок через второй элемент задержки подключен к первому входу элемента И, второй вход которого соединен с выходом элемента ИЛИ-НЕ, а выход элемента И соединен с входом сброса первого счегчика, выход которого и выход регистра назначения свободных процессоров составляют выход входа-выхода обмена селектора радиолокационных отметок, вы ходы I элементов ИЛИ второй группы блока назначения свободных процессоров на новые отметки соединены с вторыми входами элементов ИЛИ i блоков выборки информации об отметках группы, выходы вторых эле- меитоэ И и элементов ИЛИ-НЕ J блоков вь. иорки информации об отметках группы подключены к j входам элемента ИЛИ-НЕ и вторым входам элементов И второй группы элементов И блока назначения свободных процессоров па новые отметки.

2. Система по п.1,отличающаяся тем, что управляющий процессор содержит микропроцессор, первый и второй блоки ввода-вывода, блоки оперативной и посто- янной памяти и Ол о к реконфигурации входы-выходы данных адресов и управления которых соответственно соединены, вход- выход обмена управляющего npoi txcopa подключен к входу-выходу первого блока ввода-вь вода, информационный вход-выход управляющего процессора соединен с входом-выходом второго блока ввода-вывода, причем блок реконфигурации содержит первый-(ретий регистры, регистр сдвига блок сравнения, первый и втеоой счетчики первый-четвертый дешифраторы, первый- восьмой элементы И, первую-четвертую группы элементов И, группу элементов ИЛИ, элемент И-ИЛИ, первый-четвертый элементы ИЛИ, семь элементов задержки и адаптер поди/мочения, первый-третий входы-выходы которого являются соответственно входом-выходом данных, адресов и управления блока реконфигурации, выход синхронизации адаптера подключения подключен к входу первого из последовательно соединенных первого-шеетого элементов задержки, зыход которого подключен к первым входам элемента И-ИЛИ, выход второго элемента задержки подключен к первым входам пятого-седьмого элементов И, третьего - к входу синхронизации второго регистра, выход четвертого элемента задержки подключен к первым входам первопэ-четвертого элементов И, вчход пятого элемента задержки ieii к - эрвым входам элементов перьо и че(вертсй группы, а шестого слемента оадерж си - к входу сдвига

регистре- сдвига, информационный выход адаптера подключения соединен с информационным входом первого регистра, выходы ronorc соединены с вторыми входами .1 элемента И-ИЛИ, выход которого подклюG чек ., „ифоимационному входу первого разряда регистра сдвига, прлмой выход первою раз яда которого соединен с вторыми входами второго, третьего, пятого и седьмого эл менгов И, з инверсный выход 5 с вторым , седом первого и шестого элементов И, Р ямой выход второго разряда регистра сдс -ira подключен к третьим входам атсрого, i чтого и шестого элементов И, а инверсный L .1ход второго разряда - к треть0 ему входу седьмого элемента И, инверсный выход третьего регистра сдвига соединен с третьим РХОДОМ первого элемента И, а прямой -5ЫХОД третьего разряда - с третьим вхоро,-. третьего элемента И и чет5 вергыми вхгдами пятого и шестого элементов И, выходы первого-третьего элементов И и второго слемента ИЛИ соединены с соответствующими входами первого элемента ЦП 1, выход которого подключен к счетному

0 кходу первого счетчика, выход которого подключен к информационным входам первого дешифратора, второго регистра, к nep- кому информационному входу блока сравнения и первому информационному

5 входу адапюа переключения, выход чет- F ,ртого элемента И соединен с первым входом третьего элемента ИЛИ, к второму &лоду которого подключен выход четвертого .элемента ИЛИ, а к выходу - счетный вход

( ,. торого счетчика, информационный выход

огорого соединен с вторыми информациниыми входами блока сравнения и адаптеоз подключения, и с информационными

входами третьего и четвертого дешифрато5 ров, выход зторого регистра соединен с информационным входом второго дешифратора, выходы пятого-седьмого элементов И подключены к первому-третьему входам управления адаптера подключения

0 соответственно, выход пятого элемента И подключен к первым входам элементов И третьей группы и через седьмой элемент задержки соединен с вторым входом четвертого элемента И. в выход шестого эле6 мента И соединен с вторыми входами :лементив И второй группы, выходы перво- го-четвсгпого дешифраторов подключены к о {. ,-,. входам сое.. ззтствующих элементов И одноименных групп элементов И, выходы первой и четвертой i рупп элементов Л подключены к входам второго и четвертого элементов ИЛИ соответственно, а выходы элементов И второй и третьей группы подключены к первым и вторым входам соответствующих элементов ИЛИ группы, выходы которых подключены к информационным входам третьего регистра, инверсные выходы разрядов которого

подключены к третьим входам соответствующих элементов И третьей и четвертой групп и к третьему информационному входу адаптера подключения, а выход блока сравнения подключен к второму входу восьмого элемента И, выход которого подключен к соответствующему входу второго элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| АВТОМАТИЗИРОВАННОЕ РАБОЧЕЕ МЕСТО ОПЕРАТОРА УПРАВЛЕНИЯ ВОЗДУШНЫМ ДВИЖЕНИЕМ | 2001 |

|

RU2219586C2 |

| Устройство для сопряжения К процессоров с М периферийными устройствами | 1987 |

|

SU1432536A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для обработки информации мультипроцессорной системы | 1989 |

|

SU1619288A1 |

| ЦИФРОАНАЛОГОВАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ И ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2022364C1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении параллельных микропроцессорных систем повышенной надежности, в частности для цифровой обработки радиолокационной информации. Система содержит селектор и группу процессоров обработки, входы-выходы которых подключены через системную шину к управляющему процессору. Цель изобретения - повышение надежности системы за счет со- краш,ения длительности существования скрытых отказов. Цель достигается тем, что на каждый цикл работы системы назначается пара взаимопроверяемых процессоров. Это позволяет путем сравнения результатов их работы выявить наличие отказа, или сбоя одного из этих процессоров. Для реализации такого контроля в состав управляющего процессора введен блок реконфигурации. 1 з.п. ф-лы, 6 ил., 1 табл, С

Фиг 7

о

СП

ст to

№

г- 701

Передача цели свободному процессору U

I

г-12

Передача цели контрольного процессора свободному процессому

J

( Начало

Инициализация вычислительной системы

г- J -

Назначение пары процессороо на контроль

Работа процессоров 4 обработки

5Приём результатов работы про цессороВ 4

Анализ резуль - татов контроля

нет

Не/п

.13

( Конец )

J

ФигЗ

Го

-Рг

166L691

1

IT

1т Зг Ч-г 5т

L

f

|Т ,t ,

1 I I S

1 --L JН- ---1-iL jSL J1L

4

t.L

-1-. J

I,

jl J,j,

;,) т

rZ

JT I

--1+-

51sj

U-LJL.

OLI

jL 7 t it-i

Wr

Ж;

.q:::

6i

7т

8т

l-j1

trn

- I-J-I-,

t

,

т

г.

t

те

j

rZZl| CZD. LCUl L

l ilzzrih

Ж

J t

t

It

-9BФиг

| Авторское свидетельство СССР h 1245247,кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кузьмин С.З | |||

| Основы проектирования систем цифровой обработки радиолокационной информации | |||

| М.: Радио и связь, 1986, с.318, рис 8.5. | |||

Авторы

Даты

1991-11-15—Публикация

1989-09-11—Подача