fOСО ©5

Изобретение относится к вычислительной технике и может быть использовано в процессорах вычислительных машин,

Целью изобретения является сокращение аппаратурных затрат.

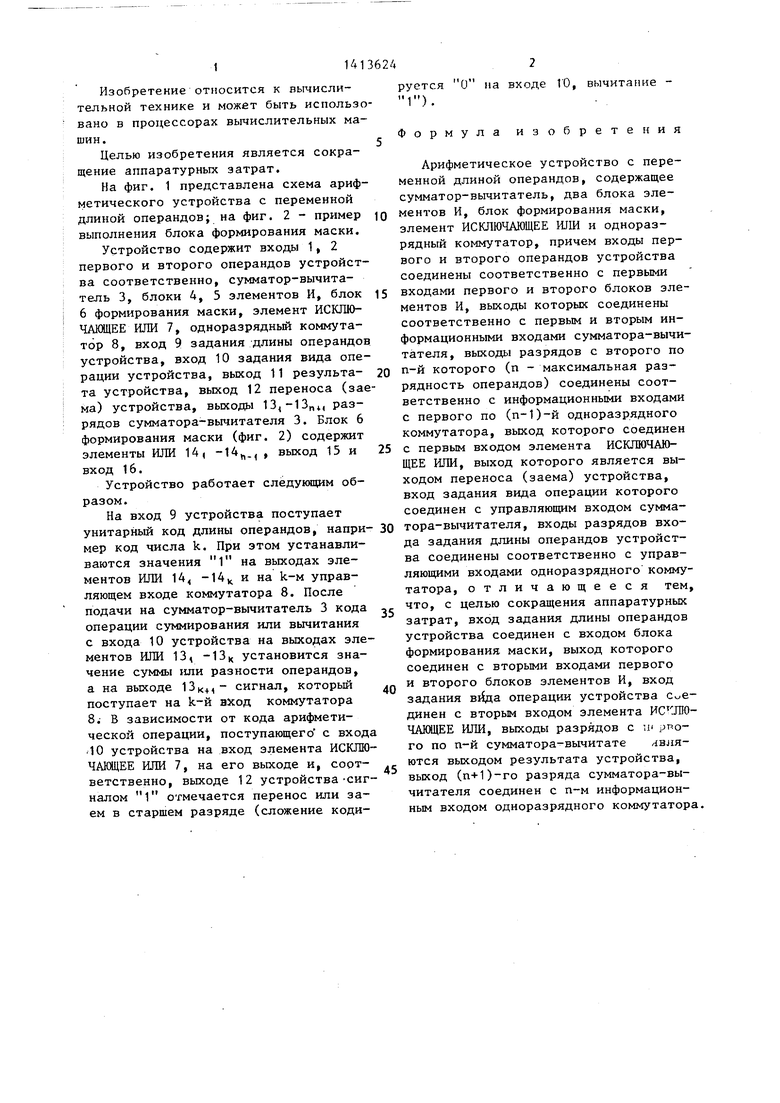

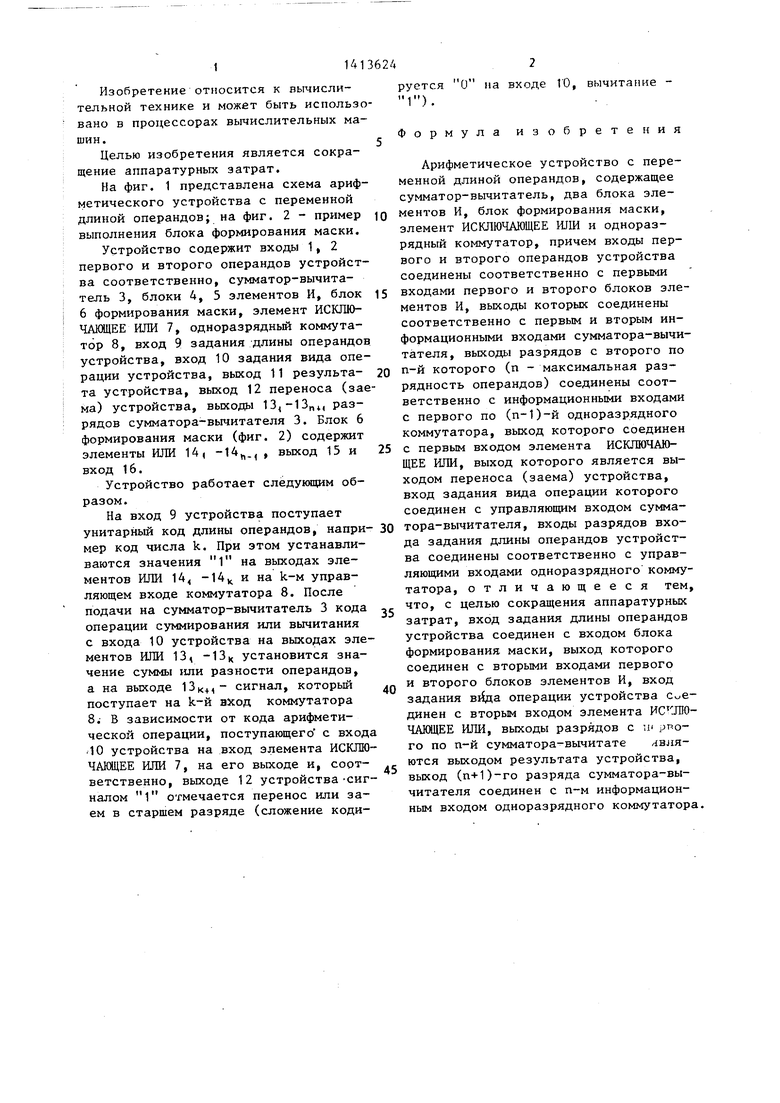

На фиг. 1 представлена схема арифметического устройства с переменной длиной операндов; на фиг. 2 - пример выполнения блока формирования маски.

Устройство содержит входы 1, 2 первого и второго операндов устройства соответственно, сумматор-вычита- тель 3, блоки 4, 5 элементов И, блок 6 формирования маски, элемент ИСКЛЮ- ЧАКЩЕЕ ИЛИ 7, одноразрядный коммутатор 8, вход 9 задания длины операндов устройства, вход 10 задания вида операции устройства, выход 11 результа- та устройства, выход 12 переноса (зае ма) устройства, выходы , разрядов сумматора-вычитателя 3. Блок 6 формирования маски (фиг. 2) содержит элементы ИЛИ 14, -14,, , выход 15 и вход 16.

Устройство работает следукицим образом.

На вход 9 устройства поступает унитарный код длины операндов, напри- мер код числа k. При этом устанавливаются значения 1 на выходах элементов ИЛИ 14 14 и на k-м управляющем входе коммутатора 8. После подачи на сумматор-вычитатель 3 кода операции суммирования или вычитания с входа 10 устройства на выходах элементов ИЛИ 13, -13 установится значение суммы или разности операндов, а на выходе 13к+ сигнал, который поступает на k-й вход коммутатора 8. В зависимости от кода арифметической операции, поступающего с входа .10 устройства на вход элемента ИСКЛЮ- ЧАЩЕЕ ИЛИ 7, на его выходе и, соот- ветственно, выходе 12 устройства Сигналом 1 отмечается перенос или заем в старшем разряде (сложение кодируется О на входе ГО, вычитание - 1).

Формула изобретения

Арифметическое устройство с переменной длиной операндов, содержащее сумматор-вычитатель, два блока элементов И, блок формирования маски, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и одноразрядный коммутатор, причем входы первого и второго операндов устройства соединены соответственно с первыми входами первого и второго блоков элементов И, выходы которых соединены соответственно с первым и вторым информационными входами сумматора-вычитателя, выходы разрядов с второго по п-й которого (п - максимальная разрядность операндов) соединены соответственно с информационными входами с первого по (п-1)-й одноразрядного коммутатора, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом переноса (заема) устройства, вход задания вида операции которого соединен с управляющим входом сумматора-вычитателя, входы разрядов входа задания длины операндов устройства соединены соответственно с управляющими входами одноразрядного коммутатора, отличающееся тем что, с целью сокращения аппаратурных затрат, вход задания длины операндов устройства соединен с входом блока формирования маски, выход которого соединен с вторыми входами первого и второго блоков элементов И, вход задания вида операции устройства динен с вторьм входом элемента ЧАЮЩЕЕ ИЛИ, выходы разрядов с и рро- го по п-й сумматора-вычитате являются выходом результата устройства, выход (п+1)-го разряда сумматора-вычитателя соединен с п-м информационным входом одноразрядного коммутатор

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

| Ассоциативный процессорный модуль | 1981 |

|

SU1015390A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах электронных вычис- .лительных машин. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что арифметическое устройство с переменной длиной операндов, содержащее сумматор-вычитатель 3, блоки 4, 5 элементов И, блок 6 формирования маски, элемент ИСКЛЮЧАЩЕЕ ИЛИ 7 и одноразрядный коммутатор 8, имеет новую организацию связей. 2 ил.

| Патент США 3751650, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Вычислительное устройство с переменной длиной операндов | 1984 |

|

SU1160396A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-30—Публикация

1987-03-09—Подача