11

Изобретение относится к вычисли- тельной технике и может быть использовано при построении операционных устройств высокопроизводительных вычислительных машин.

Известно вычислительное устройство, вьшолняющее операции над полями переменной длины и содержащее регист ры операндов, сумматор, коммутаторы, регистр результата 0}

Недостатком вычислительного устройства является низкое быстродейст,Бие, поскольку вьшолнение операций |над полями переменной длины осуществляются побайтно.

Известно вычислительное устройство, содержащее регистры операндов, регистр результата, сумматор, коммутаторы, регистр маски и преобразователи. В данном устройстве выполнение операции производится одновременно для всего слова {53 .

Недостатком устройства являются значительные аппаратурные затраты.

Наиболее близким по технической сущности к изобретению является вычислительное устройство, содержащее регистры первого и второго операндов, сумматор, блок коррекции, регистр настройки, шифратор, блок логических операций, мультиплексор, блок маскирования и коммутатор, причем первый и второй вькоды сумматора соединены соответственно с входами блока коррекции и мультиплексора, выходы регистров первого и вто;рого операндов соединены с первым и вторым входами сумматора, первым и вторым входами блока логических операций и первым и вторым информационными входами коммутатора, третий и четвертый информационные входы, выход и управляющий вход которого соединены соответственно с выходами сумматора, блока коррекции, первым входом блока маскирования и первым выходом шифратора, первый выход регистра настройки соединен .с первым входом блока коррекции, второй выход регистра настройки - с управляющим входом мультиплексора и вторым входом блока маскирования, первый выход шифратора соединен с вторым входом блока коррекции, второй выход шифратора подключен к третьему входу блока маскирования, выход которого является первым выходом устройства, управлягацие входы регистров операндов, первый.

603962

второй, третий и четвертый входы регистра настройки и вход шифратора являются управляющими входами устройства {3j .

5 Недостатком известного устройства являются значительные аппаратурные затраты и узкая область применения вследствие отсутствия возможности получения старших переменных 0 разрядов операндов.

Цель изобретения - сокращение . количества оборудования.

Поставленная цель достигается

. тем, что вычислительное устройство с -переменной длиной операндов, со-держащее регистры первого и второго операндов, регистр настройки, шифратор операций, арифметико-логический

блок, блок маскирования, первый

мультиплексор и блок коррекции, причем выходы регистров первого и второго операндов соединены соответственно с первым и вторым информа. ционными входами арифметико-логического блока, выходы суммы и переносов которого соединены соответственно с первым и вторым информационными входами блока коррекции, первый и второй управлягацие входы которого соединены соответственно с выходом режима регистра настройки и первым выходом шифратора операций, выход суммы арифметико-логического блока соединен с информационным входом

5 первого мультиплексора, управляющий вход которого соединен с первым управляющим входом блока маскирования и выходом длины маски регистра настройки второй и третий выходы

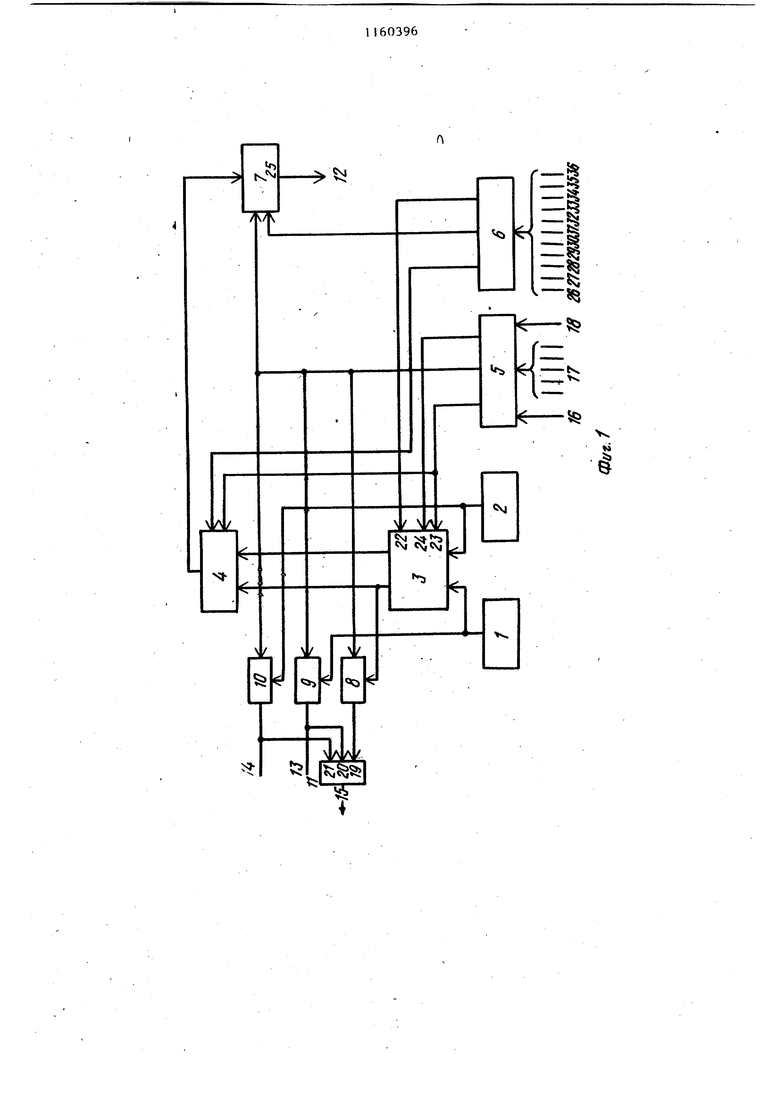

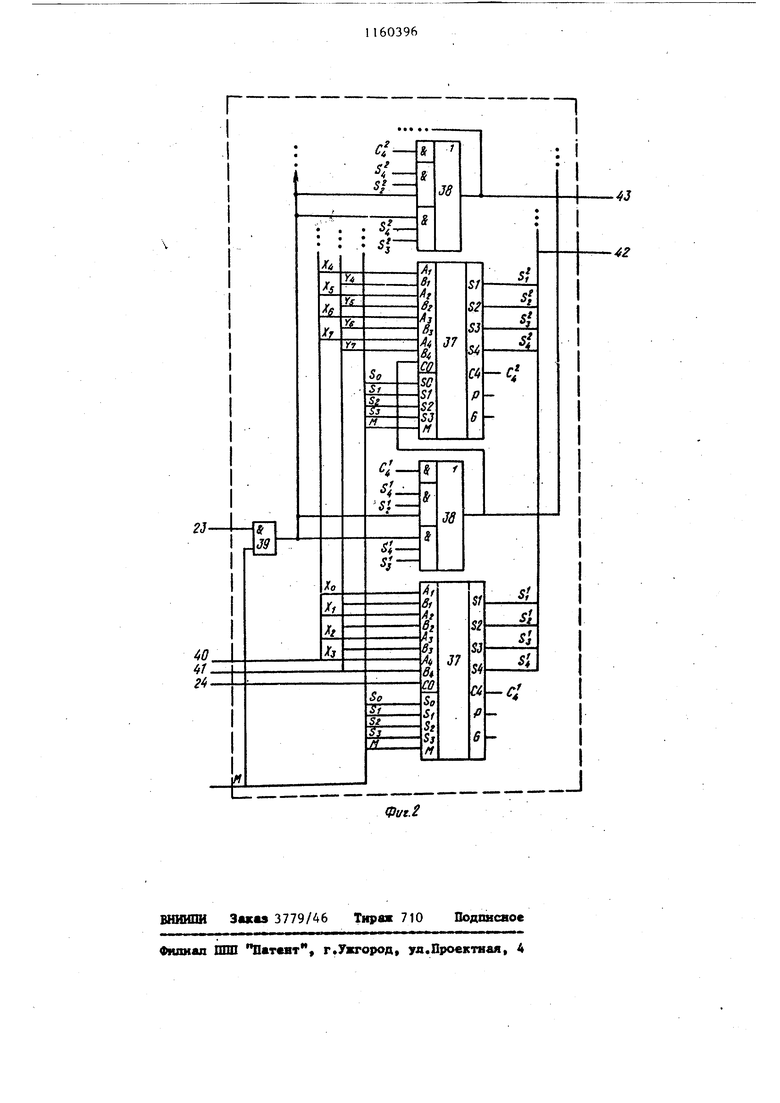

шифратора операций соединены соответственно со вторым управляющим входом.блока маскирования и входом кода операции арифметико-логического блока, входы режима и переноса которого соединены соответственно с выходами режима и переноса регистра настройки, выход блока маскирования является выходом результата устройства, вход шифратора операций явля ется входом вида операций устройства содержит второй и третий мультиплексоры и шифратор переноса, причем выход блока коррекции соединен с информационным входом блока маскирования, выходы регистров первого и второго операндов соединены соответственно с информационными входами второго и третьего мультиплексо3ров, управляющие входы которых соединены с выходами длины маски регистра настройки, выходы первого, второго и третьего мультиплексоров соединены с соответствующими входами шифратора переноса, выход которого является выходом переноса устройства, выходы вто-ро ц1 лг третьего мультиплексоров являются срответственно выходами старших переменных разрядов первого и второго операндоз устройства. На фиг. 1 представлена схема вычислительного устройства с переменнЪй длиной операндовj на фиг. 2 пример схемы арифметико-логического блока. Устройство содержит ркгистр 1 первого операнда, регистр 2 второго операнда, арифметико-логический блок 3, блок 4 коррекции, регистр 5 настройки, шифратор 6 операций, бло 7 маскирования, первый мультиплексор 8, второй мультиплексор 9, третий мультиплексор 1Oj шифратор 11 переноса, выход 12 результата, выхо 13 старшего переменного разряда первого операнда, выход 14 старшего переменного разряда второго операн- да, выход 15 переноса, вход 16 режи ма, входы 17 длины маски, вход 18 переноса, входы 19-21 второго шифра тора 11 входы 22-24 кода операции режима и переноса блока 3 суммирования, выход 25 блока маскирования входы 26-36 вида операций. Арифметико-логический блок 3 (фиг. 2) содержит арифметико-логиче кие четырехразрядные узлы 37, реализованные на микросхемах 100 ИП 181, элементы И-ИЛИ 38, элемент И 3 входы 40 и 41 операндов, выходы 42 суммы и 43 переносов. Шифратор 11 переноса осуществляет выработку переноса из старшего переменного разряда результата: : Вход 20 О О 1 1 О 1 О 1 Вход 21 О 1 О 1 О О .1 1 Вход 19 00001111 Выход 15 О 1 1 1 О О О 1 Блок 7 маскирования аналогичен известному. Входная информация, поступающая на вход блока 7 маскир вания, проходит на выход 25 без из менения при полной маске или на выход только те разряды, которйе м кируются полем единиц. 64 Семиразрядньй регистр 5 настройки содержит данные, необходимые для работы вычислительного устройства переменной длиной. Первьй разряд (вход 16 и первьй выход регистра 5 настройки) - двоичная или двоичнодесятичная арифметика, В первом случае информация с выхода блока 3 проЗгоди-г тгрез блок 4 коррекции без изменения. Во втором случае осуществляется коррекция результата в соответствии со значениями тетрадных переносов. Второй - шестой разряды (вход 17 и второй выход регистра 5 настройки) - параметр длины маски. Седьмой разряд (вход 18 и третий выход регистра 5 настройки) - перенос в младший разряд устройства. Шифратор 6 операций осуществляет преобразование сигналов вида операции в сигналы управления арифметикологическим блоком и блоком маскирования согласно таблицы. Устройство работает следующим образом. На регистры 1 и 2 принимаются операнды. На регистр 5 настройки заносится код, определяющий вьтолнекие двоичных или двоично-десятичных 1рифметических операций, длину операндов и перенос в мпадший разряд. На шифратор 6 операций по одному из входов 26-36 поступает информация о виде операции, которую следует вьшолнить, Операнды поступают на вход блока, где по коду операции на входе 22, по режиму работы на входы 23 и с учетом переноса на входе 24 выполняется заданная операция. Результат с блока 3 поступает на блок 4 коррекции, где в случае двоично-десятичной арифметики производится необходимая коррекция в зависимости от того, сложениеИЛИ вычитание выполнялось в устройстве. При двоичной арифметике результат передается через блок 4 коррекции без изменения на вход блока 7 маскирования. По значению длины маски, поступакидей с выхода длины маски регистра 5 наст- . ройки, и разрешению маскирования, поступающему с выхода шифратора 6 операций, получаем на выходе 25 блока .7 маскирования результат, у которого в разрядах с номерами большими, чем значение кода длины маски будут нули, С выхода 25 блока 7 маекирования поступает на выход 12 результата устройства.

Значения операндов с выходов регистров 1 и 2 и значение суммы с выхода блока 3 поступают на входы мультиплексоров 9, 10 и 8, где по значению кода длины маски производится выбор старших переменных разрядов операндов и суммы. Получещ; --.™--- чения поступают на шифратор 11 пе- ю

реноса, на выходе которого появляется сигнал, равный единице, если имел место перенос из переменного старшего разряда блока 3, и нуль .в противном случае.

При работе с двоично - деся тичной арифметикой значение переноса из . старшегопеременно го разряда , как ив известном устройстве неучитывает ся.

Положительный эффект изобретения состоит в сокращении количества оборудования ..тро5уемого для реализации устройства (из состава устройлогических операций, объем оборудования которых существенно больше, чем введенных двух мультиплексоров, и шифратор переноса). Кроме того., в предложенном устройстве определяются также старшие переменные разряды операндов. ства исключаются коммутатор и блок

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Операционное устройство | 1982 |

|

SU1113805A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| Устройство для предварительной обработки операндов переменной длины | 1984 |

|

SU1269147A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

| Устройство для выполнения арифметических и логических операций над словами | 1978 |

|

SU767757A1 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

| Устройство для арифметической и логической обработки двоичных и двоично-десятичных @ -разрядных чисел | 1980 |

|

SU962922A1 |

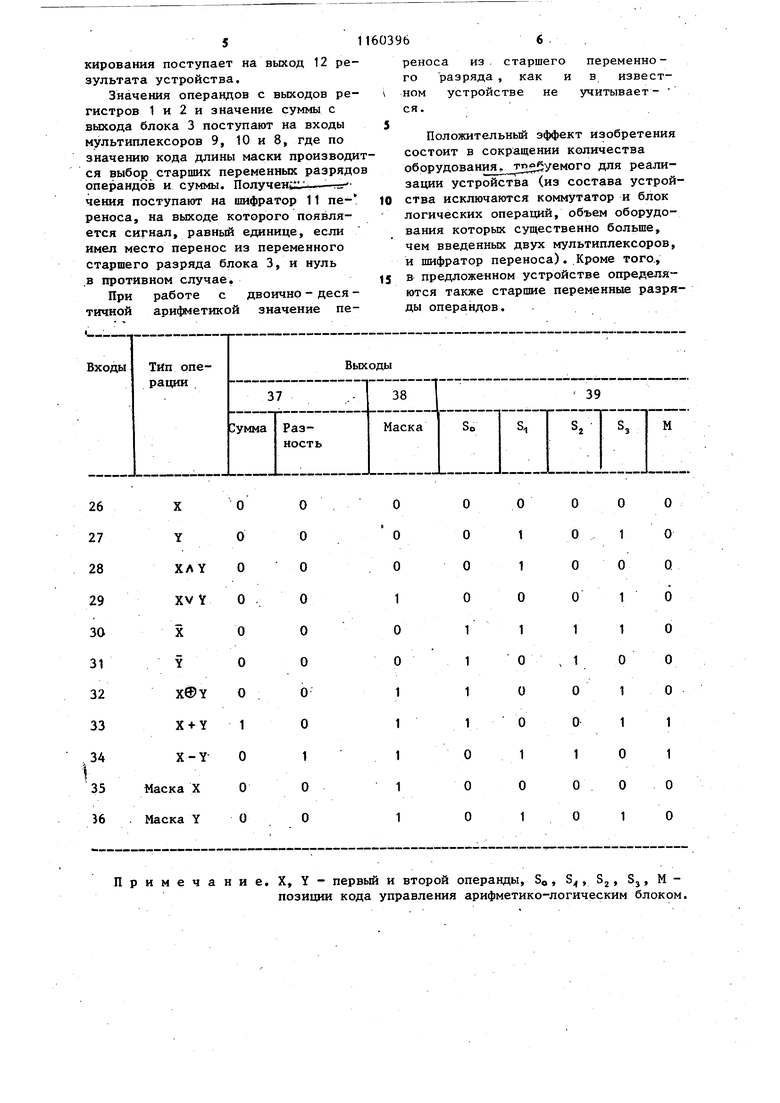

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С ПЕРЕМЕННОЙ ДЛИНОЙ ОПЕРАНДОВ, содержащее регистры первого и второго операндов, регистр настройки, шифратор операций, арифметико-логический блок, блок маскирования, первый мультиплексор и блок коррекции, причем выходы регистров первого и второго операндов соединены соответ- ственно с первым и вторым информационными входами арифметико-логического блока, выходы суммы и переносов которого соединены соответственно с первьм и вторым информационными входами блока коррекции, первый и второй управлякяцие входы которого соединещ 1 соответственно с выходом режима регистра настройки и первым выходом шифратора операций, выход суммы арифметико-логического блока соединен с информационным входом первого мультиплексора, управляющий вход которого соединен с первым управляющим входом блока маскирования и выходом длины маски регистра настройки, второй и третий выходы шифратора операций соединены соответственно с вторым управляющим входом блока маскирования и входом кода операции арифметико-логического блока, входы режима и переноса которого соединены соответственно с выходами режима и переноса регистра настройки, выход блока маскирования является выходом результата устройства, вход шифратора операций является входом вида операций устройсттем. ва, отличающееся что, с целью сокращения количества (Л оборудования, оно содержит второй и третий мультиплексоры и В1ифратор переноса, причем выход блока коррекции соединен с информационным входом блока маскирования, выходы регистров первого и второго операндов соединены соответственно с информационными входами второго и третьего мультиплексоров, управляющие входы которых соединены с выходами длины маски регистра настройки, выходы со первого, второго и третьего мульти;о плексоров, соединены с соответствую05 щими входами шифратора переноса, выход которого является вькодом:. переноса устройства,выходы второго и третьего мультиплексоров являются соответственно выходами старших переменных разрядов первого и второго операндов устройства.

Примечание. X, Y- первый и второй операнды. So, S, 5 , Sj, М позиции кода управления арифметико-логическим блоком.

Г

п

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Проектирование микропроцессоров на основе стандартных логических приборов | |||

| Электроника, 1975, № 2, с; 43 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1985-06-07—Публикация

1984-01-11—Подача