(61) 1309279

(21)4206971/24-21

(22)23.01.87

(46) 30.07.88. Бюл. № 28

(72) С.А.Колесов, Ю.В.Соколов,

В.В.Бовырин и В.Г.Семёнов

(53)621.374 (088.8)

(56)Авторское свидетельство СССР № 1309279, кл. Н 03 К 5/135,

JIO.OI.86.

(54)ФАЗОВЫЙ СИНХРОНИЗАТОР

(57)Изобретение относится к устройствам импульсной техники и может быть использовано в качестве элемента временной привязки периодического сигнала к внешнему асинхронному сигналу в системах синхронизации

ЭВМ. Цель изобретения - повьшение точности синхронизации - достигается за счет учета тока производных входного и ортогонального к нему сигналов в момент синхронизации, что обеспечивает надежность синхронизации ЭВМ. Фазовый синхронизатор содержит входные шины I и 19, элемент 2 задержки, аналоговые запоминающие устройства 3 и 4, устройства 5 и 6 выделения модуля, компараторы 7 - II, D-триггеры 12, 13 и 14, коммутаторы 15, 16 и 17, выходную шину 18. Устройство обеспечивает высокую точность и позволяет получить относительную погрешность фазовой синхронизации менее 1%, что на два порядка выше, чем у прототипа. I ил.

с б

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый синхронизатор | 1986 |

|

SU1309279A1 |

| Фазовый синхронизатор | 1985 |

|

SU1256176A1 |

| Фазовый синхронизатор | 1987 |

|

SU1443147A1 |

| Устройство для функционального контроля больших интегральных схем | 1985 |

|

SU1291905A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| Одноканальное устройство для фазового управления статическим преобразователем | 1977 |

|

SU736344A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| ЭЛЕКТРИЧЕСКИЙ ИМИТАТОР АККУМУЛЯТОРНОЙ БАТАРЕИ С ЗАЩИТОЙ ПО ТОКУ И НАПРЯЖЕНИЮ И УСТРОЙСТВО ЗАЩИТЫ ЭЛЕКТРИЧЕСКОГО ИМИТАТОРА АККУМУЛЯТОРНОЙ БАТАРЕИ | 2016 |

|

RU2635897C1 |

| Фазовый синхронизатор | 1990 |

|

SU1739491A1 |

со

о

00

N

Изобретение относится к элементам импульсной техники, может применяться в качестве элемента временной привязки периодического сигнала к внешнему асинхронному в системах синхронизации ЭВМ и является усовершенствованием известного по авт. св. № 1309279.

Цель изобретения - повьшенйе том- ности синхронизации за счет учета тока производных входного и ортогонального к нему сигналов в момент синхронизации, что обеспечивает надежность синхронизации ЭВМ.

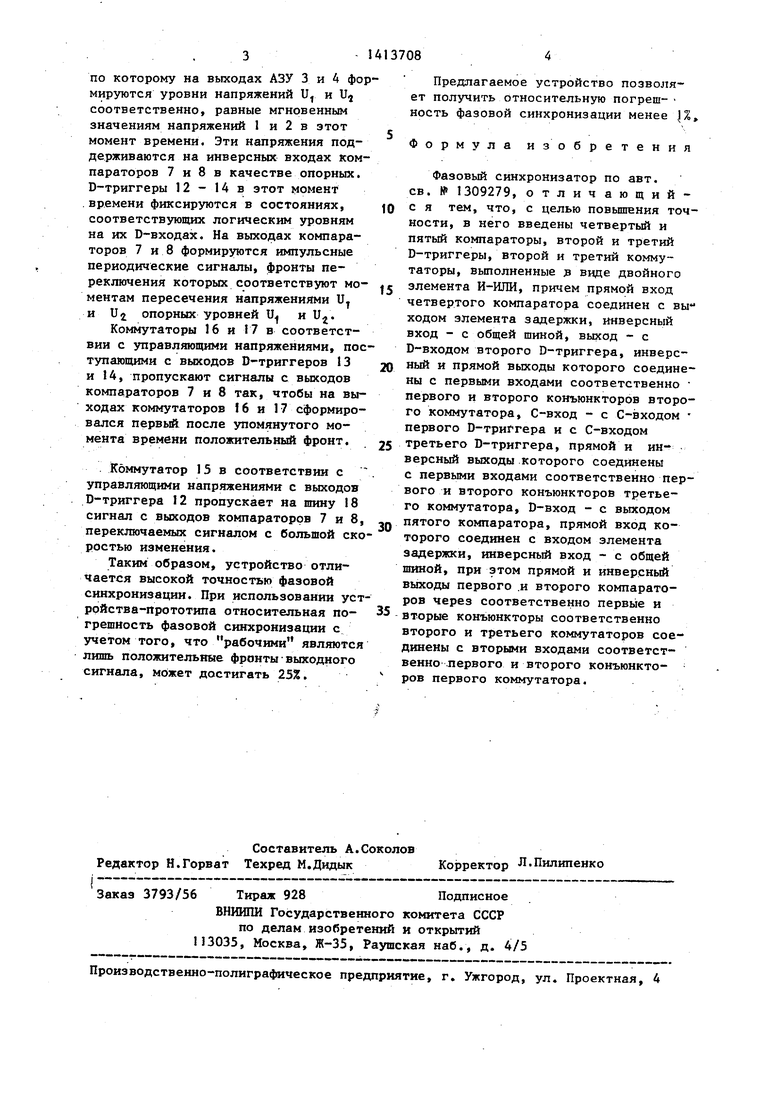

На чертеже приведена электрическая ст руктурная схема фазового синхронизатора.

Фазовый синхронизатор содержит первую входную шину 1, элемент 2 за- держки, первое и второе аналоговые запоминающие устройства АЗУ 3 и 4, первое и второе устройства 5 и 6 выделения модуля УВМ, первый, второй, третий, четвертый и пятый компарато- ры 7 - 11, первый, второй и третий D-триггеры 12 - 14, первый, второй и третий коммутаторы 15 - 17, вьгход- ную шину 18 и вторую входную шину 19. ,Первая входная шина 1 соединена со входом элемента 2 задержки, с аналоговым входом первого АЗУ 3, со входом первого УВМ 5 и с прямыми входами первого и пятого компараторов 7 и 11 . Вторая входная шина 19 сое ди- нена со входами синхронизации первого и второго АЗУ 3 и 4 и С-входами первого, второго и третьего D-тригге- ров 12 - 14. Выход элемента 2 задержки соединен с аналоговым входом вто- рого АЗУ 4, со входом второго УВМ 6 и с прямыми входами второго и четвер- того компараторов 8 и 10. Выходы первого и второго УВМ 5 и 6 соединены соответственно с прямым и инверсным входами третьего компаратора 9, выход которого соединен с D-входом первого D-триггера 12. Инверсный вход четвертого компаратора 10 соединен с общей шиной, выход - с D-входом вто- рого D-триггера 13. Инверсный выход пятого компаратора 11 соединен с общей шиной, выход - с D-входом третьего D-триггера 14. Инверсные входы первого и второго компараторов 7 и 8 соединены с выходами соответственно первого и второго АЗУ 3 и 4. Выходная шина 18 соединена с выходом первого коммутатора 15, первые входы

первого и второго конъюнкторов ко - торого соединены соответственно с инверсным и прямым входами первого D-триггера 15. Вторые вхоДы первого и второго конъюнкторов первого ком- мутатора 15 соединены с выходами соответственно второго и третьего коммутаторов 16 и 17. Инверсный и прямой выходы второго D-триггера 13 соединены с первыми входами соответственно первого и второго конъюнкторов второго коммутатора 16. Прямой и инверсный выходы третьего D-триггера 1 соединены с первыми входами соответственно первого и второго конъюнкто ров третьего коммутатора 17. Вторые входы первого и второго конъюнкторов второго коммутатора 16 соединены соответственно с прямым и инверсным выходами первого компаратора 7. Вторые входы первого и второго конъюнкторов третьего коммутатора 17 соединены соответственно с прямым и инверсными выходами второго компаратора 8.

Устройство работает следующим образом.

На шину 1 поступает гармонический сигнал

2 i Ui А cos ---t;

после прохождения элемента задержки, время задержки .которого составляет t-j Т/4, сигнал имеет вид:

и 2 А cos (-- -t + -2) А sin .

Сигналы и и и поступают на входы УВМ 5 и 6, на выходах которых соответственно формируются сигналы - |Ui I и lUjl.

На выходе компаратора 9 присутствует уровень 1 (о) в те моменты времени, когда скорость изменения сигнала U больше (меньше), чем и, . На -выходах компараторов 10 и 11 формируется уровень 1 (О) в те моменты времени, когда мгновен- ные значения U. и U больше(меньше) нуля. Учитьшая, что U/| U и и -и, логические уровни напряжений на выходах компараторов 10 и I1 соответствуют мгновенным знакам производных и ч, и и .

В некоторый момент времени на шину 19 приходит асинхронный сигнал.

по которому на выходах АЗУ 3 и А формируются уровни напряжений U и Uj соответственно, равные мгновенным значениям напряжений 1 и 2 в этот момент времени. Эти напряжения поддерживаются на инверсных входах компараторов 7 и 8 в качестве опорных. D-триггеры 12 - 14 в этот момент . времени фиксируются в состояниях, соответствующих логическим уровням на их D-входах. На выходах компараторов 7 и 8 формируются импульсные периодические сигналы, фронты переключения которых соответствуют моментам пересечения напряжениями U и и опорных уровней U и Uj.

Коммутаторы 16 и 17 в соответствии с управляющими напряжениями, поступающими с выходов D-триггеров 13 и 14, пропускают сигналы с выходов компараторов 7 и 8 так, чтобы на выходах коммутаторов 16 и 17 сформировался первьй после упомянутого момента времени положительный фронт.

Коммутатор 15 в соответствии с управляющими напряжениями с выходов D-триггера 12 пропускает на шину 18 сигнал с выходов компараторов 7 и 8, переключаемых сигналом с больщой скоростью изменения.

Таким образом, устройство отличается высокой точностью фазовой синхронизации. При использовании уст10

15

20

25

30

Предлагаемое устройство позвол ет получить относительную погрешность фазовой синхронизации менее

Формула изобретен

Фазовый синхронизатор по авт. св. № 1309279, отличающи с я тем, что, с целью повышения ности, в него введены четвертый и пятый компараторы, второй и трети D-триггеры, второй и третий комму таторы, вьтолненные в виде двойно элемента И-ИЛИ, причем прямой вхо четвертого компаратора соединен с ходом элемента задержки, инверсны вход - с общей шиной, выход - с D-входом второго D-триггера, инве ный и прямой выходы которого соед ны с первыми входами соответствен первого и второго конъюикторов вт го коммутатора, С-вход - с С-вход первого П-триГгера и с С-входом третьего D-триггера, прямой и ин версный выходы которого соединены с первыми входами соответственно вого и второго конъюнкторов треть го коммутатора, D-вход - с выходом пятого компаратора, прямой вход к торого соединен с входом элемента задержки, инверсный вход - с общей шиной, при этом прямой и инверсны выходы первого .и второго компарато ров через соответственно первые и

ррйства-прототипа относительная по- 35 вторые конъюнкторы соответственно

грешность фазовой синхронизации с учетом того, что рабочими являются лишь положительные франтывыходного сигнала, может достигать 25%.

второго и третьего коммутаторов со динены с вторыми входами соответст венно .первого и второго конъюнкторов первого коммутатора.

Предлагаемое устройство позволяет получить относительную погреш ность фазовой синхронизации менее %,

Формула изобретения

Фазовый синхронизатор по авт. св. № 1309279, отличающий- с я тем, что, с целью повышения точности, в него введены четвертый и пятый компараторы, второй и третий D-триггеры, второй и третий коммутаторы, вьтолненные в виде двойного элемента И-ИЛИ, причем прямой вход четвертого компаратора соединен с вы ходом элемента задержки, инверсный вход - с общей шиной, выход - с D-входом второго D-триггера, инверсный и прямой выходы которого соединены с первыми входами соответственно первого и второго конъюикторов второго коммутатора, С-вход - с С-входом первого П-триГгера и с С-входом третьего D-триггера, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго конъюнкторов третьего коммутатора, D-вход - с выходом пятого компаратора, прямой вход которого соединен с входом элемента задержки, инверсный вход - с общей шиной, при этом прямой и инверсный выходы первого .и второго компараторов через соответственно первые и

вторые конъюнкторы соответственно

второго и третьего коммутаторов соединены с вторыми входами соответственно .первого и второго конъюнкторов первого коммутатора.

Авторы

Даты

1988-07-30—Публикация

1987-01-23—Подача