1

Изобретение относится к имнульсной технике и может быть использовано в синтезаторах частот и в устройствах обработки асинхронной информации.

Целью изобретения является повышение точности фазовой синхронизации периодического сигнала внешним асинхронным сигналом.

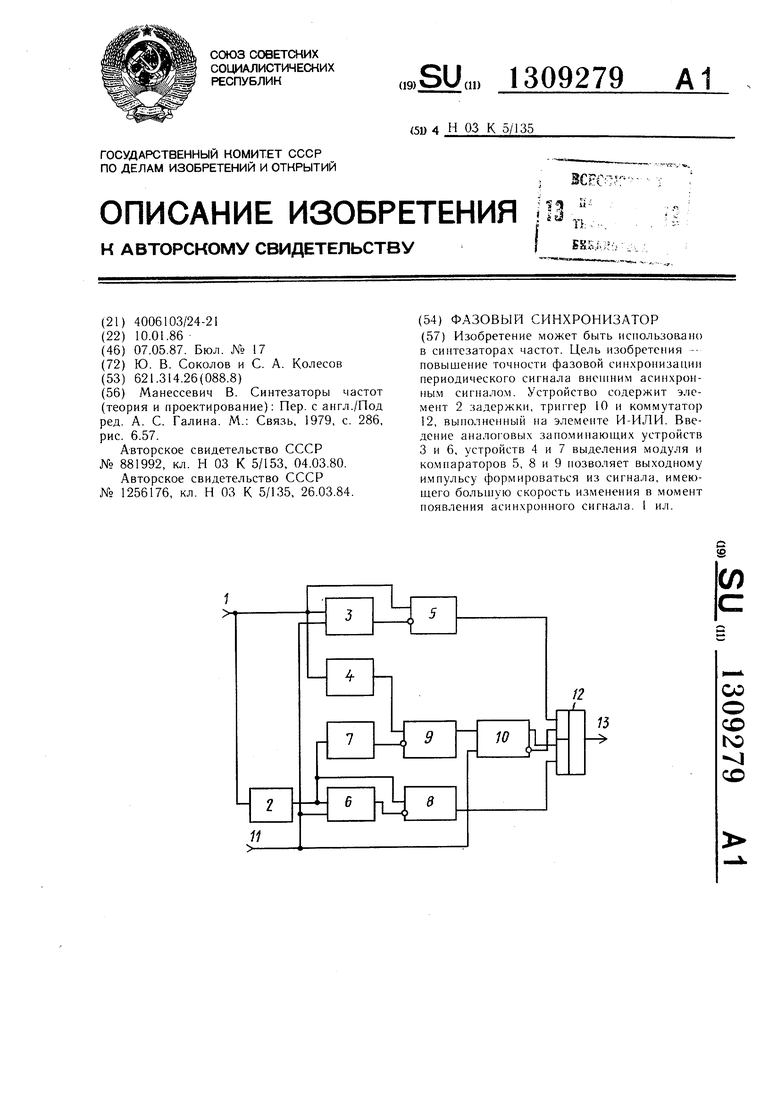

На чертеже приведена электрическая структурная схема устройства.

Фазовый синхронизатор содержит шину 1 периодического (гармонического) сигнала, которая соединена с входом элемента 2 задержки, с аналоговым входом первого аналогового запоминаюпдего устройства 3, с входом первого устройства 4 выделения мо.дуля, а также с прямым входом первого компаратора 5, инверсный вход которого соединен с выходом первого аналогового за- поминаюшего устройства 3, к выходу элемента 2 задержки подсоединены аналоговый вход второго аналогового запоминающего устройства 6, вход второго устройства 7 выделения модуля и прямой вход второго компаратора 8, инверсный вход которого соединен с выходом второго аналогового запо- минаюшего устройства 6. Выходы первого 4 и второго 7 устройств выделения модуля соединены соответственно с прямым и с инверсным входами третьего компаратора 9, выход которого, соединен с D-входом триггера 10 (D-типа). Импульсные входы первого 3 и второго 6 аналоговых запоминающих устройств и триггера 10 соединены с иди- ной 11 асинхронного сигнала. Инверсный и прямой выходы триггера 10 соедииенрз с первыми входами соответственно первого и второго конъюнкторов коммутатора 12, выполненного на элементе И-ИЛИ, втор)е входы которых соединены с выходами соответственно первого 5 и второго 8 компараторов, выход коммутатора 12 соединен с выходной шиной 13.

Устройство работает следующим образом.

На шину 1 поступает гармонический сигнал и, ACos- t. После прохождения элемента 2, время задержки которого составляет , сигнал имеет вид: U

А Cos(t + |-) А .

Сигналы Ui и Ua поступают на входы устройств 4 и 7 соответственно, на выходах которых формируются сигналы Uj и О,. Здесь используется то свойство функций Sinx и Cos X, что они взаимно являются производными одна от другой. Выходы устройств 4 и 7 соединены с входами компаратора 9, на выходе которого присутствует уровень «Лог. 1 в те моменты времени, ког

3092792

да скорость изменения сигнала Uj больше, чем у LJ(, либо уровень «Лог. О в те моменты времени, когда скорость изменения сигнала Ui меньше, чем у Ut.

В момент времени t,, на шину 11 приходит асинхронный сигнал, который поступает на импульсные входы устройств 3 и 6 и на С-вход триггера 10. На выходах устройств 3 и 6 формируются уровни напряжений, равные «Ui и и -мгновенным значениям напря жений Uj и Uz в .момент прихода асинхронного сигнала. Эти напряжения поддерживаются на инверсных входах компараторов 5 и 8 в качестве опорных. На выходах компараторов формируются импульсные нериодичесJ5 кие сигналы, моменты переключения которых определяются моментами пересечений напряжениями Ui и Ui уровней опорных напряжений Ut и Ui, зафиксированными на инверсных входах компараторов 5 и 8.

В момент прихода асинхронного сигнала

20 триггер 10 устанавливается в состояние, соответствующее логическому сигналу на его D-входе. Сигналы с выходов триггера 10 пропускают через коммутатор 12 на шину 13 сигнал с компаратора, переключае25 мого сиг налом с большей скоростью его изменения.

За счет того, что выходной импульс фор- .мируется из сигнала, имеющего большую скорость изменения в момент появления асин- 0 хронного сигнала, повыщается точность фазовой синхронизации.

Формула изобретения

Фазовый синхронизатор, содержащий эле5 мент задержки, вход которого соединен с щиной периодического сигнала, коммутатор, выполненный в виде двойного элемента И- ИЛИ, первые входы первого и второго конъюнкторов которого соединены соответственQ но с инверсным и прямым выходами триггера, выход - с выходной шиной, и шину асинхронного сигнала, которая соединена с С-входом триггера, отличающийся тем, что, с целью повышения точности фазовой синхронизации, в него введены первое и второе

5 устройства выделения модуля, первое и второе аналоговые запоминающие устройства, а также первый, второй и третий компараторы, приче.м аналоговый вход первого аналогового запоминающего устройства, вход первого устройства выделения модуля и прямой вход первого компаратора соединены с щиной периодического сигнала, выход первого аналогового запоминающего устройства соединен с инверсным входом первого компаратора, выход которого соединен с вто5 рым входом первого конъюнктора коммутатора, аналоговый вход второго аналогового запоминающего устройства, вход второго

1309279 34

устройства выделения модуля и прямой входвого и второго устройств выделения Mon.;ii;

второго компаратора соединены с выходомсоединены соответственно с прямым и с

элемента задержки, выход второго аналого-инверсным входами третьего компаратора,

вого запоминающего устройства соединен свыход которого соединен с D-входом тригинверсным входом второго компаратора, вы-гера, а импульсные входы аналоговых заиоход которого соединен с вторым входом вто-минающих устройств соединены с нжной

рого конъюнктора коммутатора, выходы пер-асинхронного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый синхронизатор | 1987 |

|

SU1413708A2 |

| Фазовый синхронизатор | 1985 |

|

SU1256176A1 |

| ЭЛЕКТРИЧЕСКИЙ ИМИТАТОР АККУМУЛЯТОРНОЙ БАТАРЕИ С ЗАЩИТОЙ ПО ТОКУ И НАПРЯЖЕНИЮ И УСТРОЙСТВО ЗАЩИТЫ ЭЛЕКТРИЧЕСКОГО ИМИТАТОРА АККУМУЛЯТОРНОЙ БАТАРЕИ | 2016 |

|

RU2635897C1 |

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1993 |

|

RU2056693C1 |

| Устройство для выделения признаков изображений | 1989 |

|

SU1661808A1 |

| Устройство для контроля величины мгновенного значения переменных аналоговых сигналов | 1985 |

|

SU1270711A1 |

| Фазометр | 1990 |

|

SU1797076A1 |

| Аналоговый интегратор | 1987 |

|

SU1425724A1 |

| Фазовый синхронизатор | 1987 |

|

SU1443147A1 |

| Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления | 1987 |

|

SU1494216A1 |

Изобретение может быть использовано в синтезатора.х частот. Цель изобретения -- повышение точности фазовой син.хронизанин периодического сигнала внсншим асинхронным сигналом. Устройство содержит элемент 2 задержки, триггер 10 и коммутатор 12, вынолненный на элементе И-ИЛИ. Введение аналог овых запоминающих устройств 3 и 6, устройств 4 и 7 выделения модуля и компараторов 5, 8 и 9 позволяет выходному и.мпульсу формироваться из сигнала, имеющего больщую скорость изменения в момент появления асинхронного сигнала. 1 ил. (Л со о со ts:) со

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| А | |||

| Кол ее о в Синтезаторы частот 4006103/24-21 10.01.86 07.05.87 | |||

| Бюл | |||

| № Ю | |||

| В | |||

| ПОРТСИГАР С ПРИСПОСОБЛЕНИЕМ ДЛЯ СКРУЧИВАНИЯ ПАПИРОС | 1922 |

|

SU621A1 |

| (теория и проектирование): Пер | |||

| с англ./Под ред | |||

| А | |||

| С | |||

| Галина | |||

| АЛ.: Связь, 1979, с | |||

| ФОРМА ДЛЯ БРИКЕТОВ | 1919 |

|

SU286A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для дискретного измерения фазы сигнала | 1980 |

|

SU881992A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Фазовый синхронизатор | 1985 |

|

SU1256176A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-07—Публикация

1986-01-10—Подача